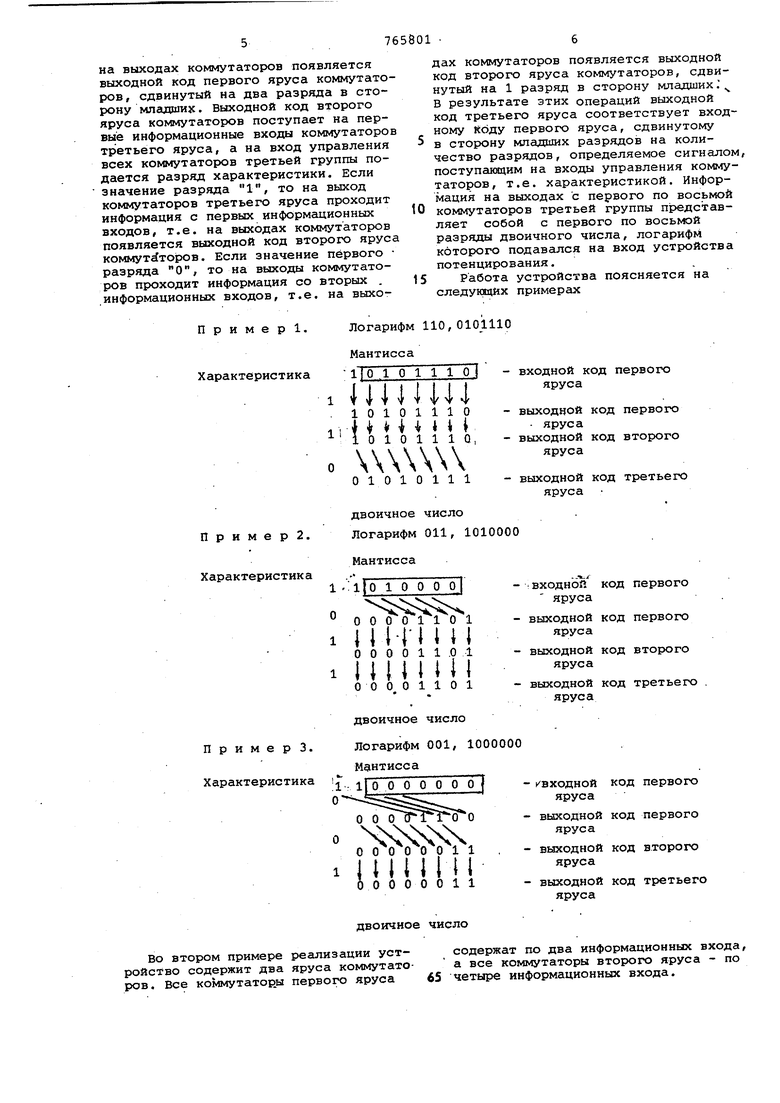

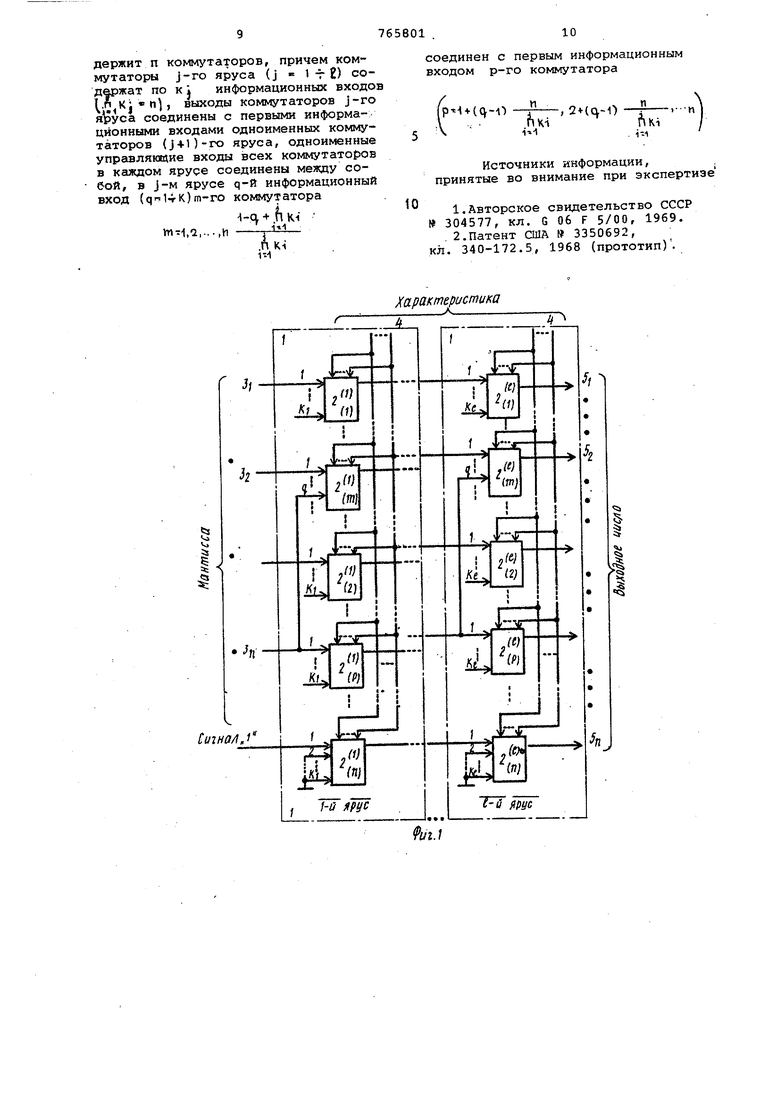

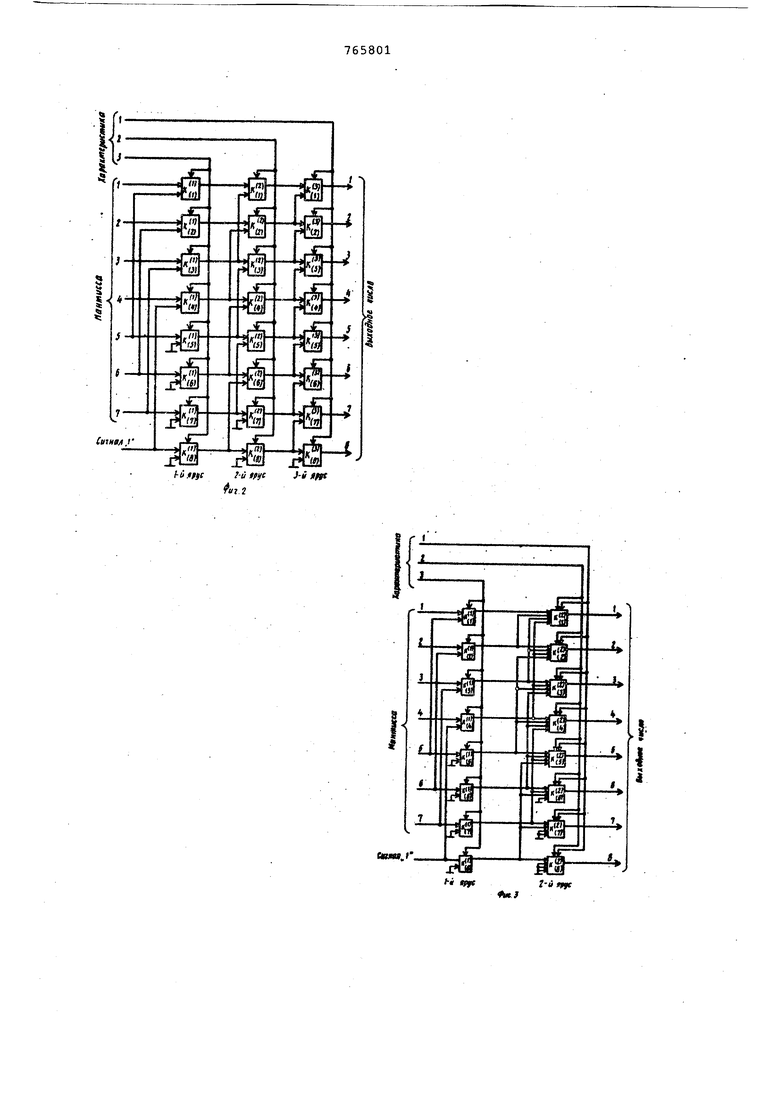

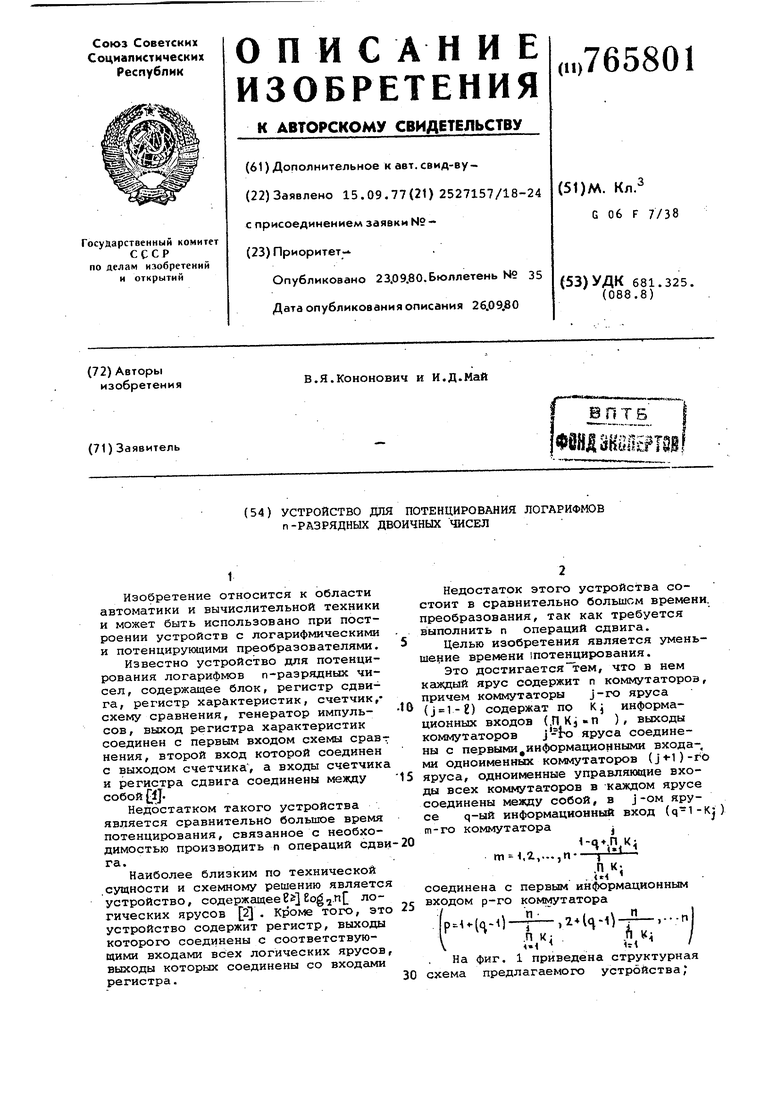

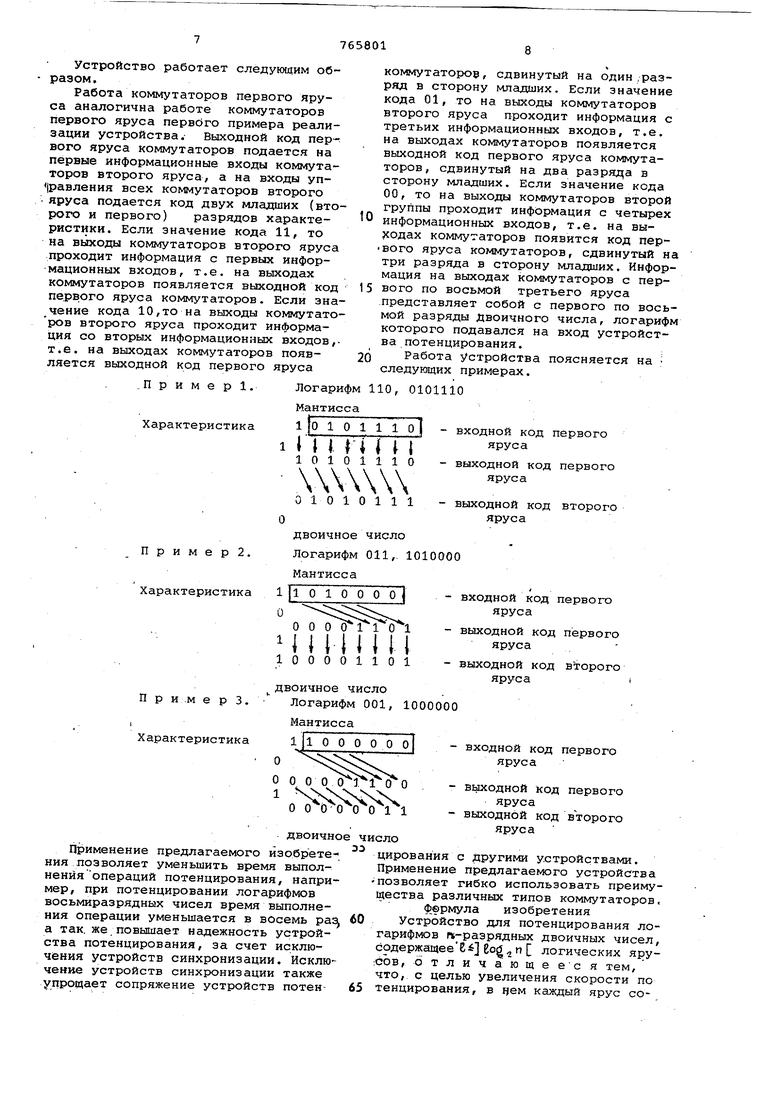

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении устройств с логариф 1ичесними и потенцирующими преобразователями. Известно устройство для потенцирования логарифмов п-разрядных чисел, содержсицее блок, регистр сдвига, регистр характеристик, счетчик,схему сравнения, генератор импульсов, выход регистра характеристик соединен с первым входом схемы сравнения, второй вход которой соединен с выходом счетчика , а входы счетчика и регистра сдвига соединены между собой lj. Недостатком такого устройства является сравнительно большое время потенцирования, связанное с необходимостью производить п операций сдви га. Наиболее близким по технической .сущности и схемному решению является устройство, содержащее8г ° гических ярусов 2 . Кроме того, это устройство содержит регистр, выходы которого соединены с соответствующими входами всех логических ярусов выходы которых соединены со входглш регистра. Недостаток этого устройства состоит в сравнительно большом времени, преобразования, так как требуется выполнить п операций сдвига. Целью изобретения является уменьшение времени шотенцирования. Это достигается тем, что в нем каждый ярус содержит п коммутаторов, причем коммутаторы j-ro яруса (j 1-2) содержат по Kj информационных входов (. ), выходы коммутаторов j-ro яруса соединены с первыми,информационными входа-, ми одноименных коко«1утаторов (j-H)-ro яруса, одноименные управляющие входы всех коммутаторов в каждом ярусе соединены между собой, в j-ом ярусе q-ый информационный вход () m-го коммутатора j bq+n.Ki mM.l,...,n- . , н соединена с первым информационным входом р-го коммутатора fp.u((il---, На фиг. 1 приведена структурная схема предлагаемого устройства, на фиг. 2 и 3 - примеры его -.реализации для потенцирования логарифмов 8-раэрядньк чисел, выполненные на коммутаторах различных типов/ на фиг. 4 и 5 - примеры реализации коммутаторов различных типов. Устройство содержит логические .; ярусы 1, состоящие из коммутаторов 2, информационные входы 3, управля щие входы 4 и выходы 5, Предлагаемое устройство содержит Cijeog nf логических ярусов, состо щих из п коммутаторов. Коммутаторы первого яруса содержат по к инфор- мационных входов, коммутаторы второ го содержат по К 2 информационных входов и т.д., коммутаторы -го яруса содержат.nOgKg информационны входов, при этом .П к j ,: п . Выходы ко мутаторов первого яруса соединены с i-ми информационными входами одноименных коммутаторов второго яруса выходы коммутаторов второго яруса соединены с 1-ми информационными входами одноименных коммутаторов третьего яруса и т.д. в первом ярусе коммутаторов q-й информационный вход 1-го, 2-го, 3-го.... ( I К / коммутаторов соединен с 1-м информа ционным входом (ьЦм1у.го,(2.(я-Ой- га, (i+()ro,...,n-ro коммутаторов соответственно. BQ вт ром ярусе коммутаторов q-й информационный вход 1-го, 2-го, 3-го... / 1-Я+1 ; г r- T li-го коммутаторов соедине с 1-м информационным входом (,.(,ro,(24qH)Jl-) ro,; (И-П1)го,...,п-.го коммутаторов соответственно. в j-м ярусе коммутаторов q-й информационный вход 1-го, 2-го, 3-го... , rt):. . . - й коммутаторов соединен с 1-м информационным входом . ,-,., i q-O-T Uro, ьчн-1)-1 .п « и ( коммутаторов .соответственно. На остальные информационные входы .коммутаторов подается сигнал логического О. Соответствующие входы управления всех коммутатордв каяадом ярусе соединены между собой Входное число, представляющее соб логарифм п-разрядного двоичного чиса, состоит из разрядов характеристики и п-1 разрядов мантиссы. Информация о 1,2,3,..п-1 разрядах мантиссы поступает на 1-е информационные входы 1-го, 2-го, 3-го (п-1)-го коммутаторов первого яруса соответственно. Информация о разрядах характерно- , тики поступает на входы управления коммутаторов, при этом информация о .старшем ( разряде характеристики поступает на первый ярус коммутаторов, а информация о младшем (1-м) разряде поступает на последний ярус. На 1-й информационный вход п-го коммутатора первого яруса поступает сигнал логической 1. в результате коммутации сигналов на выходах 1-го,2-го,3-го.. п-го коммутаторов последнего яруса появляется информация с 1,2,3..п разрядах двоичного числа, соответственно, логарифм которого поступил на вход устройства. Предлагаемое устройство может содержать три яруса коммутаторов по 8 коммутаторов на каждом (см.фиг.2) Все комг.1утаторы содержат по два информационных входа. Логарифм восьмиразрядного двоичного числа содержит : три разряда характеристики и семь разрядов мантиссы. Разряды мантиссы с первого по седьмой поступают на первые информационные входы с первого по седьмой кЪммутаторов первой группы соответственно, а на первый информационный вход восьмого коммутатора подается сигнал логической 1. На- вход управления всех коммутаторов первой группы подается cTapiший разряд характеристики. Если его значение равно 1, то на выходы коммутаторов первого яруса приходит информация с 1-х информационных входов, т.е. на выходах коммутаторов появляется входной код. Если значение старшего разряда характеристики равно О, то на выходы коммутаторов происходит информация со вторых информационных входов, т.е. на выходах коммутаторов появляется -выходной код/ представляющий собой входной код, сдвинутый на четыре разряда в сторону младших Выходной код первого яруса коммутаторов поступает на первые информационные входы коммутато.ров второго яруса,а на вход управления всех коммутаторов второго яруса подается второй разряд характеристики. Если его значение равно 1, то на выходы коммутаторов второго яруса проходит информация с первых информационных входов, т.е. на выходах коммутаторов появляется выходной код первого коммутаторов. Если значение второго разряда О, то на выходы коммутаторов проходит информация со вторых информационных входов/ т.е.

на выходах коммутаторов появляется выходной код первого яруса коммутаторов, сдвинутый на два разряда в сторону младших. Выходной код второго яруса коммутаторов поступает на первые информационные входы коммутаторов третьего яруса, а на вход управления всех коммутаторов третьей группы подается разряд характеристики. Если значение разряда 1, то на выход коммутаторов третьего яруса проходит информация с первых информационных входов, т.е. на выходах коммутаторов появляется выходной код второго яруса коммутаторов. Если значение первого разряда О, то на выходы коммутаторов проходит информация со вторых . информационных входов, т.е. на выхоПример. Характеристика

1 i О П р и м е р 2. Характеристика 1 П l-ti i U 1 П 1 П i t I П р и м е р 3. Характеристика :i г 1|о о о о о о oJ о Ч 1 П t t 1 I 11 во втором примере реализации устройство содержит два яруса коммутаторов. Все коммутаторы первого яруса 65

дах коммутаторов появляется выходной код вторюго яруса коммутаторов, сдвинутый на 1 разряд в сторону младших. В результате этих операций выходной код третьего яруса соответствует входному КОДУ первого яруса, сдвинутому в сторону младших разрядов на количество разрядов, определяемое сигналом, поступсосяцим на входы управления коммутаторов, т.е. характеристикой. Информация на выходах с первого по восьмой коммутаторов третьей группы представляет собой с первого по восьмой разряды двоичного числа, логарифм которого подавался на вход устройства потенцирования.

5

Работа устройства поясняется на следующих примерах

110

- входной код первого

-выходной код первого

яруса

-выходной код второго

яруса

- выходной код третьего яруса двоичное число Логарифм 011, 1010000 Мантисса 0100001 00001101О О О О 1 1 .0 1 00001101двоичное число Логарифм 001, 1000 Мантисса 000 СГ1 о о 000001 1 00 000011

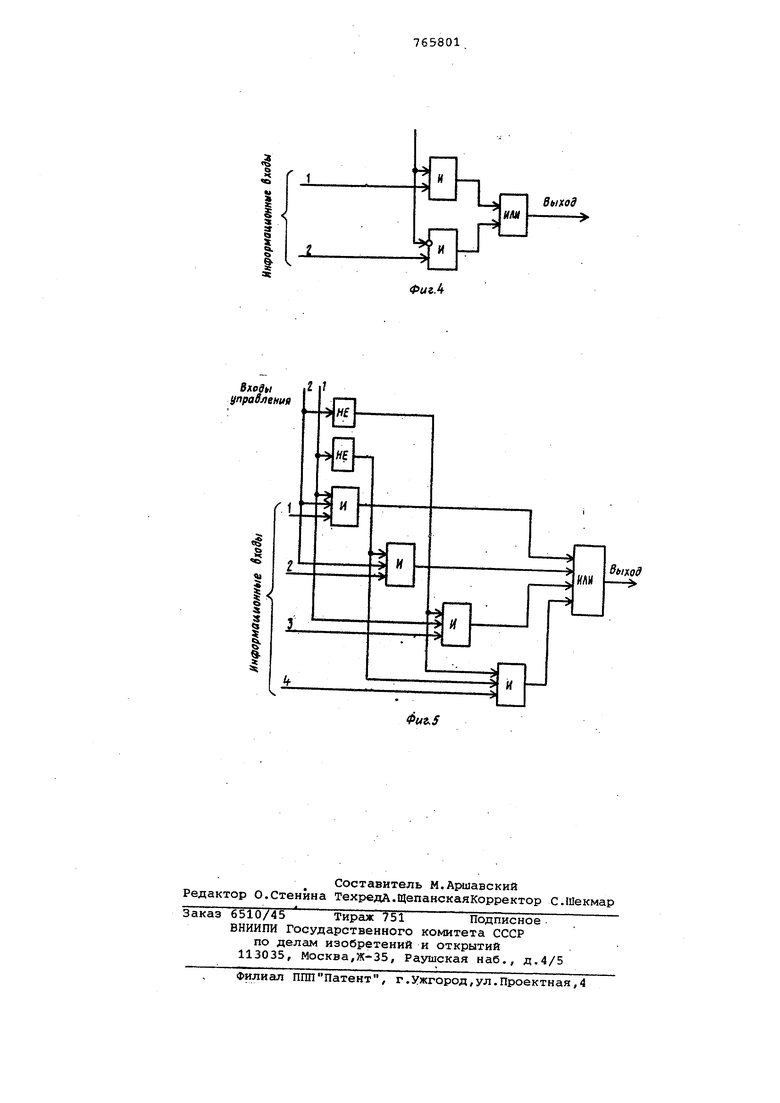

двоичное число (ВХОДНОЙ код первого яруса выходной код первого ° выходной код второго яруса выходной код третьего . яруса -ивходной код первого яруса -выходной код первого яруса -выходной код второго яруса -выходной код третьего яруса содержат по два информационных входа, а все коммутаторы второго яруса - по четыре информационных входа.

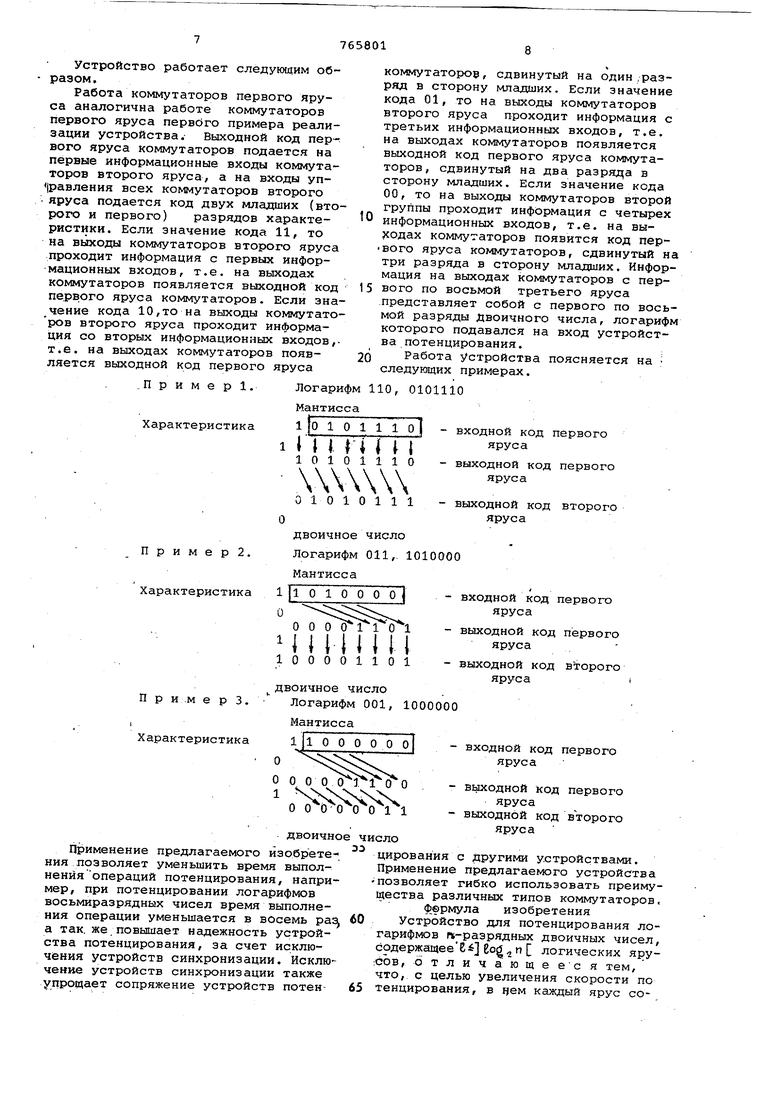

Устройство работает следующим образом.

Работа коммутаторов первого яруса аналогична работе коммутаторов первого яруса первбго примера реализации устройства. Выходной код пер вого яруса коммутаторов подается на первые информационные входы коммутаторов второго яруса, а на входы управления всех коммутаторов второго яруса подается код двух младших (второго и первого) разрядов характеристики. Если значение кода 11, то на выходы коммутаторов второго яруса проходит информация с первых информационных входов, т.е. на выходах коммутаторов появляется выходной код первого яруса коммутаторов. Если значение кода 10,то на выходы коммутаторов второго яруса проходит информация со вторых информационных входов,т.е. на выходах коммутаторов появляется выходной код первого яруса

Пример.

Логарифм 110, 0101110

Мантисса 1

Характеристика

1 I И I I I

10101110

01010111

двоичное число Логарифм 011,. 1010000

П р и м е р 2.

Мантисса

коммутаторов, сдвинутый на один/разряд в сторону младших. Если значение кода 01, то на выходы коммутаторов второго яруса проходит информация с третьих информационных входов, т.е. на выходах коммутаторов появляется выходной код первого яруса коммутаторов, сдвинутый на два разря;с а в сторону младших. Если значение кода 00, то на выходы коммутаторов второй группы проходит информация с четырех

информационных входов, т.е. на коммутаторов появится код первого яруса коммутаторов, сдвинутый на три разряда в сторону младших. Информация на выходах коммутаторов с первого по восьмой третьего яруса

представляет собой с первого по восьмой разряды Двоичного числа, логарифм которого подавался на вход устройства потенцирования.

Q Работа устройства поясняется на следующих примерах.

входной код первого яруса

выходной код первого яруса

выходной код

второго яруса Характеристика двоично Применение предлагаемого изобретения позволяет уменьшить время выполнения операций потенцирования, например, при потенцировании логарифмов восьмиразрядных чисел время выполнения операции уменьшается в восемь ра а так же/повышает надежность устройства потенцирования, за счет исключения устройств синхронизации. Исключение устройств синхронизации также упрощает сопряжение устрюйств потен-входной код первого -выходной код первого -выходной код второго сло цирования с другими устройствами. Применение предлагаемого устройства Позволяет гибко использовать преимущества различных типов коммутаторов. Фермула изобретения Устройство для потенцирования логарифмов «-разрядных двоичных чисел, содержащееЕ i бо,, и логических яру:СОВ, отличающеес я тем, что, с целью увеличения скорости по тенцирования, в «ем каждый ярус содержит п коммутаторов, причем коммутаторы j-ro яруса (j - 1 т Е) содержат по к 1 информационных входо .п к:«п), выходы коммутаторов j-ro соединены с первыми информационными входами одноименных коммутаторов (j4l)-ro яруса, одноименные управляющие входы всех коммутаторов в каждом яруре соединены между собой, в J-M ярусе q-й информационный вход (qn14K)m-ro коммутатора

i-cv + .flKi

WTl,7,...,H j-liu

.n Ki

соединен с первым информационным входом р-го коммутатора

Источники информации, . принятые во внимание при экспертизе

1.Авторское свидетельство СССР 304577, кл. G 06 Г 5/00, 1969.

. 2.Патент США 3350692, кл. 340-172.5, 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования двоичных чисел | 1977 |

|

SU717760A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| Цифровое логарифмирующее устройство | 1987 |

|

SU1448345A1 |

| Устройство для вычисления логарифмов чисел | 1981 |

|

SU972504A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

| Устройство для логарифмирования | 1980 |

|

SU959072A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для потенцирования логарифмов по основанию два | 1982 |

|

SU1020819A2 |

| Устройство для вычисления логарифмов | 1988 |

|

SU1564618A1 |

}(арактеристика

.ta.

I

ВхоЗи управления

8ьиод

Авторы

Даты

1980-09-23—Публикация

1977-09-15—Подача