Изобретение относится к вычислительной технике, в частности к устройствам для выполнения математических операций в двоичном представлении, и может быть применено в качестве спецпроцессора в комплексе с вычислительной машиной для вычисления

натурального логарифма чисел0

Цель изобретения - повышение точности вычисления функции.

s

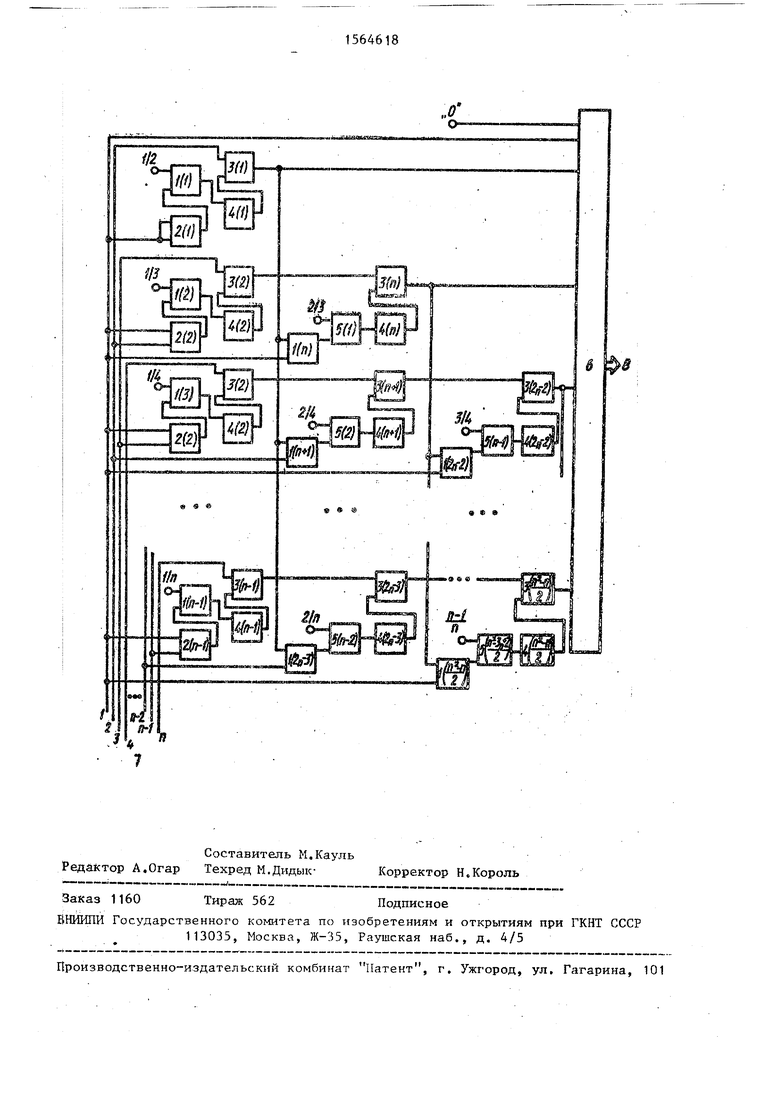

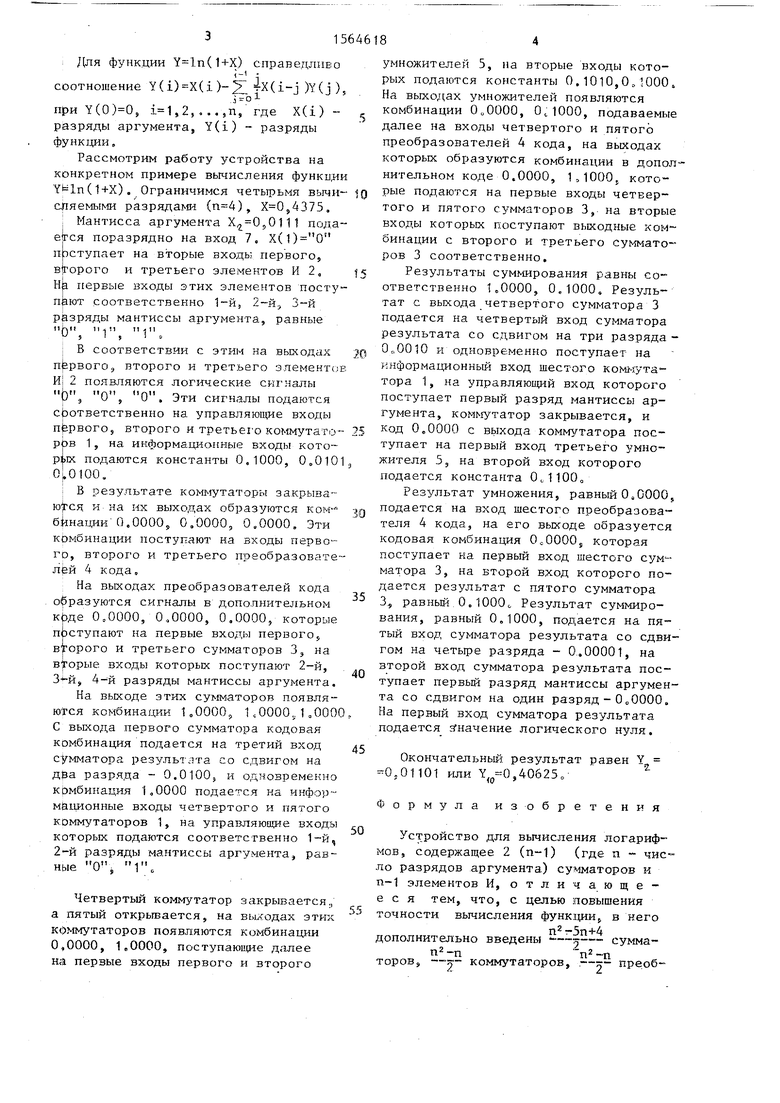

На чертеже представлена структурная схема устройства для вычисления логарифмов о

Устройство содержит -к- (где п число разрядов аргумента) коммутатоп -п

ров 1, п-1 элементов И 2, я- сумматоров 3, --к- преобразователей 4

п2-Зп+2 кода, -,умножителей 5, сумматор

6 результата, вход 7 аргумента и выход 8 о

Устройство работает следующим образом.

с

s

Для функции (1+X) справедливо

- i

соотношение Y(i)X(i )X (i-j )Y(j)s

j oJпри Y(0)0, ,2,...,n, где X(i)- разряды аргумента, Y(i) - разряды функции.

Рассмотрим работу устройства на конкретном примере вычисления функции (1+X). Ограничимся четырьмя вычисляемыми разрядами (), Х 054375.

Мантисса аргумента Х7,050111 подается поразрядно на вход 7. Х(1)0 поступает на вторые входы первого, второго и третьего элементов И 2, На первые входы этих элементов поступают соответственно 1-й, 2-й., 3-й разряды мантиссы аргумента, равные

tlKll II , 1 И 4 11 U 5 I , i о

В соответствии с этим на выходах первого, второго и третьего элементов И 2 появляются логические сигналы Ь, О, О. Эти сигналы подаются соответственно на управляющие входы первого, второго и третьего коммутагорЬв 1, на информационные входы кото- рьк подаются константы 0.1000, 0.0Ю 0.0100.

В результате коммутаторы закрыва- и на их выходах образуются ком- б нации 0.0000, 0.0000, 0,0000. Эти комбинации поступают на входы первого, второго и третьего преобразователей 4 кода

На выходах преобразователей кода образуются сигналы в дополнительном кЬде 0,0000, 0,0000, 0.0000, которые поступают на первые входы первого,, второго и третьего сумматоров 3, на вторые входы которых поступают 2-й, 3+-Й, 4-й разряды мантиссы аргумента. На выходе этих сумматоров появляются комбинации 1.0000, К 0000JаООО С выхода первого сумматора кодовая комбинация подается на третий вход сумматора результата со сдвигом на дЈа разряда - O.OIOO, и одновременно крмбинация 1.0000 подаемся на чнфэр- маиионные входы четвертого и пятого коммутаторов 1, на управляющие входы которых подаются соответственно 1-й, 2-й разряды мантиссы аргумента, рав ные О, 1.

Четвертый коммутатор закрывается., а пятый открывается, на вь1ходах этих коммутаторов появляются комбинации 0,0000, 1.0000, поступающие далее на первые входы первого и второго

0

5

0

5

O

5

0

5

0

5

умножителей 5, на вторые входы которых подаются константы 0.1010,0.000S На выходах умножителей появляются комбинации 0„0000, 0..1000, подаваемые далее на входы четвертого и пятого преобразователей 4 кода, на выходах которых образуются комбинации в дополнительном коде 0.0000, 1,1000, которые подаются на первые входы четвертого и пятого сумматоров 3, на вторые входы которых поступают выходные комбинации с второго и третьего сумматоров 3 соответственно.

Результаты суммирования равны соответственно 1.0000, 0,1000. Результат с выхода четвертого сумматора 3 подается на четвертый вход сумматора результата со сдвигом на три разряда - 0,0010 и одновременно поступает на информационный вход шестого коммутатора 1, на управляющий вход которого поступает первый разряд мантиссы аргумента, коммутатор закрывается, и код 0.0000 с выхода коммутатора поступает на первый вход третьего умножителя 5Э на второй вход которого подается константа 0С1100„

Результат умножения, равный 0 а 0000 s подается на вход шестого преобразователя 4 кода, на его выходе образуется кодовая комбинация , которая поступает ка первый вход шестого матора 3, на второй вход которого подается результат с пятого сумматора 3„ равный 0.1000,, Результат суммирования, равный 0.1000, подается на пятый вход сумматора результата со сдвигом на четыре разряда - 0.00001, на второй вход сумматора результата поступает первый разряд мантиссы аргумента со сдвигом на один разряд - 0„0000. На первый вход сумматора результата подается значение логического нуля.

Окончательный результат равен Y 0,01101 или ,40625«,

Формула изобретения

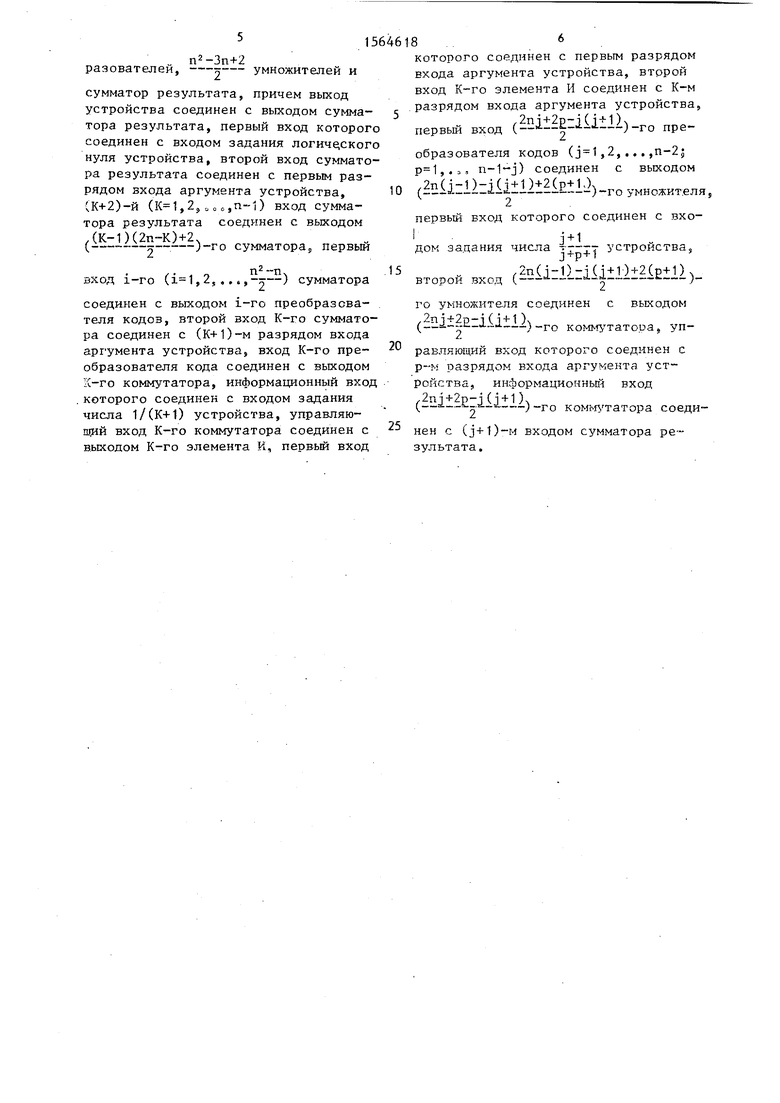

Устройство для вычисления логарифмов, содержащее 2 (п-1) (где п - число разрядов аргумента) сумматоров и п-1 элементов И, отличающееся тем, что, с целью повышения точности вычисления функции, в него

п2-5п+4 дополнительно введены --j-- суммап2 -п

торов5 --я™ коммутаторов, -х- преобразователей,

n2-3n+2

умножителей и

сумматор результата, причем выход устройства соединен с выходом сумматора результата, первый вход которого соединен с входом задания логического нуля устройства, второй вход сумматора результата соединен с первым разрядом входа аргумента устройства, чК+2)-й (,29„„0,п-1) вход сумматора результата соединен с выходом

которого соединен с первым разрядом входа аргумента устройства, второй вход К-го элемента И соединен с К-м разрядом входа аргумента устройства

5,2nj+2p-j(j+1)4

первый вход (--А-2 --)-го преобразователя кодов (,2,...,п-2; ,.эа n-1-j) соединен с выходом

10 (2n((i±1)l2(ЈilL)bro умножител

первый вход которого соединен с вхо,(К-1)(2п-К)+2.„ IJ-H

(. j-ro сумматора, первый дом зацания числа т устройства.

46186

которого соединен с первым разрядом входа аргумента устройства, второй вход К-го элемента И соединен с К-м разрядом входа аргумента устройства,,

5,2nj+2p-j(j+1)4

первый вход (--А-2 --)-го преобразователя кодов (,2,...,п-2; ,.эа n-1-j) соединен с выходом

10 (2n((i±1)l2(ЈilL)bro умножителя

первый вход которого соединен с вхо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления гиперболических функций у = @ и у = с @ | 1990 |

|

SU1735845A1 |

| Устройство для вычисления функций синуса и косинуса | 1991 |

|

SU1827673A1 |

| Устройство для вычисления функций @ = @ , @ = х @ | 1989 |

|

SU1674113A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления функции @ | 1988 |

|

SU1550513A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1136155A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Преобразователь комплексных сигналов | 1983 |

|

SU1104525A1 |

Изобретение относится к вычислительной технике, в частности к устройствам для выполнения математических операций в двоичном представлении, и может быть применено в качестве спецпроцессора в комплексе с вычислительной машиной для вычисления натурального логарифма чисел. Цель изобретения - повышение точности вычисления функции. Поставленная цель достигается тем, что устройство содержит N2-N/2 (где N - число разрядов аргумента) коммутаторов 1, N-1 элементов И 2, N2-N/2 сумматоров 3, N2-N/2 преобразователей кода 4, N2-3N+2/2 умножителей 5, сумматор результата 6, вход аргумента 7, выход 8. Работа устройства основана на том что для функции Y-LN (1+X) справедливо соотношение Y(I)=X(I) - Σ J/I X(IJ) Y(J), где X(I) - разряды аргумента, Y(I) - разряды функции. 1 ил.

п. -и вход 1-го (, 2, ...,) сумматора

соединен с выходом 1-го преобразователя кодов, второй вход К-го сумматора соединен с (К+1)-м разрядом входа аргумента устройства, вход К-го преобразователя кода соединен с выходом С-го коммутатора, информационный вход которого соединен с входом задания числа 1/(К+1) устройства, управляющий вход К-го коммутатора соединен с выходом К-го элемента К, первый вход

,2n(i-1)-Uj + l)+2(p+lK

ВТОРОЙ ВХОД ( - i- Z- )го умножителя соединен с выходом

,2nj+2p-j(j + l)

(-i---i-J.-.J.)-го комкутатооа, управляющий вход которого соединен с р-м разрядом входа аргумента устройства, информационный вход

(2nii2 E:iliil))r

2 /-го коммутатора соединен с (j+1)-M входом сумматора результата.

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Матричный вычислитель логарифмов | 1981 |

|

SU1012251A1 |

Авторы

Даты

1990-05-15—Публикация

1988-04-04—Подача