(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РЕГИСТРА СДВИГА

к шине управления записью информации, один из входов элемента ИЛИ соединен с выходом первого сумматора, а другой вход- с другой информационной шиной, первый вход первого сумматора подключен к одному из выходов регистра сдвига, , второй вход первого сумматора соединен с одной из шин управления сдвигом.

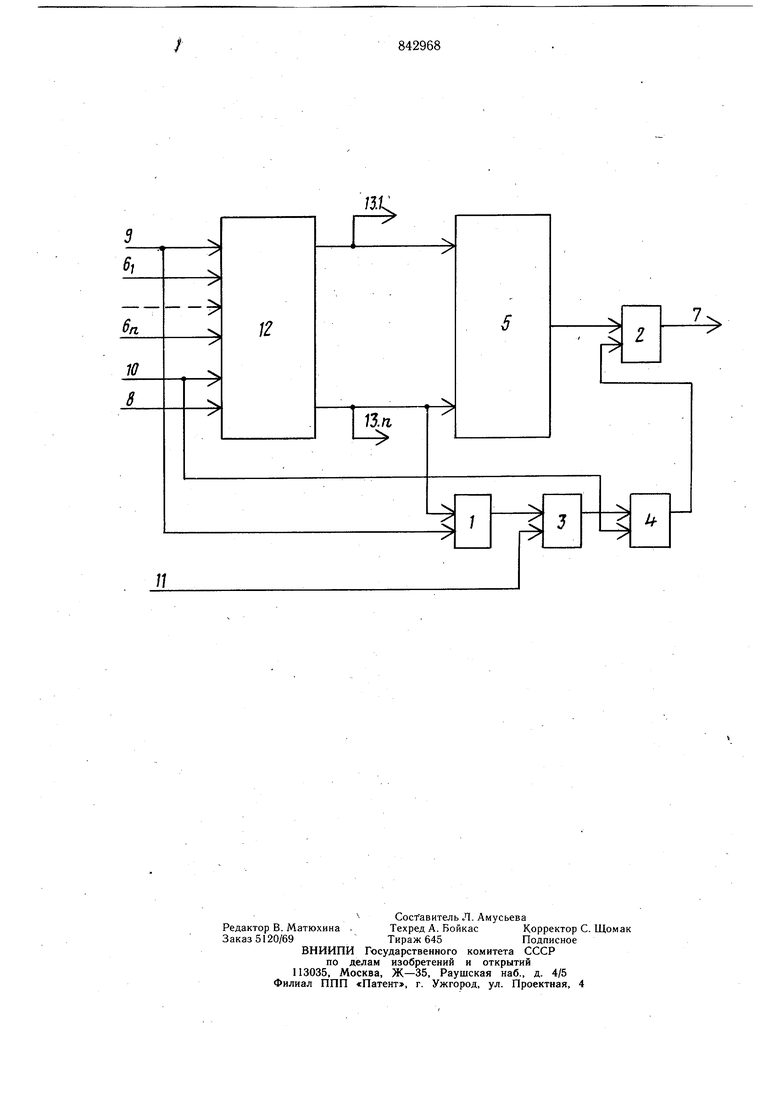

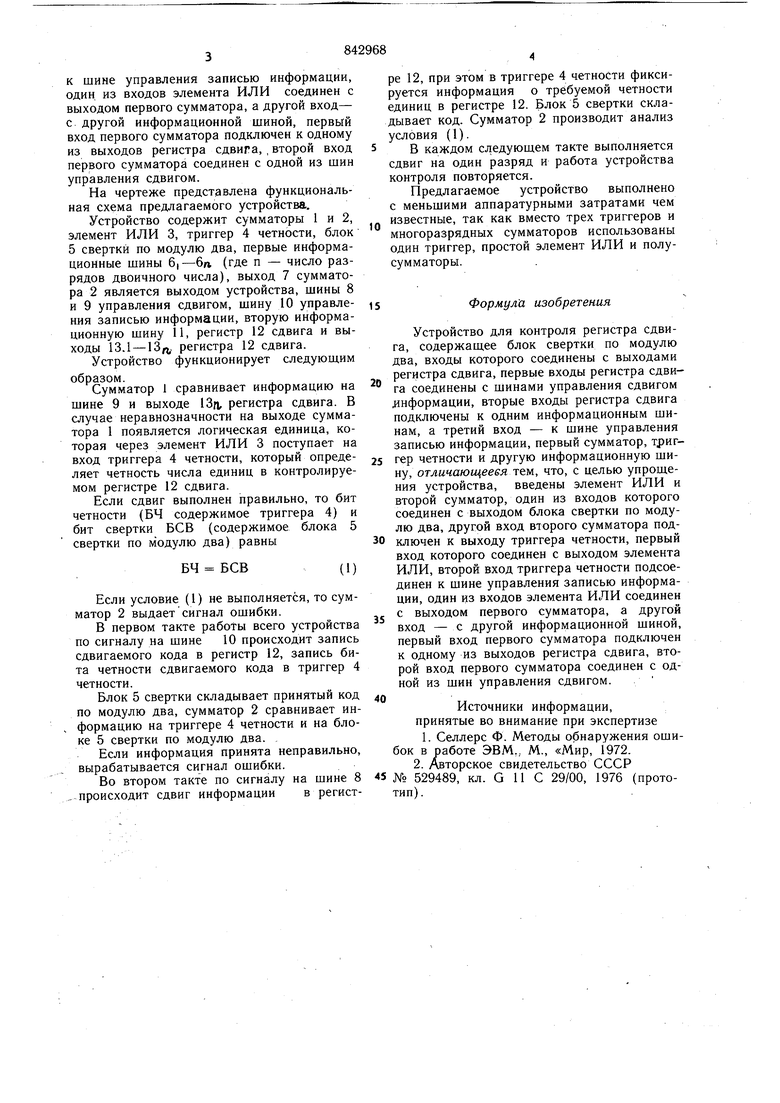

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит сумматоры 1 и 2, элемент ИЛИ 3, триггер 4 четности, блок 5 свертки по модулю два, первые информационные шины 6,-6а (где п - число разрядов двоичного числа), выход 7 сумматора 2 является выходом устройства, шины 8 и 9 управления сдвигом, шину 10 управления записью информации, вторую информационную шину 11, регистр 12 сдвига и выходы 13.1 -13, регистра 12 сдвига.

Устройство функционирует следующим

образом.

Сумматор 1 сравнивает информацию на

шине 9 и выходе 13п, регистра сдвига. В случае неравнозначности на выходе сумматора 1 появляется логическая единица, которая через элемент ИЛИ 3 поступает на вход триггера 4 четности, который определяет четность числа единиц в контролируемом регистре 12 сдвига.

Если сдвиг выполнен правильно, то бит четности (БЧ содержимое триггера 4) и бит свертки БСВ (содержимое блока 5 свертки по модулю два) равны

БЧ БСВ

Если условие (1) не выполняется, то сумматор 2 выдает сигнал ошибки.

В первом такте работы всего устройства по сигналу на шине 10 происходит запись сдвигаемого кода в регистр 12, запись бита четности сдвигаемого кода в триггер 4 четности.

Блок 5 свертки складывает принятый код по модулю два, сумматор 2 сравнивает информацию на триггере 4 четности и на блоке 5 свертки по модулю два. ,

Если информация принята неправильно, вырабатывается сигнал ошибки.

Во втором такте по сигналу на шине 8 происходит сдвиг информации в регистре 12, при этом в триггере 4 четности фиксируется информация о требуемой четности единиц в регистре 12. БЛОК 5 свертки складывает код. Сумматор 2 производит анализ условия (1).

В каждом следующем такте выполняется сдвиг на один разряд и работа устройства контроля повторяется.

Предлагаемое устройство выполнено с меньшими аппаратурными затратами чем

известные, так как вместо трех триггеров и многоразрядных сумматоров использованы один триггер, простой элемент ИЛИ и полусумматоры.

Формула изобретения

Устройство для контроля регистра сдвига, содержащее блок свертки по модулю два, входы которого соединены с выходами регистра сдвига, первые входы регистра сдвига соединены с шинами управления сдвигом информации, вторые входы регистра сдвига подключены к одним информационным шинам, а третий вход - к шине управления записью информации, первый сумматор, триггер четности и другую информационную mviку, отличающеебят&ы, что, с целью упрощения устройства, введены элемент ИЛИ и второй сумматор, один из входов которого соединен с выходом блока свертки по модулю два, другой вход второго сумматора под0 ключей к выходу триггера четности, первый вход которого соединен с выходом элемента ИЛИ, второй вход триггера четности подсоединен к шине управления записью информации, один из входов элемента ИЛИ соединен

, с выходом первого сумматора, а другой вход - с другой информационной шиной, первый вход первого сумматора подключен к одному из выходов регистра сдвига, второй вход первого сумматора соединен с одной из шин управления сдвигом.

Источники информации, принятые во внимание при экспертизе 1. Селлерс Ф. Методы обнаружения ощибок в работе ЭВМ,, М., «Мир, 1972. 2. Авторское свидетельство СССР № 529489, кл. G 11 С 29/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сдвига со встро-ЕННыМ КОНТРОлЕМ | 1979 |

|

SU809386A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1129655A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| ДВУХУРОВНЕВОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК | 1992 |

|

RU2037891C1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Запоминающее устройство с исправлением многократных ошибок | 1985 |

|

SU1300568A1 |

Авторы

Даты

1981-06-30—Публикация

1979-10-03—Подача