четности соединен с вторыми входами коммутаторов сверток адреса и данных, первым информационным входом коммутатора сигналов ошибки, выход второго триггера четности соединен с третьими входами коммутаторов сверток ад-. реса.и данных и с вторым информационным входом коммутатора сигналов ошибки, входы первого и второго операндов микропроцессора соединены соответственно с четвертыми и пятыми входами коммутаторов сверток адреса и данных, шестые входы которых соединены с шкной логического нуля, вход переноса микропроцессора соединен с первым входом элемента Н-НЕ, выход переноса арифметико-логического блока соединен с вторым входом элемента И-НЕ выxo которого соединей с третьим информационным входом коммутатора сигналов ошибки, выходы промежуточных переносо арифметико-логического блока соединены с соответствующими входами элемен;тами И-НЕ, вход сигналов контроля микропроцессора соединен с четвертым информационным входом коммутатора сигналов ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ И ЧЕРЕДУЮЩИМСЯ ОБСЛУЖИВАНИЕМ НЕСКОЛЬКИХ КОМАНДНЫХ ПОТОКОВ | 1995 |

|

RU2099780C1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

МИКРОПРОЦЕССОР С KOHTPOJDSM, содержащий арифметико-логический блок, блок микропрогра Ф4Ного управления, первый и второй коммутаторы операндов, блок синхронизации, блок регистров регистр данных, регистр адреса, свертки по ырдолза два данных н адреса, первый и второй триггеры четности, причём выходы регистров данных и адреса соединены соответственно с первыми входами сверток по модрлю два данных и адреса, выходы которых соединены соответственно с информационными входами первого, и второго триггеров четности и выходными шинами адреса и данных микропро- . цессора, первый управлякяций выход блока микропрограммного управления соединен с входами настройки арифметико-логического блока, с управляюцими входами первого и второго кс 4мутаторов операндов, блока регистров, регистра адреса и регистра данных, первш выход блока синхронизации соединен с входом синзсронизации блока регистров, регистра данных и регистра адреса, второй и третий выходы блока синхронизации соединены соответственно с входами синхронизации первого и второго триггеров четности, выходы регистра данных соединены с первыми входами первого и второго коммутаторов операндов, входы первого и второго операндов микропроцессоров соединены с вторыми входами первого и второго коммутаторов операндов, выход блока регистров соединен с третьими .входами первого и второго коммутаторов операндов, выходы которых соединены с входами первого и второго операндов арифметико-логического блока соответственно, вход переноса микропроцессора соединен с входом переноса арифметико-логического блока, выход переноса которого соединен с выходом переноса микропроцессора, информационный выход арифметико-логического (О блока соединен с информационным входом регистра адреса, регистра данных и блока регистров, о тл и ч a ю 1д и и с я тем, что, с целью сокршцения объема контрольного оборудования при выполнении логических операций, введены коммутатор свертки адреса, коммутатор свертки данных, элемент И-НЕ и коьвлутатор сигналов ошибки, причем второй управляющий выход блока ф микропрограммного управления соединен с управляющими входами коммутаторов сверток адреса и данных, a третий 00 управляющий выход блока микропрограм00 много управления соединен с входом блока синхронизации, четвертый выход Опока синхронизации соединен с первыми управляющими входами кокмутатора сигналов ошибки, выход которого соединен с первым входом блока микро программного управления и является, контрольньал выходом йикропроцессОра, ,вхсф1Ы наращивания сверток адреса и данных микропроцессор соединены соответственно с первыми входами коммутаторов сверток адреса и данных, выходы которых соединены соответственно с вторыми входами сверток адреса и данных, выход первого триггера

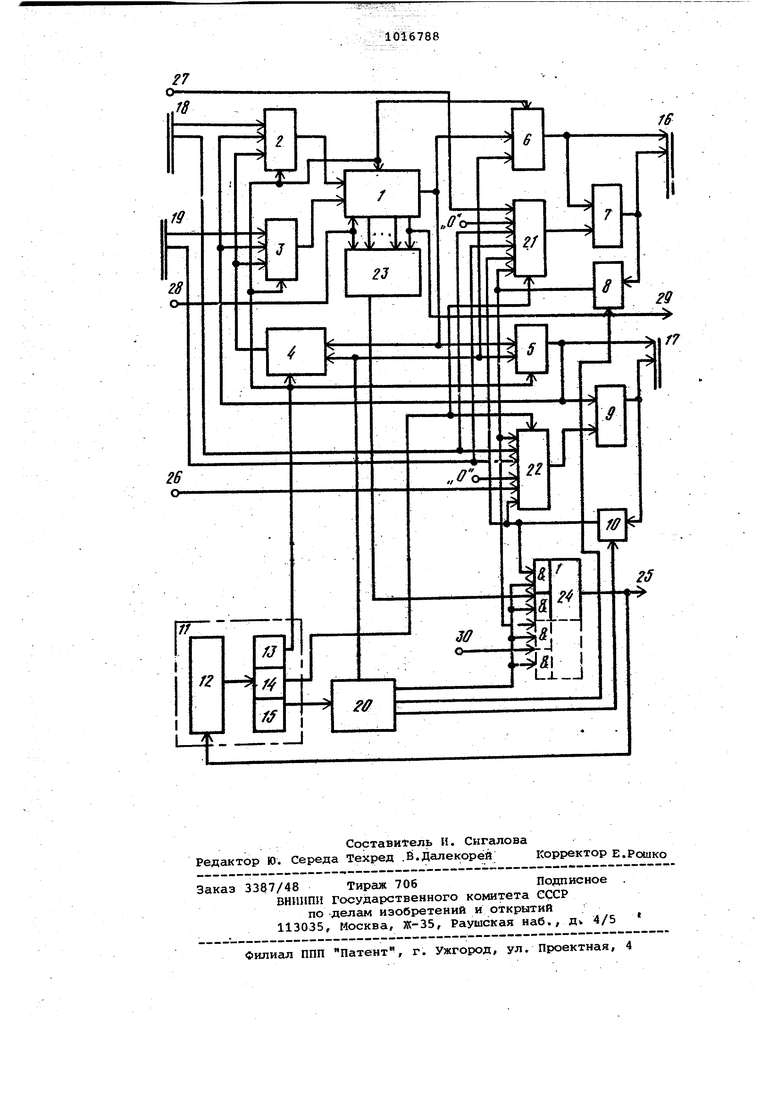

Изобретение относится к цифровой вычислительной технике и дискретной автоматике и может быть использовано в устройствах обработки двойной информации с контролем. Известны микропроцессоры с оперативным контролем, при котором возникающие сбои (отказы) обнаруживаются в неверном цикле работы микропроцессора или с задержкой на несколько циклов, определяемой конкретной схемой контроля С13 f 2 3 и Сз. В известном микропроцессоре контроль выполнения микропрограмм осуществляется подсчетом числа микрокоманд в конкретнойчасти алгоритма исравнением этого числа с зарание подсчитан ным. Недостатками такого контроля является отсутствие контроля операций, неконкретность определения сбившегос узла, необходимость хранения подсчитанного заранее числа микрокоманд для любых выполняемых микропрограмм. К устройствам с оперативньом аппаратным контролем относятся также мик ропроцессоры с контролем по модулю. Параллельно с операциями в основном АУ производятся операции над контрольными кодами операндов в контроль ном АУ меньшей разрядности по специгшьным алгоритмам. После выполнения операции в основном АУ результат сво рачивают по контрольному модулю и по лученный код свертки сравнивают с ре зультатом операции в контрольном АУ. Недостатками таких устройств являются наличие дополнительного контрольного АУ, а также большая относи тельная сложность схем сверток по мо дулю. . Наиболее близким .по технической сущности к предлагаёмо му является микропроцессор.содержащий арифметико логический блок. Для выполнения ариф метических и логических операций микропроцессор содержит два коммутатора операндов, регистр Для записи результата (данных) со схемой свертки по модулю два, регистр адреса со схемой свертки по модулю два, регистр для хранения результатов сверток по модулю два (контрольных разрядов), схему контроля арифметико-логического блока, блок микропрограммного управления. Арифметико-логический блок состоит из двух частей, одна из которых формирует результат операции в прямом коде, а вторая - в обратном. Схема контроля арифметико-логического блока сравнивает результаты, полученные от обеих частей арифметико-логического блока, и в случае несовпадения вырабатывает сигнал сбоя. При выдаче результата из арифметико-логического блока схема свертки по модулю два вьфабатьгаает дополнительный контрольный разряд результата, который вместе с информационными разрядами передается в вькодную шину. Регистр результата принимает результат операции с выходной шины арифметикологического блока вместе с контрольным разрядом. С помснаью свертки по модОЛЮ два, подключенной к выходу регистра результата, проверяется правильность передачи информации между арифметико-логическим блоком и реги- , стром результата. Таким образом, операции арифметико-логического блока контролируются методом дубления, а межрегистровые передачи контролируются по модулю два 4.- Недостатком известного устройства является большой объем оборудования, используемый для контроля. Так для получения в арифметико-логическом блоке инверсного значения результата каждой операции во второй половине арифметико-логического блока необхоцимы в общем случае микрооперации, этличающиеся от микроопераций, управ 1ЯЮ1ДИХ первой половиной арифметикологического блока. Следовательно, ли бр память микрокоманд должна содержать дополнительные поля, что увеличивает ее объем, либо необходимы дополнительные перекодирующие схемы. В то же время имеющиеся схемы свертки не используются для контроля собстзенно арифметико-логического блока. Цель изобретения - сокращение объ ема контрольного оборудования при включении логических операций. Поставленная цель достигается тем что в микропроцессор с контролем, со держащий арифметико-логический блок, блок микропрограммного управления, первый и второй коммутаторы операндов, блок синхронизации, блок регист ров, регистр данных, регистр адреса, свертки по модулю два данных и адреса, первый и второй триггеры четности, причем выходы регистров данных 1И адреса соединены соответственно с первыми входами сверток по модулю два данных и адреса, выходы которых соединены соответственно с информационными входами первого и второго триггеров четности и выходными ыииам адреса и данных микропроцессора, пер вый управляющий выход блока микропрограммного управления соединен с входами настройки арифметико-логичес кого блока, с управляющими входами первого и второго коммутаторов операндов, блока регистров, регистра адреса и регистра данных, первый выход блока синхронизации соединен с входом синхронизации блока регистров регистра данных и регистра адреса, второй и третий выходы блока синхронизации соединены соответственно с входами синхронизации первого и второго триггеров четности, выходы регистра данных соединены с первыми входами первого и второго коммутаторов операндов, входы первого и второ го операндов микропроцессоров соединены с вторыми входами первого и вто рого коммутаторов операндов, выход блока регистров соединен с третьими входами первого и второго коммутаторов операндов, выходы которых соединены с входами первого и второго операндов арифметико-логического бло ка соответственно, вход переноса мик ропроцессора соединен с входом переноса арифметико-логического блока, выход переноса которого соединен с выходом переноса микропоцессора, информационный выход арифметико-логического, блока соединен с информацион ным входом регистра гщреса, регистра :данных и блока регистров, введены коммутатор свертки адреса, коммутатор свертки данных, элемент И-НЕ и Коммутатор сигналов ошибки, причем второй управляющий выход ьлока микропрограммного управления соединен с управляющими входами коммутаторов сверток адреса и данных, а третий управляющий выход блока микропрограммного управления соединен с входом блока синхронизации, четвертый выход блока синхронизации соединен с первыми управляющими входами коммутатора сигналов ошибки, выход которюго соединён с первым входом блока микропрограммного управления и является контрольным выходом микропроцессора, входы наращивания сверток адреса и данных микропроцессора соединены соответственно с первыми входами коммутаторов сверток адреса и данных, выходы которых соединены соответственно с вторыми входами СВ-ЗрТОК с1Дреса и данных, выход первого триггера у четности соединен с вторыми входами коммутаторов сверток адреса и данных, первым информационным входом коммутатора сигналов, выход второго триггера четности соединен с третьими входами коммутаторов сверток адреса и данных и с втбрым информационным входом ком-, мутатора сигналов ошибки, входы первого и второго опер)андов микропроцессора соединены соответственно с четверты1.-.и и пятыми, входами коммутаторов сверток ащреса и данных, шесть1е входы которых соелинены с шиной логического нуля, вход переноса микропроцессора соединен с первьвл входом элемента И-НЕ, выход переноса арифметико-логического блока соединен с вторым входом элемента И-НЕ, выход которого соединен с третьим информацион- . ным входом коммутатора сигналов ошибки, выходы промежуточных переносов арифметиког-логического блока соединены ссоответствующими входами элемента И-НЕ, вход сигналов контроля микропроцессора соединен с четвертым информационным.входом коммутатора сигналов ошибки .- На черте;9(е представлена схема предлагаемого микропроцессора. Микропроцессор содержит арифметико-логический блок 1, конструкция коTopot-o описана в t33, первый и второй коммутаторы 2 и 3 операндов, блок 4 регистров, регистр 5 данных, регистр 6 адреса, свертку 7 по модулю два данных, первыйдриггер 8 четности, свертку 9 по модулю два адреса, второй триггер 10 четности, блок 11 микропрограммного управления с блоком 12 постоянной памяти и регистром микрокоманд с полями 13 - 15, выходную шину 16 адреса, выходную шину 17 данных, входы 18 и 19 первого и второго операндов, блок 20 синхронизации , коммутатор 21 свертки адреса, коммутатор 22 свертки данных, элемент И-НЕ .23, коммутатор 24 сигнгшов оыиб.кк, контрольный выход 25 микропроцессора, входы 26 и 27 нарац1ива1-1ия сверток данных и адреса, вход 28 и выход 29 переноса микропроцессора и вход 30 сигналов контроля микропроцессора.

Арифметико-логический блок 1 микропроцессора выполняет арифметические - (сложение, звычитание и т.д.) и логические (конъюнкцию, дизъюнкцию, исключающее ИЛИ и т.д.) операции. Выполнение операций в арифметико-логическом блоке 1 происходит под управлением 10 кода мик рок Оман ды, поступающего Из блока 11 микропрограммного управления (поле 13 микрокоманды). Каждая очередная микрокоманда задает свою операцию в арифметико-логическом блоке 1.15 Операции в арифметико-логическом блоке 1 выполняются комбинационно над операндами, поступакщими на входы арифметико-логического блока 1 с выходов первого и второго коммутатора 20 2 и 3 операндов. Коммутаторы 2 и 3 также управляются кодом микрокоманды из блока 11 микропрограммного управления и подключают -на вход арифметико-логического блока один из следую- 95 щих возможных источников операндов: входы 18 и 19 первого и второго операндов, блок 4 регистров, регистр 5 данных. При этом конкретный номер регистра из блока 4 регистров задает-,ся микЕ ркомандой из блока 11 микропрограммного управления (поле 13 регистра микрокоманды),

Результат операции арифметико-логического блока 1 записывается в один из регистров-приемников: регистра 5 35 данных, регистр б адреса или один из регистров блока 4. Выбор приемника хакже осуществляется кодом из поля 13. Блок 4 регистров представляют , собой набор адресуемых регистров, 40 предназначенных для хранеудя промежуточных результатов вычислений и операндов..

Регистр 5 данных и регистр 6 сщре-45 са служат для временного хранения ре- зультатов операции арифметико-логического блока и для выдачи этих результатов на выходные шины 16 адреса или 17 данных соответственно. -«

Свертки 7 и 9 по модулю два-.подключены к выходам регистров 5 и 6 анных и адреса. Результаты сверток передаются в выходные шины адреса и анных в качестве контрольных разря ов соответствующих кодов или записываются в первый и второй триггеры 8

и 10 четности по сигналам, из блока 20 синхронизации. К входам расширения

сверток подключены коммутаторы 21 и 22 сверток адреса и данных, переключеине60 которых под управлением поля 14 регистра микрокоманд обеспечивает комутацию на вход расширения сверток дной из следующих цепей: выхода первого триггера 8 четности, выхода вто-б5

рого триггера 10 четности, константы О.

Поле 1з регистра микрокоманд задает основные функции арифметико-логического блока 1, коммутаторов 2 и 3 операндов, блока 4 регистров и т.д.

Поле 15 в микрокоманде опре целяет функционирование блока 20 синхронизации, который управляет записью первого и второго триггеров 8 и 10 четности, а также опросом коммутатора и сигналов ошибки, на котором формируется сигнал Ошибка.

Элемент И-НЕ 23 предназначен для анализа наличия всех переносов (входного, выходного, промежуточных) арифметико-логического блока 1. Выходы элемента И-НЕ 23 и выходы первого и второго триггеров 8 и 10 четности подключены к входам коммутатора 24 сигналов ошибки.

Выход сигналов Ошибка подключен к контрольному выходу 25 и к блоку 12 постоянной памяти, в котором сигнал Ошибка вызывает .переход к микропрограмме диагностики. Микропроцессор с контролем работает под воздействием микрокоманд, вырабатываемых блоком 11 микропрограммного управления.

Выполнение рабочих микроопераций задается полем 13 регистра микрокоманд. Контрольные микрооперации выполняются (над теми же операндами) отдельно от рабочих или совмещаются с рабочими (встраиваются). Выполнение контрольных микроопераций задается полем-13 совместно с полем 14 и 15 регистра микрокоманд.

Последовательность выполнения KOHтрольных микроопераций зависит от места хранения операндов и типа операции, с которой совмещаются контрольные микрооперации.

Рассмотрим вариант функционирования .устройства в случае выполнения операции сложения наиболее сложной для совмещения контрольных микроопераций с рабочими/ над операндами, находя14имися в блоке 4 регистров общего назначения. Результат операции также быть записан в один из регистров блока 4 общего назначения. Будем считать, что разрядность регистров адреса и данных одинакова.

Первая контрольная микрокоманда /задает выполнение функции конъюнкции над опеврандами с .записью результата . .в регистр 6 адреса и заносит значение четности результата в первый триггер 8 четности. При этом к входу расширения свертки 7 по модолю два под управлением поля 14 микрокоманды через коммутатор 21 свертки подключается константа О. Вторая контрольная микрокоманда задает операцию дизъюнкции над исходными операндами с записью результата в регистр 6 адреса |И заносит в первый триггер 8 четнодти результат совместной-сварки по моДОлю два содержимого регистра 6 адреса и предьщущего значения кода триггера 8 четности. Для этого коммутатор 21 подключают к входу расширения свертки 7 выход триггера 8. Таким образом после выполнения этой микрокоманды в триггере 8 четности храниться-сумма по МОДОЛЮ два результатов операций диъюнкции и конъюкции над исходными операциями. Третья контрольная микро 1ко 1ланда задает выполнение функции Исключение ИЛИ над исходными операндами с записью результата в регистр 5 данных. При этом значение совместной свертки по модулю 2 результата и значения кода триггера 8 четности , подключенного к свертке 9 через коммутатор 22, заносится во.второй триггер 10 четности. При правиль ном выполнении описанных микрорперацрй в триггер 10 будет записан в соответствии с тождеством. р М-) Р Гн р- П - или . или - Де Р,, П1екл.или значение четности результатов логических операций И, ИЛИ, исключайщее ИЛИ соответственно над одними и теми же операциями. Четвертая микрокоманда задает функцию арифметико-логического блока 1 и коммутаторов 2 и 3 операндов,при которой вырабатываются все промежуточные .переносы арифметико-логическо го блока 1. Например, задается функция сложения двух операндов и входного переноса. При этом значения опе рандов ( подачи определенных ко стант через коммутаторы операндов задают, например, А ОО...О В 11...1), чтобы при сложении с входным переносом., задаваемым блоком 11 микропрограммного управления, во все разрядс«, а следовательно, и группах арифметико-логического блока 1 образовался сигнал переноса. Сигнал о наличии всех переносов выр атываетс комбинационно на элементе И-НЕ 23 и поступает на колшутатор 24 сигналов ошибки. В этой же ч етвертой микрокоманде, поле 15 зещает в блоке 20 син хронизации, режим выработки сигнала опроса коммутатора 24 сигналов ошибки. Сигнал Сйпибка на выходе этого коммутатора и на контрольном выходе 25 микропроцессора выраба:тывается в .сле дующих случая;х: при отсутствии хотя бы одного из анализируемых переносов арифметико-логического блока 1, при единичном состоянии триггера 10 четности. Сигнал Ошибка обрабатываетс на микрокомандном уровне в блоке 11 микропрограммного управления и передается в систему, в составе которой (Работает микропроцессор для об1 аботк на системном уровне. Таким образом, -осуществляется контроль всех цепей и узлов, участвующих в операции сложения. Сама рабочая операция сложения может бы-ть выполнена до или после (а иногда н в промежутке) описанной последовательности контрольных микроопераций. . Для логических операций типа И, ИЛИ, исключающее ИЛИ микропроцессор обеспечив1ает контроль по модулю лва с последовательным вычислением дополнительной информации, (результатов сверток дополн;1Ю1цих логических операций) . При этом полут ение результата требуемой логической операции совмещается в микропрограмме с получением результата контроля. Отсутствие сиг-, нала Ошибка свидетельствует о правильности выполнения операции. При различных разрядностях регистра 5 данных и регистра & адреса выполнение описанной процедуры контроля происходит в контурах: регистр б адреса-свертка 7 по модулю два- триг-г гер В четности- коммутатор 21 сверт„ки- свертка 7, - регистр 5 данныхсвертка 9. по модулю два- триггер 10 четности- коммутатор 22 сверткисвертка 9. При этом, если в качестве операндов или результата операции арифме-А-ико-логйческого блока 1 выступают адреса, контрольные микроопе- ч рации выполняются в контуре регистра б адреса, если данные - то в контуре регистра 5 дайных. Контрольные микрооперации при этом выполняются аналогично описанному выше, а при анализе результатов контроля в четвертой контрольной микрооперации блок 20 синхронизации стробйрует на коммутаторе 24. сигналов ошибок выход того триггера четности, в контуре которого производились контрольные микрооперации. Контроль приема входных кодов производитсяпри записи информационных разрядов входного кода с входов 18 или 19 операндов через арифметико- логический блок 1 в регистр б адреса или регистр 5 дайных подключением контрольного разряда входного кода через кокйкутатор 21 или. 22 к свертке по два соотйетствующего регистра. При этом в соответствующий триггер четйости запишется результат срйместной свертки по модулю два информационных и контрольного разрядов входного Kojcia. При отсутствии сбоя в триггере четности будет записан О. Анализ-состояния триггера производится как описано выше. Для обеспечения реализации микроI процессора в Виде йодуля,имеется входы, обеспечивающие наращиваемость модулей: входы 26 и 27 наращивания разрядности. сверток, соединенные с входами коммутаторов 21 и 22 сверток, вход 30 сигналов контроля, соединенный с ВХОДФ1 коммутатора 24 сигналов

ошибки. Наращивание микропроцессорг5Н выполненньох в виде модулей, осуществляется соединением цепей переносов {выход 29 переноса младших разрядов подключается к входу 28 переносов старших разрядов), объединением сверток по цепям наращивания разрядности (выход соответствующей свертки предыдущего модуля подается на вход наращивания разрядности 26 или 27 соответствунхцей свертки последующего модуля объединением цепей выработки .сигнала Ошибка) подключ ением контрольного -выхода 25 предьщущего модуля к входу сигналов;контроля 30 последующего МОДУЛЯ. Функционирование такого модульного устройства аналогично описанному выше. При этом выход соответствующей свертки 7 или 9 последнего в этой цепочке модулей является выходом контрольного разряда всего выходного кода (соответственно адреса или данных). На входы наращивания разрядности 26 и 27 свертки в цепочке модуля при этом подается константа О.

Техническая эффективность предлагаемого микропроцессора с контролем заключается в упрощении контрольного оборудования за счет исключения дублирующего арифметико-логического блока,схемы сравнения результатов обра;ботки информации основным и дублирующим арифметико-логическим блоком,свертки по модулю 2 выходного кода арифметикологического блока, кроме этого сокращается длина микрокоманды за счет исключения полей управления дублирующим арифметико-логическим блоком. Введенные дополнительные поля микрокоманды имеют меньшую разрядность, чем исключенные.

Микропроцессор с контролем обеспечивает возможность локации неисправности с точностью до модуля или группы модулей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммный процессор | 1977 |

|

SU705452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Методы обнаружения ошибок в работе ЭЦВМ.М, Мир, 1972, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| Под ред.А.А.Васенкова и В.А | |||

| Шахнова | |||

| М., Радио и связь, 1982, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-05-07—Публикация

1981-01-12—Подача