(54) УСТРОЙСТВО ДЛЯ С/ВИГА СО ВСТРОЕННЫМ КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Счетчик с контролем на четность | 1981 |

|

SU1010728A1 |

| Устройство для контроля обработки двоичной информации | 1982 |

|

SU1089581A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Устройство для контроля двоичного кода на четность | 1981 |

|

SU989558A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| Устройство для контроля регистраСдВигА | 1979 |

|

SU842968A1 |

| Постоянное запоминающее устройство с самоконтролем | 1984 |

|

SU1274005A1 |

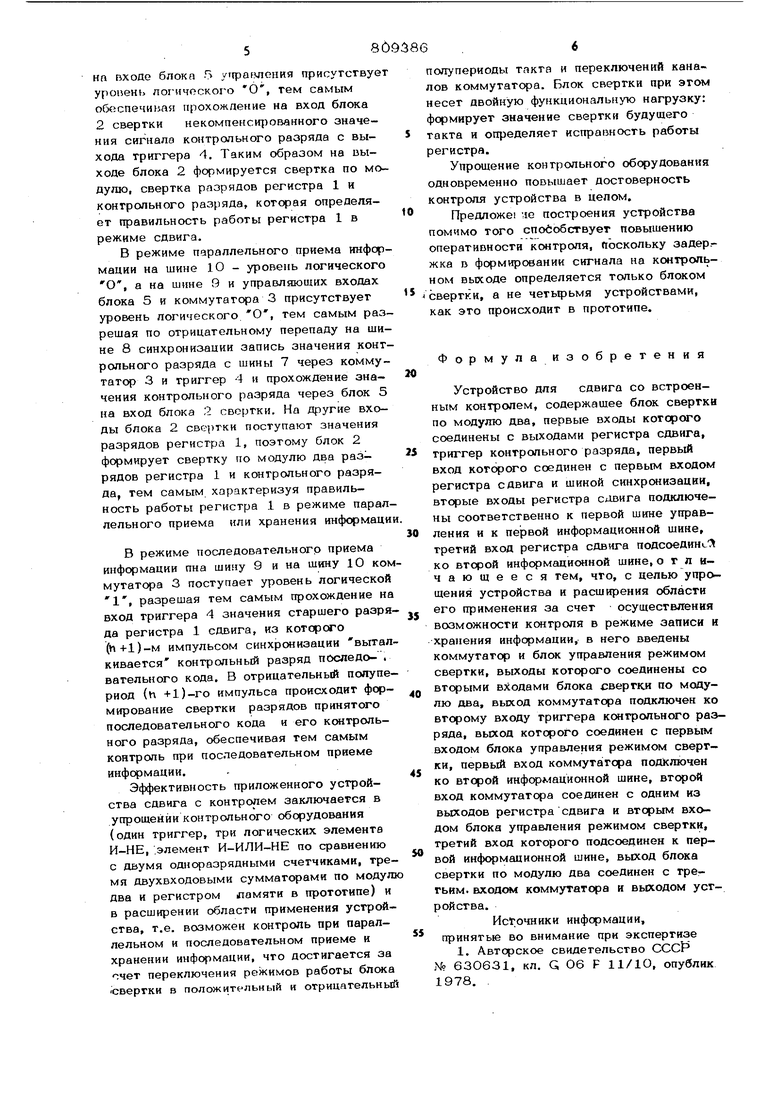

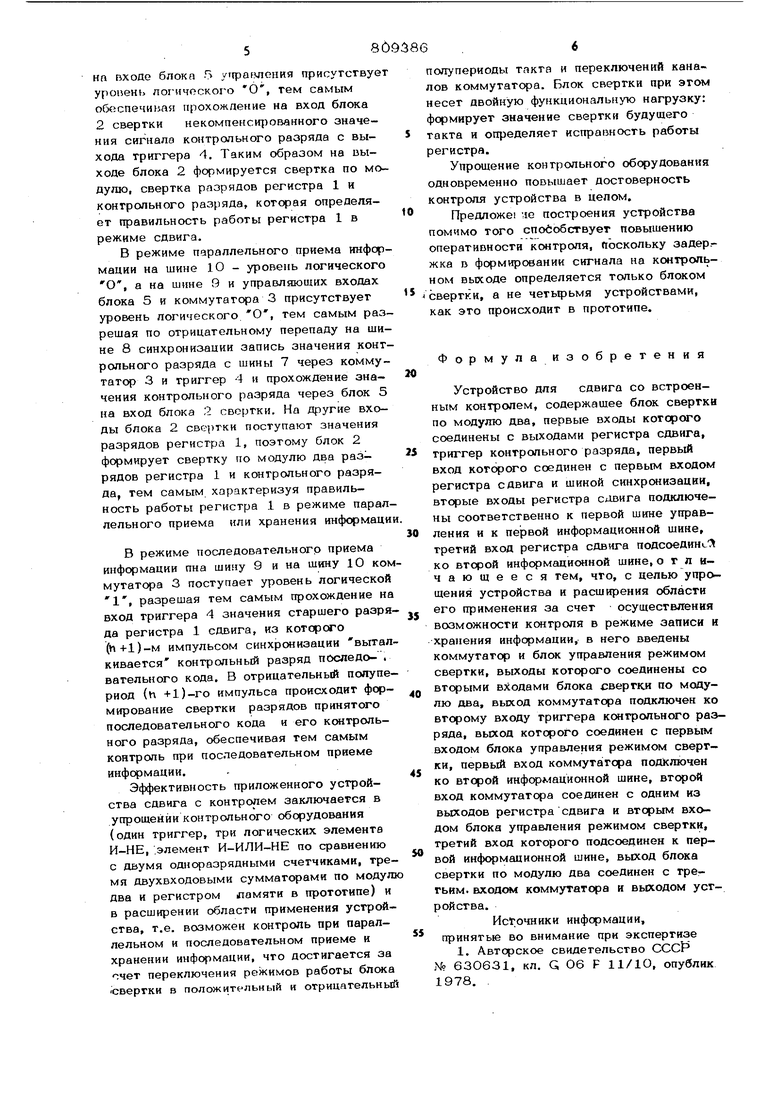

Изобретение относится к вычислитель ной технике и дискретной автоматике и может быть использовано в качестве уст ройства сдвига (хранения) со встроенным контролем. Известны регистры сдвига со схемам контроля, обеспечивающими контроль рабо ты регистра на основе анализа свертки по модулю два разрядов регистра в данном такте работы и значения этой свертки 1 и 2. Из известных устройств наиболее близ ким по технической сущности является устройство для проверки четности двоичного регистра, которое содержит сдбиговый регистр, два одноразр51двых счетчика, схему свертки по модулю два, три двухвходовых сумматора по .Модулю два регистр памяти. Выходы регистра сдвига соединены со входами схемы свертки и одноразрядных счетчиков, выходы которых соединены со входами первого сумматора. Выход схемы свертки соединен со входом регистра памяти и входом третьего сумматора, выход которого является выходом устройства, а второй вход соединен с выходом второго сумматора, входы которого соединены с выходом регистра и выходом первого сумматора ГЗ . Недостатками указанных устройств являются сложность схемы контроля, снижение достоверности контроля, а также отсутствие контроля записи и хранения информации в регистре. Цель изобретения состоит в упрощении устройства и расширении области применения за счет осуществления возможности контроля в режиме записи и хранения информации. Поставленная цель достигается тем, что в устройство для сдвига со встроенным контролем, содержащее блок свертки по модулю два, первые выходы которого соединены с выходами регистрй сДвига, триггер контрольного разряда, первый вход которого соединен с первым входом регистра сдвига и шиной синхрониации, вторые входы регистра сдвига аодключены соответственно к первой шине управления и к первой информационной шине, третий вход регистра сдвига подсоединен ко второй информацисиной шине, введены коммутатор и блок управления режимом свертки, выходы которого соединены со вторыми входами блока свертки по модулю два, выход коммутатора подключен ко второму входу триггера контрольного разряда, выход которого соединен с первым входом блока управления режимом свертки, первьй вход ком мутатора подключен ко второй информационной шине, второй вход коммутатора соединен с одним из выходов регистра сдвига и вторым входом блока управления режимом свертки, третий вход которого подсоединен к первой информационной шине, выход блока свертки по модулю два соединен с третьим входом комму татора и выходом устройства. Сущность изобретения заключается в построении устройства на указанных блоках таким образом, что блок управления переключает режим работы свертки в положительные и отрицательные полупериоды такта, а также в зависимости от сигналов управления регистра, причем в положительный попупериод блок свертки формирует признак четности разрядов регистра для следующего такта, запоминае; мый в триггере контрольного разряда, а в отрицательный полупериод блок свертки сравнивает запомненное значение признак четности, либо записанное в триггер при приеме или ,хранении значение контроль ного :азряда кода, введенного в регистр, текущей четностью разрядов регистра, оп ределяя таким образом исправность работы регистра как в режиме сдвига, так и в режиме приема и хранения информации. Таким образом, блок свертки несет двойную функциональную нагрузку: форми рование будущего значения четности и оп ределение исправности работы регистра. Достижение цели изобретения способствует выполнению блока управления режимом свертки в виде трех 3-входовых логических элементов И-НЕ, первые вход являются информационными вход ми блока, вторые и третьи входы об.ьед иены и служат первым и вторым управля щими входамв блока, а входами блока яв ляются выходы элементов И-НЕ. На фиг. 1 изображено устройство, фун кциональная схема; на фиг. 2 приведен вариант выполнения его электрической схем Предлагаемое устройство (фиг..1) соде-ржит регистр 1 сдвига, блок 2 свертки по модулю, коммутатор 3, триггер 4 контрольного разряда, блок 5 упранутения режимом свертки, информационные шины 6 и 7, шина 8 синхронизации, шины 9 и 10 управления и выход 11 устройства. На принципиальной схеме (фиг.2) приведен 12-разрядный регистр 1 на 3-х элементах 133 ИР1, блок 2 свертки на 2-х элементах 133 ИП2, коммутатор 3 (элемент И-ИЛИ-НЕ 133 ЛРЗ), триггера 4 контрольного разряда (JK -триггер 133 ТВ1), блока 5 управления три элемента ЗИ-НЕ 133 ЛА4. Запись информации в регистр-и триггер производится по отрицательному перепаду на входах синхронизации. Принцип работы устройства заключает ся в следующем. В режиме сдвига на шине 9 управления присутствует уровень логической , а на шине 10 управления - уровень логического О, На шине 8 синхронизации положительный полупериод такта будет также уровень 1. Высокие потенциалы на управляющих входах блока 5 разрешают прохождение инвертированных значений сигнала старшего разряда регистра 1 сигнала последовательного входа регистра и контрольного разряда на входы блока 2 свертки, на другие входы которого поступают текущие значения сигналов всех разрядов регистра .1. При сложении по модулю два прямые и инверсные значения сигналов старшего разряда регистра 1 и контрольного разряда дают логические , а в сумме - логический О. Поскольку на вход блока 2 свертки с шины 6 поступает будущее значение младшего разряда регистра 1, то тем самым в положительный полупериод такта на выходе блока 2 свертки формируется значение четности будущего такта, которое через коммутатор 3, открытый управляющим сигналом, поступает на вход триггера 4 контрольного разряда. По окс«чанию положительного полупериода такта (отрицательному фронту) происходит запоминание значения четности будущего такта в триггере 4 и изменение информации в регистре 1 сдвига. В отрицательный полупериод такта на входы блока 2 свертки поступают новые значения сигналов разрядов регистра 1 сдвига. В отрица- тельный полупериод такта на входы блока 2 свертки поступают новые значения сигналов разрядов регистра 1 сдвига. На щине 8 синхронизации и, соответстпонно. нп входе блока 5 уфару1ения присутствуе уровень ЛОГНЧОСКО1-О О, тем самым o6 ;cne4H)ias прохожаенне на вход блока 2 свертки некомпенсированного значения сигнала контрольного разряда с выхода триггера 4. Таким образом на выходе блока 2 формируется свертка по модулю, свертка разрядов регистра 1 и контрольного разряда, которая определяет правильность работы регистра 1 в режиме сдвига. В режиме параллельного приема инфор мации на шине Ю - уровень логического О, а на шине 9 и управляющих входах блока 5 и коммутатора 3 присутствует уровень логического О, тем самым раз решая по отрицательному перепаду на ши не 8 синхронизации запись значения конт рольного разряда с шины 7 через коммутатор 3 и триггер 4 и прохождение зна- чения контрольного разряда через блок 5 на вход блока 2 свертки. На другие входы блока 2 свертки поступают значения разрядов регистра 1, поэтому блок 2 формирует свертку по модулю два разрядов регистра 1 и контрольного разряда, тем самым характеризуя правильность работы регистра 1 в режиме парал лельного приема или хранения информаци в режиме последовательного приема информации она шину 9 и на шнну 10 ком мутатора 3 поступает уровень логической , разрешая тем самым прохождение на вход триггера 4 значения старшего разря да регистра 1 сдвига, из которого (п+1)-м импульсом синхронизации вытал кивается контрольный разряд последо- . вательного кода. В отрицательный попупериод (л +1)-го импульса происходит формирование свертки разрядов принятого последовательного кода и его контрольного разряда, обеспечивая тем самым контроль при последовательном приеме информации. Эффективность приложенного устройства сдвига с контролем заключается в упрощении контрольного оборудования (один триггер, три логических элемента И-НЕ, .элемент И-ИЛИ-НЕ по сравнению с двумя одноразрядными счетчиками, тремя двухвходовыми сумматорами по модулю два и регистром ламяти в прототипе) и в расширении области применения устройства, т.е. возможен контроль при параллельном и последовательном приеме и хранении информации, что достигается за очет переключения режимов работы блока свертки в положительный и отрицательный полупериоды такта и переключений кана лов коммутатора. Блок свертки при этом несет двойную функциональную нагрузку: формирует значение свертки будущего такта и огфеделяет исправность работы регистра. Упрощение контрольного оборудования одновременно повышает достоверность контроля устройства в целом. Предложе le построения устройства помимо того способствует повышению оперативности контроля. Поскольку задер.жка D формировании сигнала на контрольном выходе определяется только блоком свертки, а не четьфьмя устройствами, как это происходит в прототипе. Формула изобретения Устройство для сдвига со встроенным контролем, содержащее блок свертки по модулю два, первые входы которого соединены с выходами регистра сдвига, триггер контрольного разряда, первый вход которого соединен с первым входом регистра сдвига и шиной синхронизации, вторые входы регистра сдвига подключены соответственно к первой шине управления и к первой информационной шине, третий вход регистра сдвига подсоединс/Л ко второй информационной шине, отличающееся тем, что, с целью упрощения устройства и расширения области его применения за счет осуществления возможности контроля в режиме записи к хранения информации, в него введены коммутатор и блок управления режимом свертки, выходы которого соединены со вторыми входами блока свертки по модулю два, выход коммутатора подключен ко второму входу триггера контрольного разряда, выход которого соединен с первым входом блока управления режимом свертки, первый вход коммутатора подключен ко второй информационной шине, второй вход коммутатора соединен с одним из выходов регистрасдвига и вторым вхоом блока управления режимом свертки, ретий вход которого подсоединен к перой информационной шине, выход блока вертки по модулю два соединен с треьим, входом коммутатора и выходом устойства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР O 630631, кл. Q Об F 11/10, опублик 978. .

8093868

В 6

«-5 --

фие.1

т

10

Tn eintef,fef

ut.t

Авторы

Даты

1981-02-28—Публикация

1979-06-11—Подача