(54) УСТЮЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1976 |

|

SU763912A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Устройство широкодиапазонного логарифмического аналого цифрового преобразования | 1980 |

|

SU900440A1 |

| Устройство для возведения в куб | 1985 |

|

SU1283803A1 |

| Аналого-цифровое множительное устройство | 1980 |

|

SU883930A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Аналоговое множительное устройство | 1987 |

|

SU1497625A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПРЯМОУГОЛЬНЫХ КООРДИНАТ В ПОЛЯРНЫЕ | 1992 |

|

RU2085995C1 |

| Устройство для измерения среднего индикаторного давления двигателя внутреннего сгорания | 1984 |

|

SU1283559A1 |

| ТРИГОНОМЕТРИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2085994C1 |

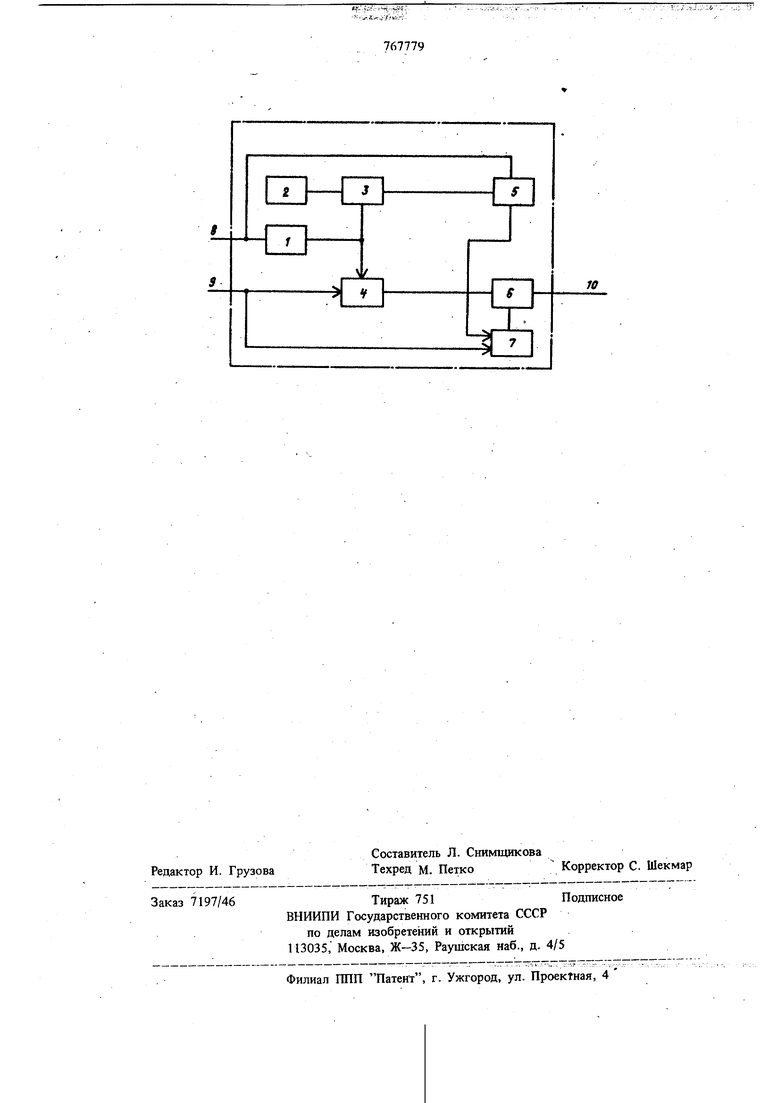

Изобретение относится к области вычислительной и измерительной техники, может быть применено в измерительных устройствах для измерения мощности, расхода газа, в коррелометрах. Известно устройство для умножения, содержащее реверсивные счетчики, цифроаналоговые преобразователи, нуль-органы, переключатели 1 Это устройство отличаете больщой сложностью. Наиболее близким техническим решением к изобретению является устройство, содержаще узкодиапазонный блок умножения 2. Такое устройство не обеспечивает достаточной точности. Цель изобретения - повышение точности устройства. Поставленная цель достигается тем, что уст. ройство содержит амплитудный анализатор, ист ник опорного напряжения, дискретно-изменяемые резисторы, сумматоры, причем первый вход устройства соединен со входом амплитуд ного анализатора и первым входом первого сумматора, второй вход которого через первы дискретно-изменяемый резистор связан с источником опорного напряжения, второй вход устройства - с первым входом, узкодиапазонного блока умножения, второй вход которого соединен с выходом первого сумматора, а выходс первым входом второго сумматора, второй вход которого через второй дискретно-изменяемый резистор соединен со вторь1м входом устройства, а выход второго сумматора является выходом устройства, выход амплитудного анализатора подключен к управляемым входам дискретно-изменяемых резисторов. На чертеже приведена структурная схема устройства. Преобразователь содержит амплитудный анализатор Г, источник 2 опорного напряжения, дискретно-изменяемые рез1нсторы 3 и 4, сумматорь 5 и 6, узкодиапазонный блок 7 умножения, входные 8 и 9 и выходную 10 клеммы. Принцип действия предложенного устройства следующий. Входной сигнал и з ,поступающий на клемму 8, вызывает появление на его выходе соответствующих сигналов. Вследствие этого устанавливаются определенные значения дискретно изменяемых резистороЬ 3 и 4. На выходе сумматора 5 формируется разность входного сигнала Ug.j и сигаала, поступающего от опо ного источника 2 . . U,--Ue,x -UonK, где Uj-сигнал на выходе сумматора 5; сигнал на выходе источника 2; коэффициент передачи сумматора д сигнала от источника 2, зависящий от значения дисректно-изменяемо. го резистора 3. Узкодиапазонный блок умножения перемно жает сигналы с выхода сумматора 5 и с клем мы 9 (второй входной сигнал что на выходе второго сумматора 6 получается сигнал в соответст1вии с выражением ., где К л-коэффициент передачи су1йматора 6, определяемый значением дискретноизменяемого резистора 4; К -коэффициент передачи множительног блока 7. Если выбрать соотношения между коэффициентами такими, чтобы то 2 BX-i в а ; следовательно, выполняется операция умножения без методической погрешности. Предложенное устройство позволяет существенно повысить точность по сравнению с испол зуемым простейшим блоком умножения. Так при погрешности блока 7 10-1% и и -5 пороговых элементов в амплитудном aHajfasaторе 1 погрешность предложенного устройства получается соответственно 2-0,2% ( -22 ) Погрешность устройства практически не зависит от стабильности характеристик пороговых элементов, что является существенным преиму ществом предложенного устройства по сравнению с известным, где уровни квантования, задаваемые с помощью преобразователей коднапряжение, должны устанавливаться с высокой степенью точности. Для достижения еще более высокой точност выполнения операции умножения осуществляется каскадное включение устройств, выполнен ных по предложенной схеме. При этом первое из НИХ строится с применением известного простейшего множительнрго блока, а для второго в качестве множительного блока применяется первое. При каскадном включении точность повышается в .-И,где И Via Ио, ис ло пороговых элементов в первом, втором и 4 третьем устройствах для умножения для трехкаскадной схемы построения. При каскадном включении требуется меньшее число пороговых элементов (в анализаторе), чем для однокаскаддюй схемы той же точности. Для изменения входных сигналов в широком диапазоне на обоих входах множительного устройства целесообразно такое соединение каскадов, когда на каждом входе включается амплитудный анализатор и дискретно-изменяемое сопротивление. Например, для двухкаскадной схемы выход первого сумматора первого каскада подключается к дискретно-изменяемому сопротивлению и одному входу множительного устройства низкой точности второго каскада, а вход первого каскада, соединенный с дискретно-изменяемым сопротивлением первого каскада, к амплитудному анализатору и первому сумматору второго каскада. Предложенное устройство позволяет; повысить точность в 10 и более раз по сравнению с известными быстродействующими множительными устройЬтвами, также, как прототип, оно может быть реализовано методами интегральной технологии. Формула изобретения Устройство для умножения, содержащее узкодиапазонный блок умножения, отличающееся тем, что, с целью повышения точности, оно содержит амплитудный анализатор, источник опорного напряжения, дискретно-изменяемые резисторы, сумматоры, причем первый вход устройства соединен с входом амплитудного анализатора и первым входом первого сумматора, второй вход которого через первый дискретно-изменяемый резистор соединен с источником опорного напряжения, второй вход устройства соединен с первым входом узкодиапазонного блока умножения, второй вход которого соединен с выходом первого сумматора, а вь1ход - с первым входом второго сумматора, второй вход которого через второй дискретно-изменяемый резистор соединен со вторым входом устройства, а выХод второгб сумматора является выходом устройства, выход амплитудного анализатора соединен с управляемыми входами дискретно-изменяемых резисторов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 435530, кл. G 06 G 7/16, 1973. 2.Шило В. Л. Линейные интегральные схемы. Советское радио, 1974, с. 162-163 (прототип).

Авторы

Даты

1980-09-30—Публикация

1976-08-01—Подача