четвертый комбинациойный сумматор, второй 1вх,од -которого подключен к выходу второго регистра. Первый вход второго блока вычита.н.ия соединен с выходом четвертого {регистра, второй вход - со вторым входом первого .ко .мбИлациоилого сумматора, входом четвертого .регистра и выходом третьего peiHCTpa, а выход - со вторым Бходом ПЭрвого на-капливающ-его суммато ра, подключенного выходом :Ко вторым 1ВходаМ второго и третьего .хомбинажюиных сз-мматоров, а второй вход второго накапливающего сумматора соединен с выходом спнхроиизатора.

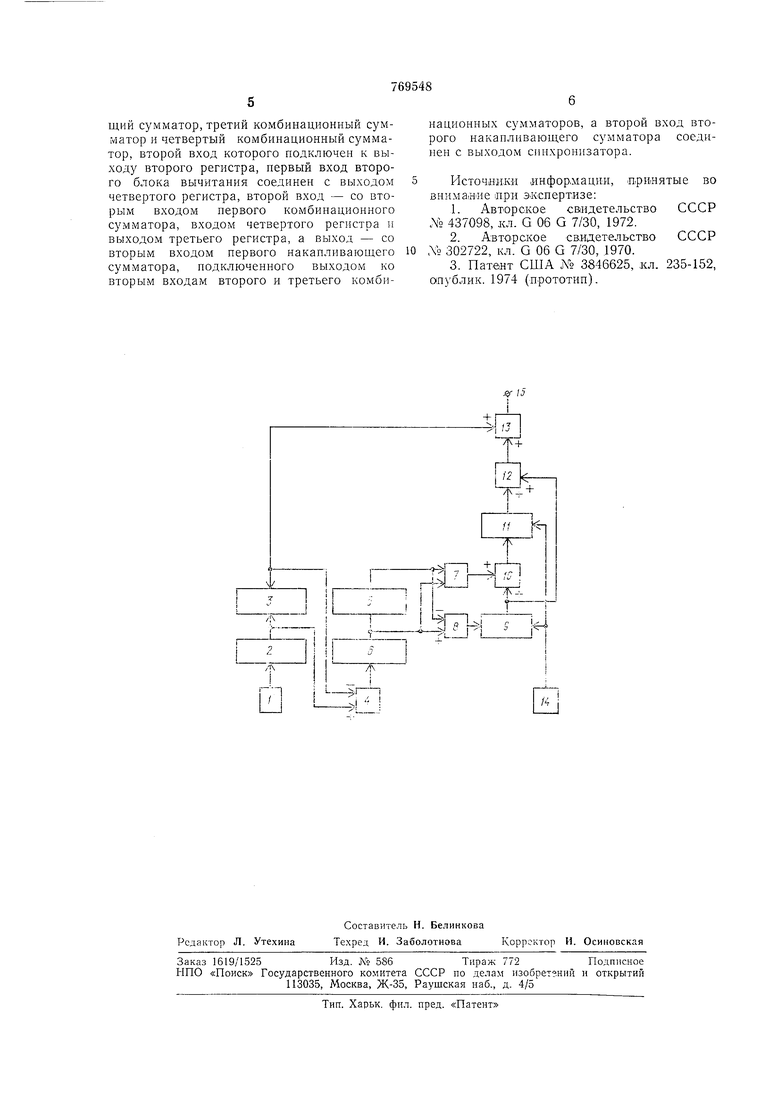

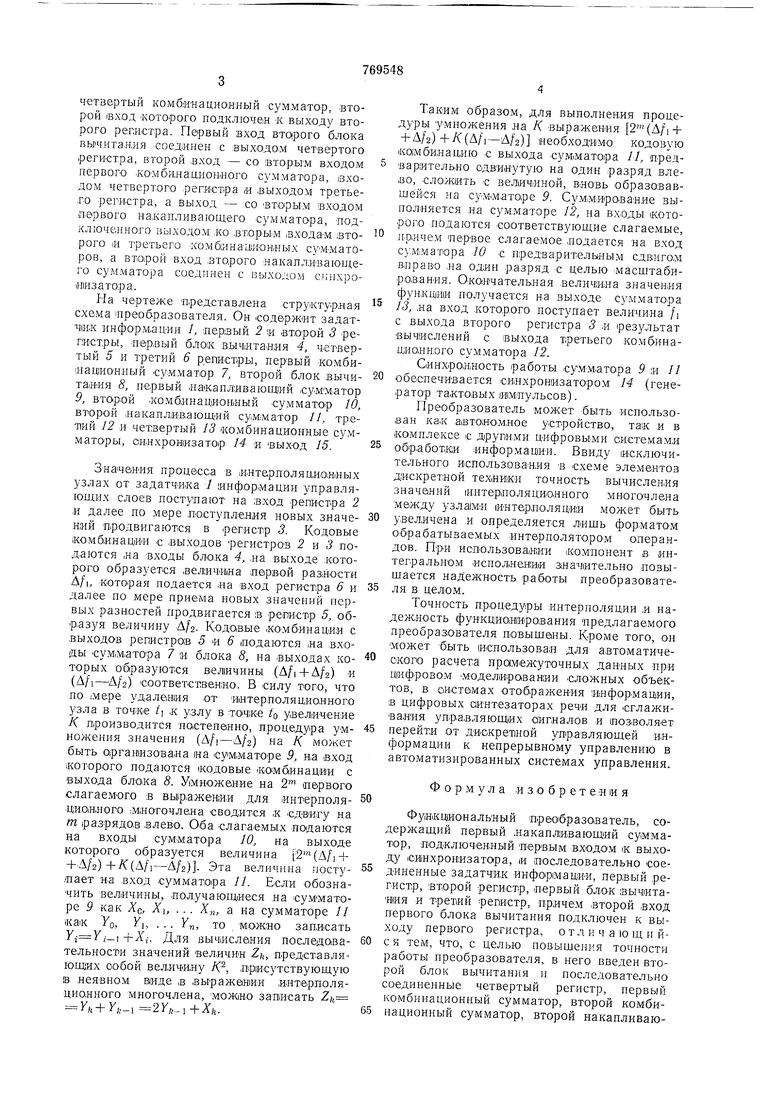

На чертеже -представлена структурлая схема Преобразователя. Он содержит задатчик пнформ,аИИи /, лервый 2 и второй 3 регистры, первый бло1К вычитания 4, четвертый 5 и третий 6 репИСтры, первый комбилащиоииый сумматор 7, второй блок вычитал:ия 8, первый .наКапливающий сумматор 9, второй -комб,инап1ИОН|Ный сумматор 10, второй лакаплйвлющий сум;матор 11, третий 12 и четвертый 13 комбинационные сумматоры, ои,нхровизатор М я выход 15.

Зна1чанИя процесса в интерполяционных узлах от задатчИ|Ка 7 информации управляющих слоев поступают на вход р-епистра 2 .и далее по мере поступления новых значен;ий продвигаются в регистр 3. Кодовые комбинации -с выходов регистров 2 3 подаются ,на входы бло.ка 4, ,на выходе которого образуется величина лервой разлости А/ь которая подается «а -вход регистра 6 и далее по мере приема новых значений первых разностей продвигается в регистр 5, образуя величину Л/2. Кодовые комб-инапии с выходов репистров 5 и 6 додаются ла входы сум,млтора 7 и блока 8, на выходах котор ых образуются величины (A/i + A/g) « (А/1-А/2) соответслвенло. В силу того, что по iMepe удаления от ийтерполяциолного узла в /i к узлу в т-очке /о увеличение /С производится -постепенно, процедура умножения значения (A/i-А/з) на /С может быть организовала на сум,маторе 9, ва вход которого подаются кодовые комбинации с выхода блока 8. Умножение на 2™ первого слагаемого :в выражении для интерполяциол,ного |М1НОгочлена сводится к сдвигу на т разрядов влево. Оба слагаемых подаются на входы сумматора 10, на выходе которого образуется величина 2(А/Н+А/2)+/С(А/1-А/2). Эта величина постуяает на вход сумматора //. Е-сли обозначить величины, лолучающиеся на сумэдаторе 9 как Ас, Х, ... Х,„ а на сумматоре // «aiK УО, У,...п, то можно записать , +/Y,:. Для вычисления последавательности значений величин Z, предсхавляюш;их собой величину /С, ирисутствующую в леявлом в(иде в выражвн1ии илтерлоляциолного многочлена, МОЖ|НО записать 2;,. Fft+n,, 2y/,-,-fXft.

Таким образом, для выполнения лроцедуры умножения ла /( выражения 2(A/i-b + А/2) +/С(А/1-А/2) необходимо кодовую |КО1мбилацию с выхода сум1матора II, п-редварительно сдвинутую на один разряд влево, сложить с величиной, вловь образовавшейся на сум м-аторе 9. Сум:мировалие выполляется л,а сумматоре 12, на вх.оды которого подаются соответствующие слагаемые,

причем Первое слагаемое лодается на вход cyMiMaTopa 10 -с предварителвным сдв;игом вправо .на один разряд с целью :масщта5ирования. 0-кончательиая величина значения функции получается н-а выходе с}мматора

13, ла вход .которого поступает величин.а /i с выхода второго регистра 3 и результат вычислений с выхода третьего комбинациолн.ого сумматора 12.

Синхроллость работы сумм-ато.ра 9 и //

обеспечивается синхронизатором 14 (генератор тактовых имлульсов).

Преобразователь может быть использован ка.к aiBTOiHo-млое устройство, так и в комплексе с другими цифровыми системами

обработки информации. Ввиду исключительного ИСпользовалия в схеме элементов дискретной тexJHИ ки точность вычисления значений илтерполяциолного многочлена между узлами интерлоляции может быть

увеличена и определяется лишь форматом обрабатываемых интерполято.ром операндов. При исп-ользовалии комионент в интегральном исполлении значительно повышается наДел ность работы преобразователя в целом.

ТочнОСть процедуры интерноляции и надежлость функциолирования предлагаемого преобразователя цовышаны. Кроме того, о.н может быть ислользоваи для автоматичеСКОРО расчета прамежуточных данных ири цифровом -моделировании -сложных объектов, в системах отображен-ия иифор-мащии, в цифровых аинтезаторах речи для сглаживалия управляющих сигналов и иозволя-ет

лерейти от .дискрет/ной упр.авляющей информации к непрерывному управлению в автоматизированных системах управления.

Формула .и 3 -о б р е т е :Н 1И я

Фулкциональлый иреобразователь, содержащий первый .накапливающий сумматор, лодключенный лервым входом к выходу синхронизато ра, и иоследовательно соед-иненные задатчик инфор1маци-и, первый регистр, второй -регистр, л-ервый бло-к вычитал ия и третий реги-стр, причем второй вход первого блока вычитания подключен к выходу первого регистра, о т л и ч а ю щ и йс я тем, что, с целью повыщепия точности работы преобразователя, в него введен второй блок вычитания и последовательно соединенные четвертый регистр, первый комбинационный сумматор, второй комбинационный сумматор, второй накапливающий сумматор, третий комбинационный сумматор и четвертый комбинационный сумматор, второй вход которого подключен к выходу второго регистра, нервый вход второго блока вычитания соединен с выходом четвертого регистра, второй вход - со вторым входом иервого комбинационного сумматора, входом четвертого регистра н выходом третьего регистра, а выход - со вторым входом первого накапливающего сумматора, иодключенного выходом ко вторым входам второго и третьего комбинационных сумматоров, а второй вход второго накапливающего сумматора соединен с выходом синхронизатора.

Источники инфор|Маци:И, л.ридятые во внимаиие лри экспертизе:

1.Авторское св(идетельство СССР ЛЬ 437098, кл. G 06 G 7/30, 1972.

2.Авторское свидетельство СССР ЛЬ 302722, кл. G 06 G 7/30, 1970.

3.Патент США N° 3846625, кл. 235-152, опублик. 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для воспроизведения функций | 1988 |

|

SU1532945A1 |

| Цифровой кубический интерполятор | 1979 |

|

SU849227A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Устройство для умножения | 1977 |

|

SU662939A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для решения интегральных уравнений | 1987 |

|

SU1446619A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

Авторы

Даты

1980-10-07—Публикация

1979-01-04—Подача