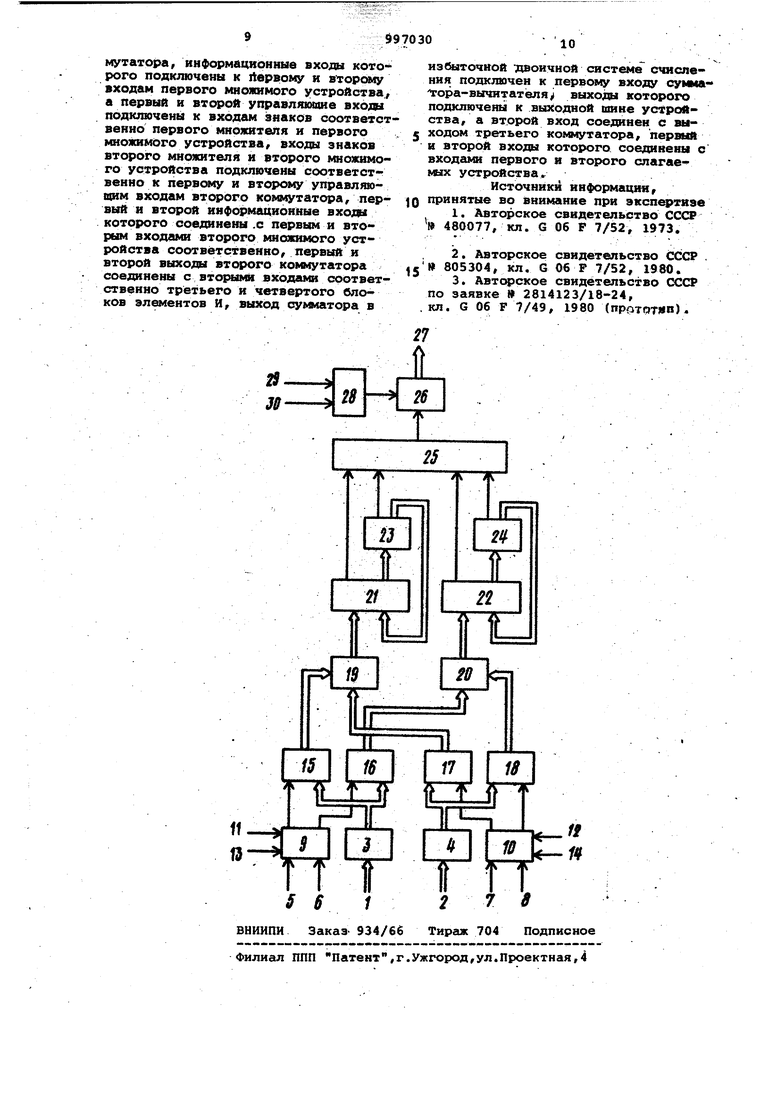

го и второго сумматоров результата выходы разрядов которых соединены входами соответственно первого и вт рого регистров результата, выходами старшего разряда подключенных ко втор входам первой и второй rpyrfn сумматора в избыточной двичной системе счисления, выходы которого подключены ко входам устройства. Устройство производит умножение двух чисел, одно из которых представлено в избыточной двоичной системе счисления, -а другое - двоичным кодом, и имеет высокое быстродействие так как пронзведение выводится посл довательным кодом, начиная со старшего разряда, в процессе вычисления З. . Недостатком данного устройства является сложность алгоритма умножения, что вызывает большие аппаратурные затраты и получение только . одного произведения. Цель изобретения - упрощение уст ройства и расширение его функциональных возможностей за счет получения суммы нескольких произведений Поставленная цель достигается т что вычислительное устройство, сддержащее регистр первого множителя входы которого подключены к шине первого множителя устройства, перв и второй блоки элементов И, первые входы которых подключены к выходам регистра первого множителя, первый и второй сумматоры результата, пер вый и второй регистры результата, входы которых соединены с выходами соответственно первого и ii oporp сумматоров результата, первые вхо ды разрядов которых с второго по (п+1)-й (п - число разрядов множителя) подключены к выходам п младших разрядов соответственно первого и второго регистров результата, и сумматор в избыточной двоичной сис теме счисления, первый и второй вхо да которого подключены к выходам переноса соответственно первого и второго сумматоров результата, а третий и четвертый входы подключены к выходам старшего (п+1)-го раз ряда соответственно первого и второго регистров результата, содержит регистр второго множителя, три ком мутатора, третий и четвертый блоки элементов И, два комбинационных сум тора, и сумматор-вычитатель, причем шина второго множителя устройства подключена к входам регистра второ го множит еля, выходы которого соеди иены с первыми входами третьего и четвертого блоков элементов И, выходы которых подключены к первым входам соответственно первого и вто рого комбинационных сумматоров, выходы которых подключены к вторым входам соответственно первого и второго сумматоров.результата, а вторые входы первого и второго комбинационных сумматоров соединены с выходами соответственно первого и второго блоков элементов И, вторые входы которых подключены соответственно к первому и второму выходам первого коммутатора, информационные входы которого подключены к первому и второму входам первого множимого устройства, а первый и второй управляющие входы подключены к входам знаков соответственно первого множителя и первого множимого устройства, входы знаков второго множителя и второго множимого устройства подключены соответственно к первому и второму управляющим входам второго коммутатора, первый и второй информационные входы KOTOpioго соединены с первым и вторым входами второго множимого устройства соответственно, первый и второй выходы второго коммутатора соединены с вторыми входами соответственно третьего и четвертого блоков элементов И, .выход сумматора, в избыточной двоичной системе счисления подключен к первому входу сумматора-вычитателя, выходы которого подключены , к выходной шине устройства, а второй вход соединен с выходом третьего коммутатора, первый и второй входы которого соединены со входами первого и второго слагаемых устройства. На чертеже приведена структурная схема устройства. Устройство содержит шины 1 и 2 первого и второго множителей, регистры 3 и 4 первого и- второго множителей, входы 5 и 6 первого множимого, входы 7 и 8 второго множимого, первый и второй коммутаторы 9 и 10, входы 11 и 12 знаков первого и второго множителей устройства, входы 13 и 14 знаков первого и второго множимых устройства, .первый, второй, третий и четвертый блоки элементов И 15-18, комбинационные сумматоры 19 и 20, сумматоры результата 21 и 22, регистры результата 23 и 24, сумматор 25 в избыточной двоичной системе счисления, сумматор-вычитатель 26, выходную шину 27, третий коммутатор 28, входы 29 и 30 Ъервого и второго слагаемых. Шины 1 и 2 множителей устройства соединены со входами регистров 3 и 4 первого и второго множителей, входы 5 и 6 первого множимого и входы 7 и 8 второго множимого устройства подключены к информационным входам соответственно первого и второго коммутаторов 9 и 10, первые управляющие входы которых соединены со входами 11 и 12 знаков соответственно первого и второго множителей устройства, а вторые управляющие

входы соединены со входами знаков 13 и 14 соответственно первого и второго множимых устройства. Выходы регистра 3 первого множителя подключены к первым входам первого и второго блоков элементов И 15 и 16, вторые входы которых соединены соответственно с первым и вторым выходам первого коммутатора 9. Выходы регистра 4 второго множителя соединены с первыми входами третьего и четвертого блоков элементов И 17 и 18, вторые входы которых подключены соответственно к первому и второму выходам второго коммутатора 10. Выходы первого и второго блоков элементов И 15 и 16 соединены с первыми входами соответственно первого и второго комбинациовных сумматоров 19 и 20, вторые входы которых подклЕйчены к выходам соответственно третьего и четвертого блоков элементов И 17 и 18. Выходы первого и второго комбинационных сумматоров 19 и 20 подключены ко вторым входам соответственно первого и второго сумматоров результата 21 и 22, первые входы которых соединены с выходами, п младших разрядов соответственно первого и второго регистров результата 23 и 24, входы которых подключены к выходам соответственно первого и второго сумматоров результата 21 и 22. Выходы переноса первого и второго сумматоров результата 21 и 22 подключены соответственно к первому и второму входам сумматора 25 в избыточной двоичной системе счисления, третий и четвертый входа которого соединены с выходами старшего разряда соответственно первого и второго регистров результата 23 и 24. Выход сумматора 25 подключен к первому входу сумматора-вычитателя 26, выходы которого подключены к выходной, шине 27 устройства, а второй вход соединен с выходом третьего коммутатора 28, первый и второй входы которого соединены со. входами 29 и 30 первого и второго слагаемых

устройства. I .

Устройство работает следующим образом.

В начальном такте работы регистры 23 и 24 результата сбрасываются в нулевое состояние, а в регистры 3 и 4 множителей по шинам 1 и 2 устройства заносятся значения первого и второго множителей параллельным двоичным кодом. Знаки множителей со входов 11 и 12 устройства подаются на первые управляющие входы соответственно первого и второго коммутаторов 9 и 10 и остаются на входах устройства до окончания цикла умножения. Значения множимых последовательным кодом, начиная со старшего

разряда, подаются со входов 5,6 и 7, 8 устройства на информационные входы первого и второго коммутаторов 9 и 10. Если перемножаются числа, выраженные в двоичной позиционной системе счисления, то вход 5 устройства объединяется со входом 6 а вход 7 - со входом 8. Если множикие выражены;;- в избыточной двоичной системе счисления (цифрами 1,0,

1), Фо входа 13 и 14 знаков множикшх устройства объединяются со вто{яями (отрицательными) входами 6 и 7 соответственно первого и второго множи 1ых устройства. Алгоритм вычисления

суммыJ poиэвeдeний основан на формуле

; i S-A-B+C-D, .

где А и С - первое и второе мн6жи- мие;

В и D - первый и второй множители.

Если в К-м такте (К 1,2,...,N) работы К-й разряд первого или второго множимых равен нулю, то на выходы первого коммутатора 9 выдается нулевая информация, и соответственно на входы первого и второго комбинационных сумматоров 19 и 20 также поступает нулевая информация.

Если в К-м такте работы К-й раз|РЯД первого множимого равен единице, то с первого и второго выходов коммутатора 9 щ зависимости от соотношения знаков множителя и множимого подается единица на вторые входы элементов И блока 15 (если знаки совпадают) или блока 16 (если знаки не совпадают), Блоки 15 и 16 элементов И осуществляют перемножение значений К-го разряда первого множимого А на значение первого множителя В. Если iSignA SignB i, т.е. перемножгиотся числа с. разными знаками, то код

множителя В с выходов регистра 3 через блок 16 элементов И поступает на первые входы второго комбинационного сумматора 20. Если SignA-SignB 0, т.е. перемножаются числа с одинаковыми знаками, то код множителя В с

выходов регистра 3 через блок 15 элементов И поступает на первые входы первого комбинационного сукматора 19. Аналогично происходит работа коммутатора 10 и блоков элемен- ; тов И 17 и 18, которые осуществляют перемножение значений К-го разряда второго множимого С на значение второго множителя D.

.. .

Комбинационные сумматоры 19 и 20 суммируют соответственно положительные и отрицательные значения произведений п-го разряда множимых А и 6

на значения множителей С-и D:

(ЛцЬ H sig MA-Si gfvibneigyi А В+Сц и-н/та sig iA-SiQyibvisigMC-s g T);

6 к. tt siQIi A tSrtgT В V SigH с - siQTiD i О «ути. Sto A Ф sigvi В M С t

( АцВ tv V A sigTi В и sigT C sigHD; C-; j AxBf CitD it/vu- sigfVi A -Sign Ви CtS-igViD I -K V S S S С t sigfn D ; I 0 1уйс. A ) Bи С 5 .

«.-Полученные в сумматорах 19 и 20 значения сумм S и Sj подаются ,на вторые входы (п+1)-разрядных сумматоров результата 21 и 22, на .первые входы разрядов которых со второго по (п+1)-и с выходов п младших разрядов (п+1)-разрядных регистров результата 23 и 24 подаются значения п.младших разрядов (K-l)-ro частичного результата, полученные в пре дыдушем (К-1)-м такте работы. Значение старшего (п+2)-го разряда К-го частичного результата с выходов переноса сумматоров 21 и 22 поступает на первый (положительный) и третий (отрицательный) входы сумматора 25 в избыточной двоичной системе счисления, образуя первое число а, которое суммируется со вторым числом Ь, образуемым значением (п+1)го разряда (K-l)-ro частичного результата, которое подается на второй (положительный) и четвертый (отрицательный) входы сумматора 25 с выходов старшего (п+1)-го разряда регистров результата 23 и 24. Значения (п+1) младших разрядов К-го час тичного результата с выходов сумматоров 21 и 22 заносятся в регистры результата 23 и 24.

Полученное- значение К-го разряда суммы произведений S поступает на первый вход сумматора-вычислителя 26 на второй вход которого через коммутатор 2.8 со входов 29 и 30 устройства подается последовательным кодом, начиная со старшего разряда, значение слагаемого F, которое может быть суммой произведений, накапливаемой во внешнем запоминающем устройстве. На выходную шину 27 устройства подается значение результата Z F ± S в избыточной двоичной системе счисления последовательньам кодом, старшими, разрядами вперед.

Данное устройство может применяться не только для вычисления суммы произведений, но и выполнять другие функции:

(AB+CT)); 7,j,P±AB; .Z,,F-t(); Z4::F4(A+C)

и т.д.

Кроме того, данное устройство может работать с комплексными числами.

например, при вычислении коэффици.ентов Фурье;

Re(ACi,K)K,--RgAa)Kt. iERe Vfte 3 AtK),Л(.,К)(3)к.4 , ± l-Re A(lc)icDv«w Dy,,A Cn)icReW. Таким образом, данное устройство имеет более широкие функциональные возможности и требует меньших аппаратурных затрат, чем прототип.

Формула изобретения

Вычис тйтельное устройство, содержащее регистр первого множителя, входы которого подключены к шине первого множителя устройства, первый и второй блоки элементов И, первые входы которых под слючены к выходам регистра первого множителя, первый и второй сумматоры результата, первый и второй регистры результата, входы которых соединены с выходами соответственно первого и второго сумматоров результата, первые входы разрядов которых с второго по (п+1)-и (п - число разрядов множителя) подключены к выходам п младших разрядов соответственно первого и второго регистров результата, и сумматор в избыточной двоичной системе счислений, первый и второй входы которого подключены к выходам переноса соответственно первого и второго сумматоров результата, а третий и четвертый входы подключены к выходам старшего (п+1)-го разряда соответственно первого и второго регистров результата, отличающееся тем, чао, с целью упрощения устройства и расширения его функциональных возможностей за счет вычислений

суммы нескольких произведений, оно содержит регистр второго множителя, три коммутатора, третий и четвертый блоки элементов И, два комбинационных сумматора и сумматор-вычитатель, причем шина второго множителя устройства подключена к входам регистра второго множителя, выходы которого соединены с первыми входами третьего и четвертого блоков элементов И, выходаз которых подключены к первым входам соответственно первого и второго комбинационных сумматоров, выходы которых подключены к вторьш входам соответственно первого и второго сумматоров результата,а вторые вхо-

0 ды первого и второго комбинационных сумматоров соединены с выходами со;ответственно первого и второго блоков элементов И, вторые входы которых подключены соответственно к пер5 вому и второму выходам первого коммутахора, информбциоиные входы которого подключены к Лервому и второму входам первого множимого устройства., а первый и второй управляющие входи подключены к входам знаков соответственно первого множителя и первого множимого устройства, входы знаков второго множителя и второго множимого устройства подключены соответственно к первому и второму управляющим входам второго коммутатора, первый и второй информационные вхояа которого соедшнены .с первым и вторым входами второго мноаюоюго устройства соответственно, первый и второй выходы второго коммутатора соединены с вторы « входами соответственно третьего и четвертого блоков элементов И, выход суьматора в

избыточной -двоичной системе счисления подключен к первсжу входу сумма Тора-вычитатёля выходы которого подключены к выходной шине устройства, а второй вход соединен с вы5 ходом третьего коммутатора, первый и второй входы которого соединены с входами первого и второго слагаемых устройства

Источники информации, JQ принятые во внимание при экспертизе

1.Авторское свидетельство CCCf 480077, кл. G 06 F 7/52, 1973.

2.Авторское свидетельство СССР . ,5 805304, кл. G 06 Р 7/52, 1980.

3.Авт( свидетельство СССР по заявке 2814123/18-24,

. кл. G 06 F 7/49, 1980 (протаТЯП).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для вычисления суммы произведений | 1981 |

|

SU978144A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Устройство для умножения | 1979 |

|

SU960804A1 |

| Устройство для умножения | 1981 |

|

SU991414A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

Авторы

Даты

1983-02-15—Публикация

1981-07-06—Подача