OtmcHou

В

лиавз la

BtilXOd

42

1А466

рой блок 6 элементов И, функциональный преобразователь 7, третий блок 8 элементов И, первый элемен т ИЛИ 9, четвертый блок 10 элементов И, блок 11 элементов ИЛИ, блок 12 памяти, элемент И 13, элемент 14 задержки, второй элемент ИЛИ 15, пятый блок 16 элементов И, второй накапливающий сумматор 17, шестой блок 18 элементов И, второй блок сравнения 19, первый блок элементов НЕ 20, первый комбинационный сумматор 21, блок 22 возведения в степень, второй комби19 национный сумматор 23, регистры 24,

25первого и второго параметров,блок

26вычисления обратной величины, первый умножитель 27, третий накапливающий сумматор 28, второй умнолситель 29, второй блок элементов НЕ 30,седьмой блок 31 элементов И, третий комбинационный сумматор 32, блок 33 деления, регистр 34 третьего параметра, блок 35 синхронизации. Цель достигнута за счет замены исходного уравнения эквивалентным и решением его квадратурным методом. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения интегрального уравнения измерительного преобразователя скорости потока | 1989 |

|

SU1651283A1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Устройство для решения линейных интегральных уравнений Вольтерры | 1983 |

|

SU1124322A1 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ ОРТОГОНАЛЬНЫХ СОСТАВЛЯЮЩИХ ГАРМОНИЧЕСКОГО НАПРЯЖЕНИЯ ИЗВЕСТНОЙ ЧАСТОТЫ | 1991 |

|

RU2010241C1 |

| Устройство для нахождения оптимального вектора решения системы линейных неравенств | 1985 |

|

SU1315996A1 |

| Устройство для формирования фигур конического сечения на экране электронно-лучевой трубки | 1981 |

|

SU991489A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Генератор случайных чисел | 1988 |

|

SU1509885A1 |

Изобретение относится к вычислительной технике и может быть ис пользовано как специализированный вычислитель для решения слабосингулярных интегральных уравнений. Цель изобретения - расширение функциональных возможностей за счет решения уравнений со слабосингулярным ядром. Устройство содержит регистр 1 верхней границы интегрирования, пер вый блок 2 сравнения, регистр 3 величины шага, первый блок А элементов И, первьш накапливакщий сумматор 5, вто

1

Изобретение относится к цифровой вычислительной технике и может быть использовано как специализированное вычислительное устройство для решения задачи автоматизации экспериментальных исследований на основе реализации слабосингулярных интегральных уравнений.

Цель изобретения - расширение функциональных возможностей за счет решения уравнений со слабосингулярным ядром.

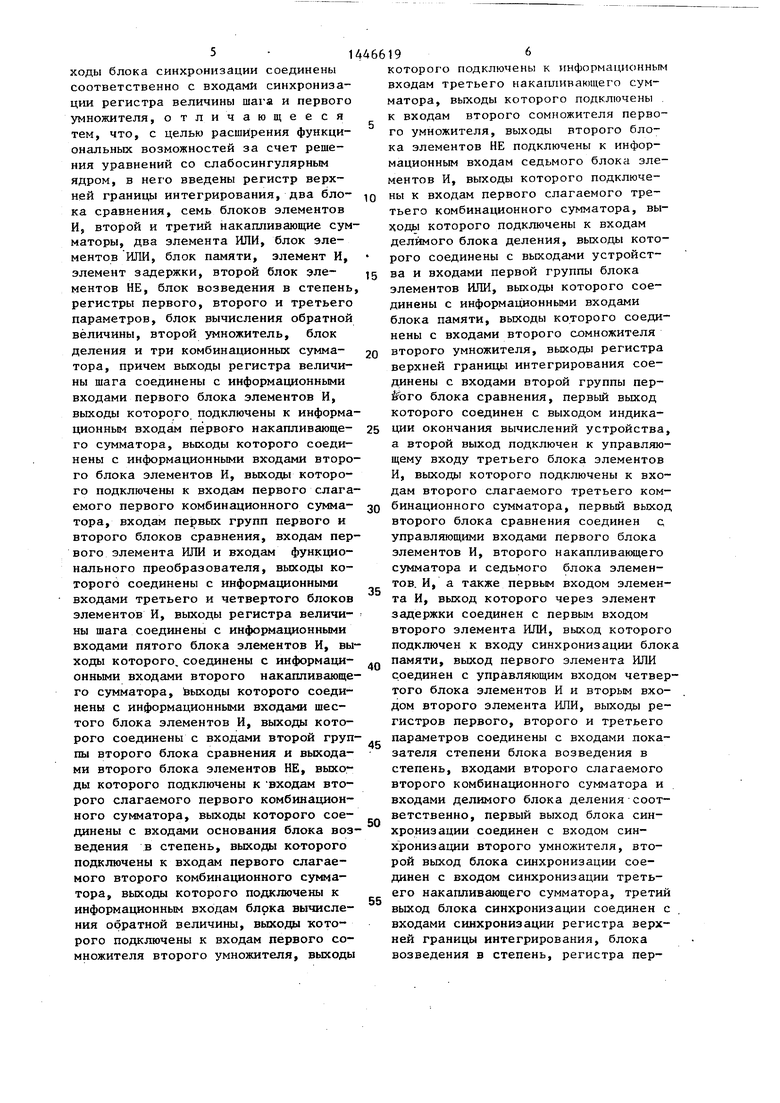

На чертеже показано предлагаемое устройство.

Устройство состоит из регистра 1 верхней границы интегрирования, первого блока 2 сравнения, регистра 3 величины шага, первого блока элементов И 4, первого накапливающего сумматора 5, второго блока элементов И 6s функционального преобразователя 7 третьего блока элементов И 8, первого элемента ИЛИ 9, четвертого блока элементов И 10, блока элементов ИЛИ 11, блока 12 памятиf элемента И 13, элемента 14 задержки, второго элемента ИЛИ 15, пятого блока элементов И 16, второго накапливающего сумматора 17, шестого блока элементов И 18, второго блока 19 сравнения, первого блока элементов НЕ 20, первого комбинационного сумматора 21, блока 22 возведения в степень, второго комбинационного сумматора 23, регистра 24 первого параметра, регистра 25 второго параметра, блока 26 вычислений обратной величины, умножителя 27

третьего накапливающего сумматора 28, умножителя 29, второго блока элементов НЕ 30, седьмого блока элементов И 31, третьего комбинационного сумматора 32, блока 33 деления, регистра 34 третьего параметра и блока 35 синхронизации, выполненного в виде по следовательно соединенных тактового генератора 36, счетчика 37 импульсов

и дешифратора 38.

Устройство решает сингулярное интегральное уравнение Вольтерра второго рода

y(S)(t), (1)

где О ;о(1 - некоторое, реальное число;

f(t) - известная функция , y(t) - неизвестная функция

K(t)

1/(t-S) - сингулярное ядро интегрального уравнения, которое несет информацию об исследуемом объекте.

Непосредственное применение метода квадратурных формул для решения интегрального уравнения типа (1), которое является сингулярным, исклю- чается.

Поэтому уравнение (1) преобразовано к виду

35

р

fTirp y .2)

где - параметр внутренней регуляризации. Как видно из выражения (2),

314466

на основе применения параметра регуляризации f получено интегральное уравнение с регулярным ядром, которое допускает непосредственное применение метода квадратурных формул. Расчетные выражения, полученные при этом на основе метода квадратурных формул,, имеют вид

ly(t,)(t.)Гн 1

I 0; J

I: /.(tl-t.

j-1 j

U4e- A:

Задача определения параметра регуляризации р является сложной и трудоемкой. Для определения значения р существует ряд способов. Среди них способ модельных примеров является эффективным средством решения интегральных уравнений Вольтерра,

Перед началом работы устройства в регистр 1 заносится величина верхней границы интегрирования, в регистр 3 заносится величина шага, в регистр 24 заносится величина пара- метра d , в регистр 25 заносится величина регуляризирующего параметра (Ь, в регистр 34 заносится величина

4Устройство начинает функционировать с момента подачи команды запуска на вход тактового генератора. Последовательность импульсов, вьфа- батываемая тактовым генератором, поступает на вход счетчика импульсов, который работает в режиме суммирования с модулем равным пяти. Кодовая Комбинация с выхода счетчика анализируется дешифратором 38, ко- торый вьщеляет каждьй тактовый им- пул ьс на один из своих пяти выходов циклически с модулем, определяемая счетчиком 37. Частота и скважность импульсов тактового генератора опре- деляется длительностью вычислительных процессов, происходящих за один такт. ,

Рассмотрим i-й цикл работы устройства. В первом такте по сигналу управления с шины 43 .депшфратора 38 в первом блоке 2 сравнения выполняется сравнение переменной t с верхней границы интегрирования, в функ

циональном преобразователе 7 вычисляется значение функции f(t ;) , во втором блоке 19 сравнения выполняется сравнение переменной t; с переменной tj, на выходе блока 22 возведения в степень устанавливается величина (t; -t ) .,

Во втором такте по сигналу управления с шины 39 дешифратора 38 на выходе второго комбинационного сум матора 23 устанавливается величина (b+(.;), а на выходе блока 26 вычисления обратной величины уста- навливается величина (t j-t j) .

В третьем такте по сигналу управления с шины 40 дешифратора 38 в накапливающих сумматорах 5 и 17 вычисляются следующие значения соот- ветст венно переменных t , и tj , а на вьсходе у шожителя 29 устанавливается величина y(t j)/ +(t ). В четвертом, такте по сигналу управления с шины 41 дешифратора 38 величина y(tj)/ /fi + (t .-t ) суммируется с содержимым третьего накапливающего сумматора 28, а на выходе умножителя 27 устанавливается величина h- y(t )/fV+(t(-tj)4

в пятом такте по сигналу управления с 42 дешифратора 38 срабатывает третий комбинационный сумматор 32, на его выходе устанавливается величина

y(t)f(t,)(t.).

На выходе блока 33 деления устанавливается величина

- 1

Р

y(t;)

1

„ijt. - |,it,-ti)

которая записывается в блок 12 памяти магазинного типа.

Формула изобретения

Устройство для решения интегральных уравнений, содержащее регистр величины шага, первый накапливающий сумматор, функциональный преобразователь, первый умножитель, первый блок элементов НЕ и блок синхронизации, причем выходы регистра величины шага соединены с входами первого сомиожи- теля первого умножителя, выходы которого соединены с входами первого блока элементов НЕ, первый и второй выходы блока синхронизации соединены соответственно с входами синхронизации регистра величины шага и первого умножителя, отличающееся тем, что, с целью расширения функциональных возможностей за счет решения уравнений со слабосингулярным ядром, в него введены регистр верхней границы интегрирования, два блока сравнения, семь блоков элементов И, второй и третий накапливающие сумматоры, два элемента ИЛИ, блок элементов ИЛИ, блок памяти, элемент И, элемент задержки, второй блок элементов НЕ, блок возведения в степень регистры первого, второго и третьего параметров, блок вычисления обратной величины, второй умножитель, блок деления и три комбинационных сумматора, причем выходы регистра величины шага соединены с информационными входами первого блока элементов И, выходы которого подключены к информационным входам первого накапливающего сумматора, выходы которого соединены с информационными входами второго блока элементов И, выходы которого подключены к входам первого слагаемого первого комбинационного сумматора, входам первых групп первого и второго блоков сравнения, входам первого элемента ИЛИ и входам функционального преобразователя, выходы которого соединены с информационными входами третьего и четвертого блоков элементов И, выходы регистра величины шага соединены с информационными входами пятого блока элементов И, выходы которого, соединены с информационными входами второго накапливающего сумматора, выходы которого соединены с информационными входами шестого блока элементов И, выходы которого соединены с входами второй группы второго блока сравнения и выходами второго блока элементов НЕ, выхо ды которого подключены к входам второго слагаемого первого комбинационного сумматора, выходы которого соединены с входами основания блока возведения в степень, выходы которого подключены к входам первого слагаемого второго комбинационного сумматора, выходы которого подключены к информационным входам блока вычисления обратной величины, выходы которого подключены к входам первого сомножителя второго умножителя, выходы

5

0

5

0

5

0

5

0

5

которого подключены к ннформацнсжным входам третьего накагшнвающего сумматора, выходы которого подключены к входам второго сомршжителя первого умножителя, выходы второго блока элементов НЕ подключены к информационным входам седьмого блока элементов И, выходы которого подключены к входам первого слагаемого третьего комбинационного сумматора, выходы которого подключены к входам делимого блока деления, выходы которого соединены с выходами устройства и входами первой группы блока элементов ИЛИ, выходы которого соединены с информационными входами блока памяти, выходы которого соединены с входами второго сомножителя второго умножителя, выходы регистра верхней границы интегрирования соединены с входами второй группы пер- йЪго блока сравнения, первьй выход которого соединен с выходом индикации окончания вычислений устройства, а второй выход подключен к управляющему входу третьего блока элементов И, выходы которого подключены к входам второго слагаемого третьего комбинационного сумматора, первый выход второго блока сравнения соединен с; управляющими входами первого блока элементов И, второго накапливающего сумматора и седьмого блока элементов. И, а также первым входом элемента И, выход которого через элемент задержки соединен с первым входом второго элемента ИЛИ, выход которого подключен к входу синхронизации блока памяти, выход первого элемента ИЛИ соединен с управляющим входом четвертого блока элементов И и вторым входом второго элемента ИЛИ, выходы регистров первого, второго и третьего параметров соединены с входами показателя степени блока возведения в степень, входами второго слагаемого второго комбинационного сумматора и входами делимого блока деления соответственно, первый выход блока синхронизации соединен с входом синхронизации второго умножителя, второй выход блока синхронизации соединен с входом синхронизации третьего накапливающего сумматора, третий выход блока синхронизации соединен с входами синхронизации регистра верхней границы интегрирования, блока возведения в степень, регистра первого параметра и управляющими входами второго и шестого блоков элементов И, четвертый выход блока синхронизации . соединен с входами синхронизации регистра параметра и блока вычисления обратной величины, пятый выход блока синхронизации соединен с входами синхронизации блока делеСоставитель А.Чеканов Редактор А.Ворович Техред л.ОлийныкКорректор М.Максимишинец

Заказ 6748/53

Тираж 704

ВНИШШ Государственного конитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

ния и регистра третьего параметра, управляющим входом седьмого блока элементов И и вторым входом элемента И, входы верхней грани1у 1 интегрирования, величины шага, первого, второго и третьего параметров устройства соединены с информационными входами соответствующих регистров.

Подписное

| Устройство для решения линейных интегральных уравнений Вольтерры | 1985 |

|

SU1290311A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1099755, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-23—Публикация

1987-05-04—Подача