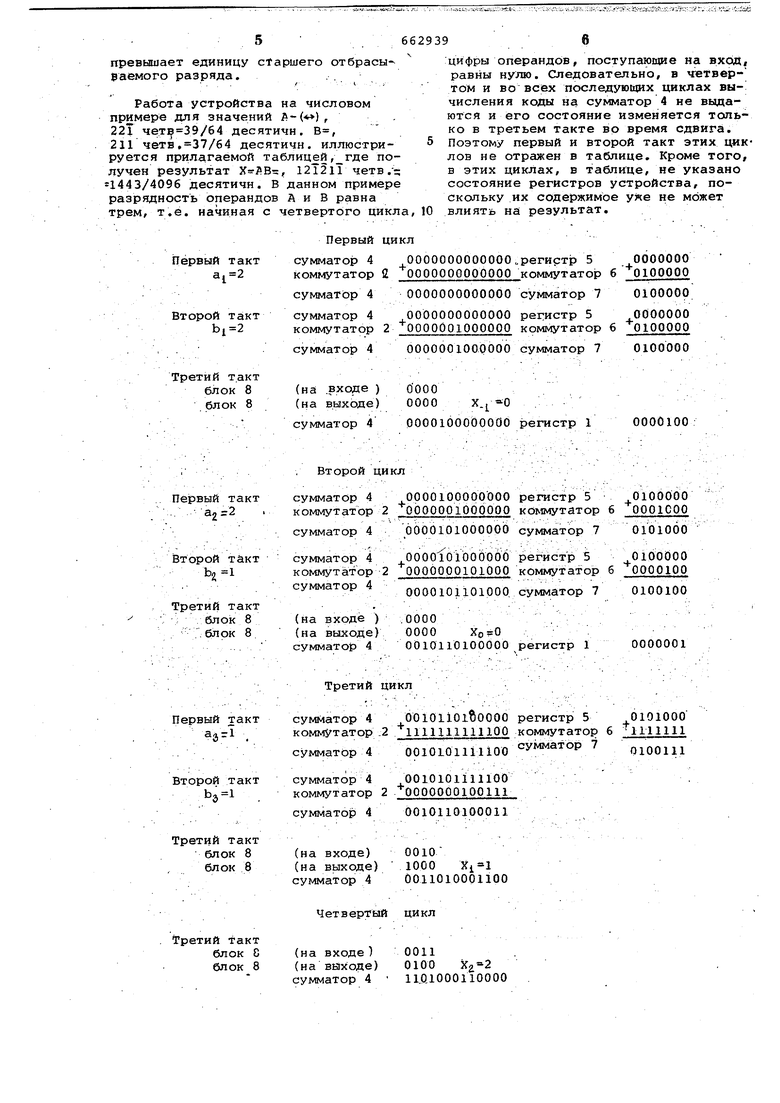

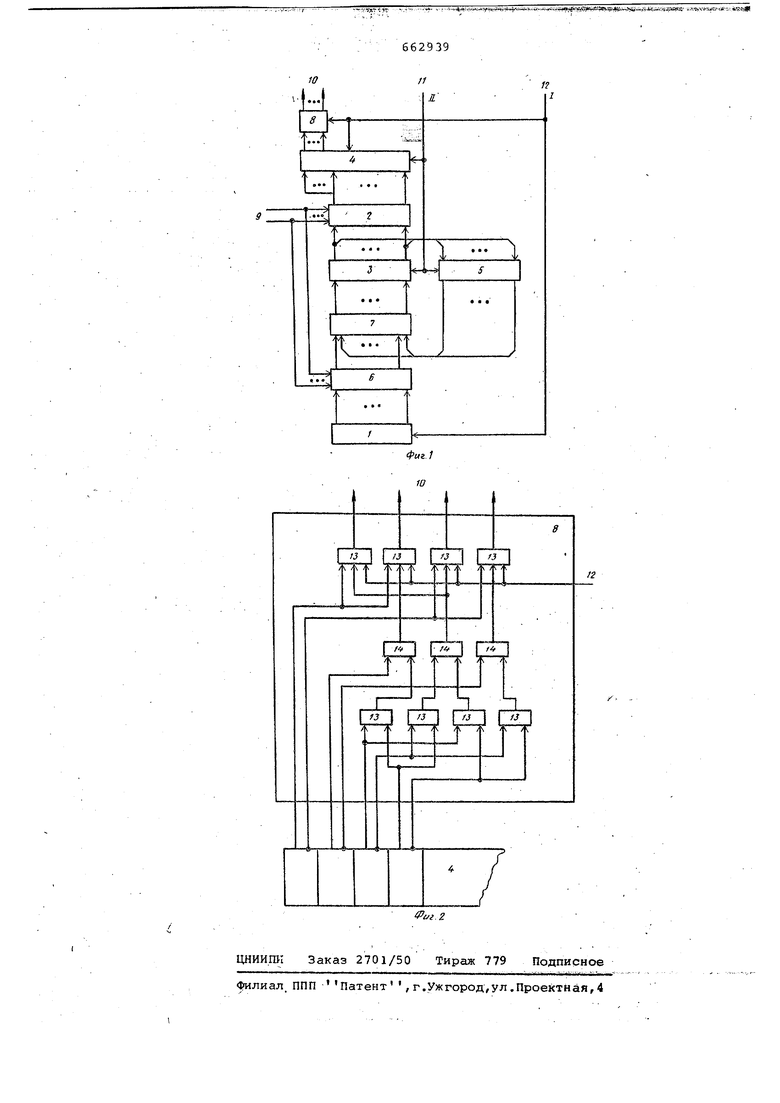

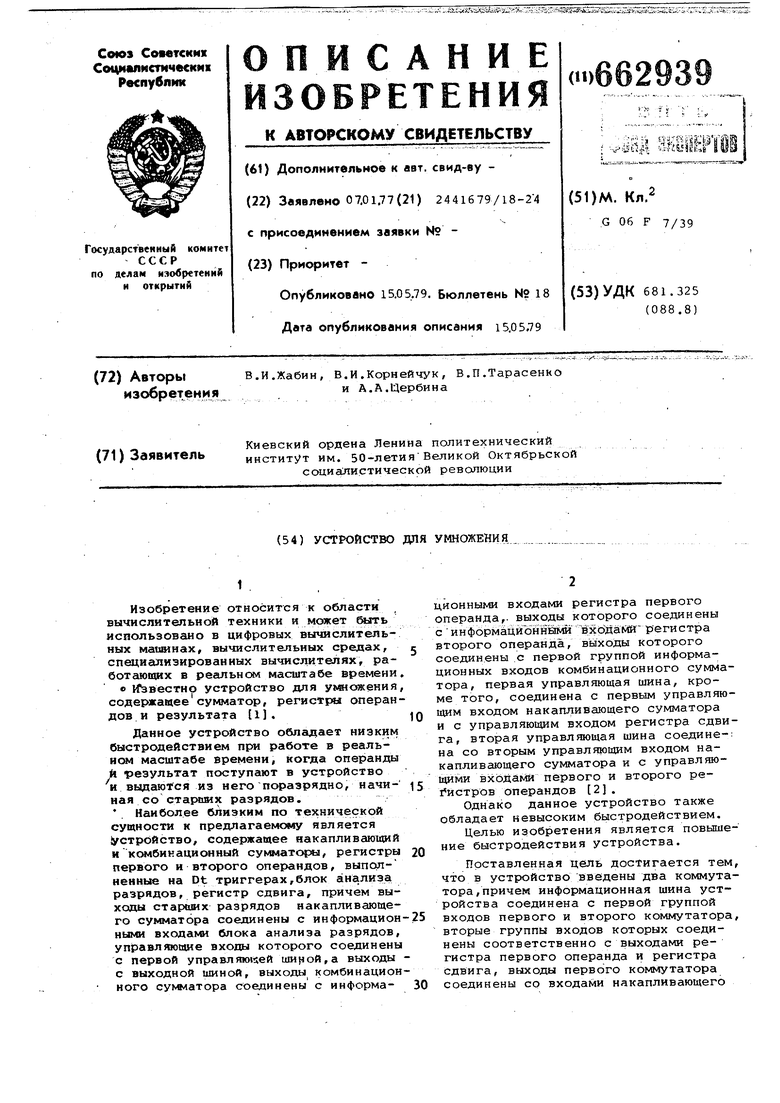

(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ сумматора, причем выход первого раз ряда первого коммутатора соединен со входами первых шести разрядов накапливающего.сумматора, выходы вт рого коммутатора соединены со второ группой информационных входов комбинационного сумматора. На фиг.1 приведена структурная с ма устройства умножения, на фиг.2 пример выполнения блока анализа раз рядов. Устройство содержит сдвигающий регистр 1, первый коммутатор 2, регистр первого операнда 3, накаплива Ю1ЦИЙ сумматор 4, регистр второго оп ранда 5, второй коммутатор 6, комби национный сумматор 7, блок анализа разрядов 8, входную шину 9, выходну шину 10, первую 11 и вторую 12 упра ляющие шины, элементы И 13 и ИЛИ 14 входящие в состав блока анализа-раз рядов 8. В предлагаемом устройстве сомножители А и В и результат X представ лены в избыточной :позиционной однородной системе счисления с основани 4 и естественным порядком весов, .т. . CV/2 . А 1а;4- - , i,b,-, Ч/2 X-,r xi4-V где цифры ai Ь; хj 2,1,0,1,2. . На входных шинах 9 и выходных шинах 10 применено Пространственное кодирование. Наличие единицы на шине .: .1,2,3,4 соответствует соотвётственн цифрам 1,2,1,2. Нулю сортв етствуёт, отсутс вйе сигнала на всех шинах. Вычисления в устройстве ведутся п следующему алгоритму: ; ; Исходное с:ос;тЬяние: . (4) в каждом 1-м цикле: Первый такт: i - . . .f4-2oiBi.i . (5) . А,- А,-. + 4-а; Второй такт: Н- н;. , , - 1 Ь,В.,.4-Ъ хретий тактЧ , если Hj --1,1 I, если -1, -0,1 i-zHO если -0,,,1 1, если О , li Н; -i 1,1 2, если 1, 12. если 1. (н,--х;.(10) где h и Bj - сомножители А и В, пре ставленные только i старшими разряда ми. : . ,,;; в ИСХОДНОМ состоянии, в соответст вии с (4), в регистрах 3 и 5 и в сум .маторе 4 записаны нули. При каждом i-M цикле вычисления регистре 1 единица находитсяв (21+1)-м.разряде, т.е. в нем записано число , . В первом такте по сигналу в синхронизирующей шине 11 на входные шины 9 принимается цифра а,, т.е. :-1-я после запятой цифра сомножителя А. Она поступает на управляющие входы комму 1татора 2 и, в зависимости от того, какое значение 1, I, 2 или 2 прини мает , на сумматор 4 выдается прямой, дополнительный, удвоенный прямой или удвоенный дополнительный код .числа ,хранящийся в этом такте на .регистре 3. Одновременно с этим цифра а, с помощью коммутатора 6 управляет аналогичньпи образом выдачей на сумматор 7 кода регистра 1. Таким обpaiaOM, после снятия сигнала в шине 11, 5 соответствии с (5) и (6) на сумматоре 4 образуется код н|, в регист-. .ре 3 код i J , а в регистре 5 - кодВ(-1, Второй такт аналогичен первому. В этом такте по сигналу в шине 11 на входные шины 9 поступает цифра bi, т.е. i-я после Запятой цифра сомножителя В, В результате, после снятия сигнала в шине 11, на сумматоре 4 и в регистре 3 получаем Н и Bj, в соответствии с (7) и (8), а в регистр 5, как и в первом такте; перезаписывается код с выходов регистра 3, в данном случае Af. В третьем такте, по сигналу в maHie 12, блок анализа разрядов 8 в соответствии с (9) .формирует и видает на выходные шины 10 очередную цифру результата х |-2. После.снятия сигнала в шийе 12 единица в регистре 1 оказывается сдвинутой на два разряда вправо, а в сумматоре 4 получаем число Ri (iO)« Вычитание х .|.2 из содержимого сумматора 4 Н| при этом сЬвйёЫёно во времени сЬ сдвигом. Нет эУдно убедиться, что на сумматоре 4 будет получен тот же результат R, есливместо непосредственного вы-читания .,-2 приёдвйге в первый разряд сумматора 4 переписывать значение не с третьего, а с четвертого разряда. В предлагаемом устройстве задержка появления старшей цифры результата на выходе составляет два цикла, т.е. Дляполучения точного резуЛьтаг Та умножения двух j /2-разрЯдных чисел необходимо выполнить циклов вычисления (как известно, точный результат умножения двух q/2-разрядных чисел содержит разрядов). Если е достаточно (/2 старших разрядов результата, то для этого необходимо вьтолнить циклов. В общем случае, устройстве:) дает возможность ычислять результат с- произвольной азрядностью S/2 {(J/26 S/2 q. ). Для того нужно выполнить 2+В/2 цикЛов ычисления. ;При этом погрешность не

превышает единицу ctapmero отбрасы раемого разряда. ..

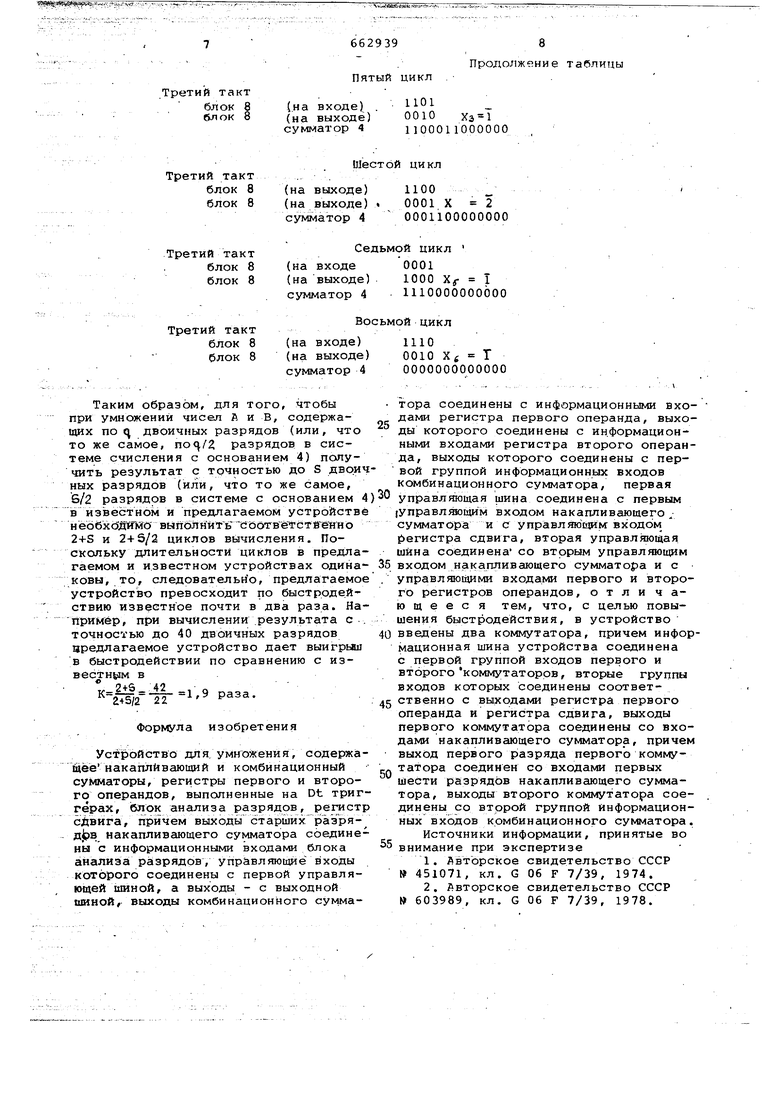

- , -/ . - . Работа устройства на числовом примере для значений f(f . 221 чет 39/64 десятичн. В, 211 четв,37/64 десятичн. иллюстрируется прилагаемой таблицей, где получен результат , 1212ll четв.-1443/4096 десятичн. В данном примере разрядность операндов А и В равна трем, т.е. начиная с четвертого цикл

цифры операндов, поступающие на вхоД, равны нулю. Следовательно, в четвертом и во всех последующих циклах вычисления коды на сумматор 4 не выдаются и его состояние изменяется только в третьем такте во время сдвига. Поэтому первый и второй такт этих циклов не отражен в таблице. Кроме того, в этих циклах, в таблице, не указано состояние регистров устройства, поскольку их содержимое уже не может влиять на результат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный | 1985 |

|

SU1300641A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1973 |

|

SU409222A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

первый такт

Второй такт

Третий такт блок 8 блок 8

Первый такт .. а2 2

Второй такт bjj 1

Третий такт

блок 8 блок 8 Третий цикл сумматор 400101101 0000 Первый такт коммутатор .21111111111100 3- . сумматор 40010101111100 сумматор 4OOlOlOliillOO Второй такт коммутатор 20000000100111 . сумматор 40010110100011

(на входе) (на выходе) сумматор 4

Четвертый цикл

(на входе ) (на выходе) сумматор 4

0010

1000

OOllOlOOOllOO

ООН

0100

(на входе) (на выходе) су лматор 4

ретий такт блок 8

(на выходе) блок 8 (на выходе) сумматор 4

ретий такт

(на входе 0001 блок 8

(на выходе) 1000 Xf 1 блок 8

сумматор 4 1110000000000

ретий такт

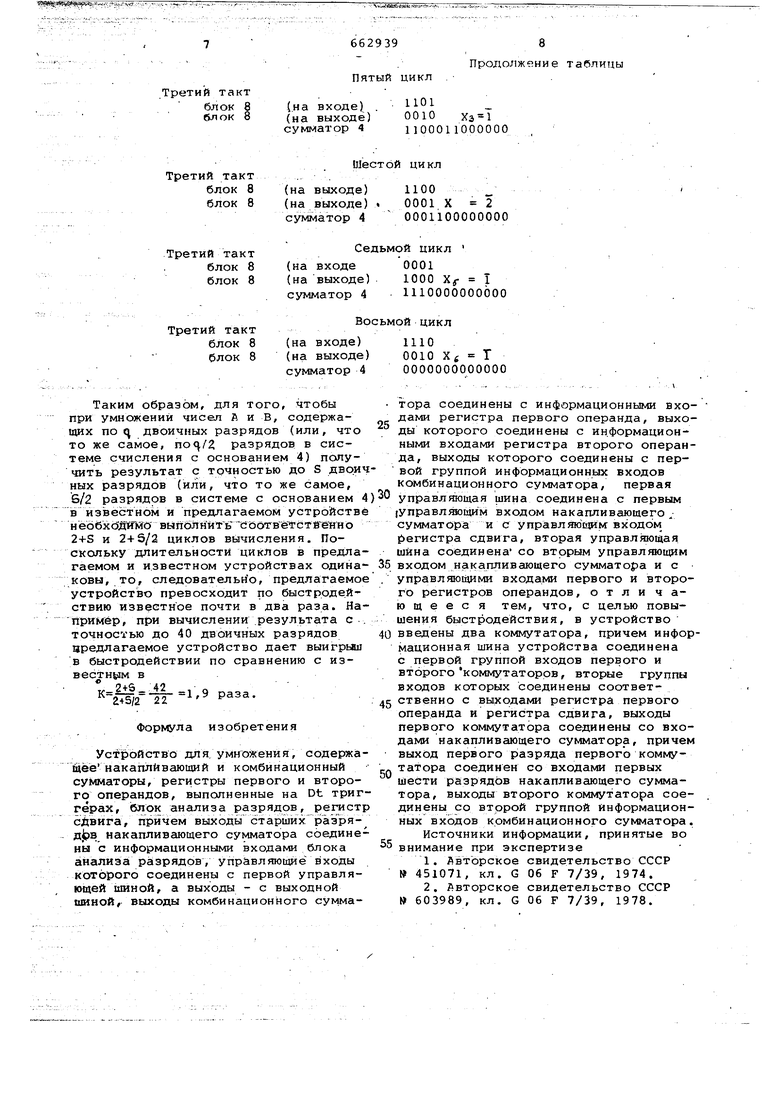

(на входе) блок 8 (на выходе) блок 8 сумматор 4 Таким образом, для того, чтобы при умножений чисел А и В, содержащих по ( двоичных разрядов (или, что то же самое, разрядов в системе счисления с основанием 4) получить результат с точностью до S двои ных разрядов (или, что то же самое, S/2 разрядов в системе с основанием 1в известном и предлагаемом устройств нёобхоДТРШО выпойнить ейотв-ё тств ённо 2+S и 2+3/2 циклов вычисления. Поскольку длительности циклов в предла гаемом и известном устройствах одина ковы, то, следовательно, предлагаемо устройство превосходит по быстроде.йствию известное почти в два раза. На Пример, при вычислении .результата с точностью до 40 двоичных разрядов предлагаемое устройство дает выигрьии в быстродействии по сравнению с известнум в K-2±§-ji2 -i 9 a4S/2 22 Формула изобретения Устройство для. умножения, содержа Йёё накапливающий и комбинационный сумматоры, регистры первого и второго операндов, выполненные на Dt триг герах, блок анализа разрядов, регист сДвига, причем выходы старших разряд|рв накапливающего сумматора соедине ны с информационными входами блока анализа разрядов, управляющие входы которого соединены с первой управляющей шиной, а выходы - с выходной шиной, выходы комбинационного сумма8

Продолжение таблицы Пятый цикл

1101

0010 хэ 1

1100011000000

Шестой цикл

1100

0001 X 2

0001100000000

Седьмой цикл

Восьмой цикл

1110

0010 Хй Т

0000000000000 тора соединены с информационными входами регистра первого операнда, выходы которого соединены с информационными входами регистра второго операнда, выходы которого соединены с первой группой информационных входов комбинационного сумматора, первая управлшощая шина соединена с первым (Управляющим входом накапливающего сумматора и с управляющим входом регистра сдвига, вторая управляющая шина соединена со вторым управляющим входом накапливающего сумматора и с управляющими входа.ми первого и второго регистров операндов, отличающееся тем, что, с целью повышения быстродействия, в устройство введены два коммутатора, причем информационная шина устройства соединена с первой группой входов первого и второгокоммутаторов, вторые группы входов которых соединены соответственно с выходами регистра первого операнда и регистра сдвига, выходы первого коммутатора соединены со входами накапливающего сумматора, причем выход первого разряда первого коммутатора соединен со входами первых шести разрядов накапливающего сумматора, выходы второго коммутатора соединены со второй группой Информационных входов комбинационного сумматора. Источники информации, принятые во внимание при экспертизе 1.Двторское свидетельство СССР 451071, кл. G 06 F 7/39, 1974. 2.Авторское свидетельство СССР 603989, кл. G 06 F 7/39, 1978.

Авторы

Даты

1979-05-15—Публикация

1977-01-07—Подача