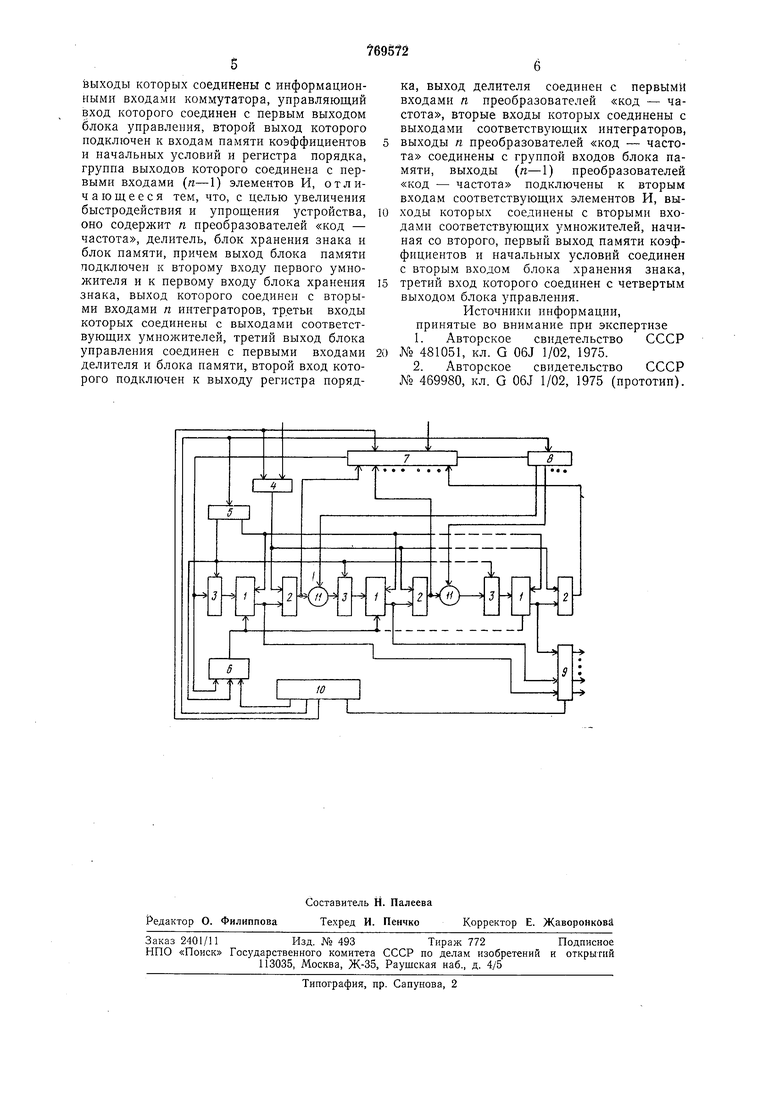

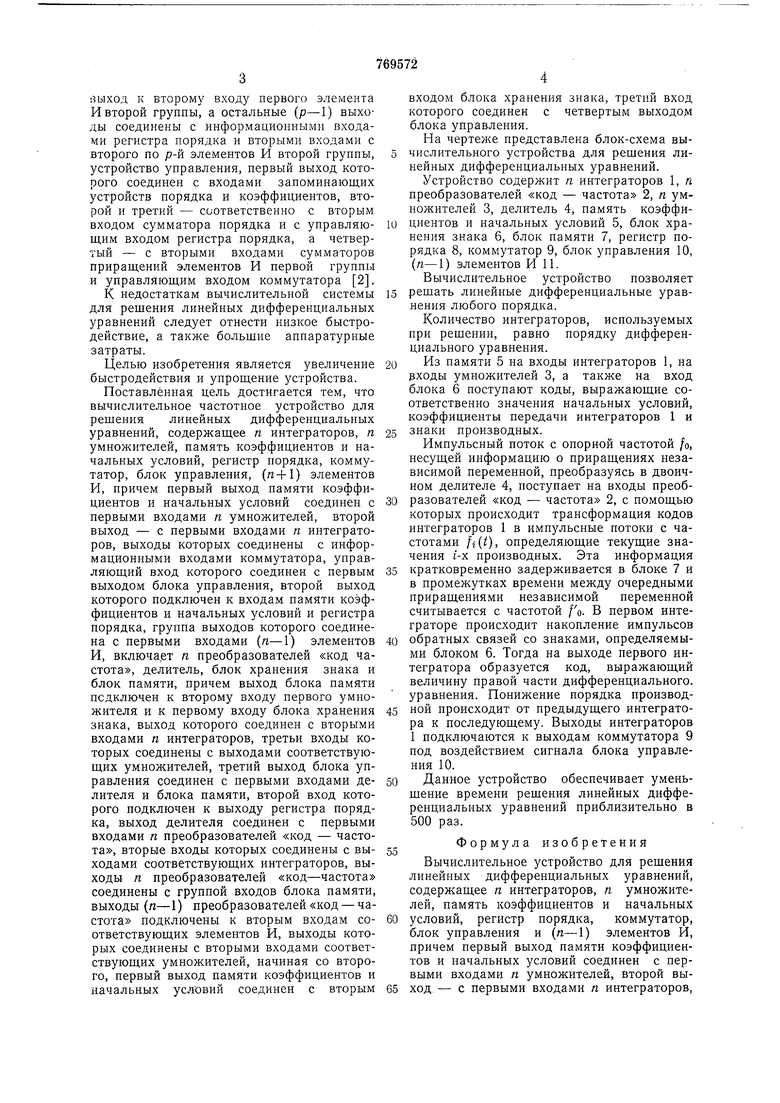

выход к второму входу первого элемента И второй группы, а остальные (р-1) выходы соединены с информационными входами регистра норядка и вторыми входами с второго по р-й элементов И второй группы, устройство управления, первый выход которого соединен с входами запоминающих устройств норядка и коэффициентов, второй и третий - соответственно с вторым входом сумматора порядка н с управляющим входом регистра порядка, а четвертый - с вторыми входами сумматоров приращений элементов И первой группы и управляющим входом коммутатора 2. К недостаткам вычислительной системы для рещения линейных дифференциальных уравнений следует отнести низкое быстродействие, а также больщие аппаратурные затраты. Целью изобретения является увеличение быстродействия и упрощение устройства. Поставленная цель достигается тем, что вычислительное частотное устройство для рещения линейных дифференциальных уравнений, содержащее п интеграторов, п умножителей, память коэффициентов и начальных условий, регистр порядка, коммутатор, блок управления, (л+1) элементов И, причем первый выход памяти коэффициентов и начальных условий соединен с первыми входами п умножителей, второй выход - с первыми входами я интеграторов, выходы которых соединены с информационными входами коммутатора, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к входам памяти коэффициентов и начальных условий и регистра порядка, группа выходов которого соединена с первыми входами (п-1) элементов И, включает п преобразователей «код частота, делитель, блок хранения знака и блок памяти, причем выход блока памяти подключен к второму входу первого умножителя и к первому входу блока хранения знака, выход которого соединен с вторыми входами п интеграторов, третьи входы которых соединены с выходами соответствующих умножителей, третий выход блока управления соединен с первыми входами делителя и блока памяти, второй вход которого подключен к выходу регистра порядка, выход делителя соединен с первыми входами п преобразователей «код - частота, вторые входы которых соединены с выходами соответствующих интеграторов, выходы и преобразователей «код-частота соединены с группой входов блока памяти, выходы (п-1) преобразователей «код - частота подключены к вторым входам соответствующих элементов И, выходы которых соединены с вторыми входами соответствующих умножителей, начиная со второго, первый выход памяти коэффициентов и начальных условий соединен с вторым входом блока хранения знака, третий вход которого соединен с четвертым выходом блока управления. На чертеже представлена блок-схема вычислительного устройства для рещения линейных дифференциальных уравнений. Устройство содержит п интеграторов 1, п преобразователей «код - частота 2, п умножителей 3, делитель 4, память коэффициентов и начальных условий 5, блок хранения знака 6, блок памяти 7, регистр порядка 8, коммутатор 9, блок управления 10, (п-1) элементов И 11. Вычислительное устройство позволяет рещать линейные дифференциальные уравнения любого порядка. Количество интеграторов, используемых при рещении, равно порядку дифференциального уравнения. Из памяти 5 на входы интеграторов 1, на эходы умножителей 3, а также на вход блока 6 поступают коды, выражающие соответственно значения начальных условий, коэффициенты передачи интеграторов 1 и знаки производных. Импульсный поток с опорной частотой /о, несущей информацию о приращениях независимой переменной, преобразуясь в двоичном делителе 4, поступает на входы преобразователей «код - частота 2, с помощью которых происходит трансформация кодов интеграторов 1 в импульсные потоки с частотами f-i(t), определяющие текущие значения i-x производных. Эта информация кратковременно задерживается в блоке 7 и в промежутках времени между очередными приращениями независимой переменной считывается с частотой /о. В первом интеграторе происходит накопление импульсов обратных связей со знаками, определяемыми блоком 6. Тогда на выходе первого интегратора образуется код, выражающий величину правой части дифференциального, уравнения. Понижение порядка производной происходит от предыдущего интегратора к последующему. Выходы интеграторов 1 подключаются к выходам коммутатора 9 под воздействием сигнала блока управления 10. Данное устройство обеспечивает уменьщение времени рещения линейных дифференциальных уравнений приблизительно в 500 раз. Формула изобретения Вычислительное устройство для рещения линейных дифференциальных уравнений, содержащее л интеграторов, п умножителей, память коэффициентов и начальных условий, регистр порядка, коммутатор, блок управления и (л--1) элементов И, причем первый выход памяти коэффициентов и начальных условий соединен с первыми входами л умножителей, второй выход - с первыми входами л интеграторов.

выходы которых соединены с информационными входами коммутатора, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к входам памяти коэффициентов и начальных условий и регистра порядка, группа выходов которого соединена с первыми входами (п-1) элементов И, отличающееся тем, что, с целью увеличения быстродействия и упрощения устройства, оно содержит п преобразователей «код - частота, делитель, блок хранения знака и блок памяти, причем выход блока памяти подключен к второму входу первого умножителя и к первому входу блока хранения знака, выход которого соединен с вторыми входами п интеграторов, третьи входы которых соединены с выходами соответствующих умножителей, третий выход блока управления соединен с первыми входами делителя и блока иамяти, второй вход которого подключен к выходу регистра порядка, выход делителя соединен с первыми входами п преобразователей «код - частота, вторые входы которых соединены с выходами соответствующих интеграторов, выходы п преобразователей «код - частота соединены с группой входов блока памяти, выходы (п-1) преобразователей «код - частота подключены к вторым входам соответствующих элементов И, выходы которых соединены с вторыми входами соответствующих умножителей, начиная со второго, первый выход памяти коэффициентов и начальных условий соединен с вторым входом блока хранения знака, третий вход которого соединен с четвертым выходом блока управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 481051, кл. G 06J 1/02, 1975.

2.Авторское свидетельство СССР № 469980, кл. G 06J 1/02, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор функций | 1984 |

|

SU1166148A2 |

| Устройство для моделирования лампы бегущей волны | 1977 |

|

SU748248A1 |

| УНИВЕРСАЛЬНОЕ ГИБРИДНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1971 |

|

SU311283A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU940213A1 |

| Цифровой функциональный генера-TOP | 1979 |

|

SU832550A1 |

| Устройство для решения разностных уравнений | 1978 |

|

SU767784A1 |

| Устройство для приема информации | 1981 |

|

SU1014001A1 |

| Генератор функций | 1982 |

|

SU1057966A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Преобразователь среднего значения напряжения | 1982 |

|

SU1114964A1 |

-

-

Авторы

Даты

1980-10-07—Публикация

1978-07-18—Подача