(54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ РАЗНОСТНЫХ УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор дискретных функций | 1978 |

|

SU746477A1 |

| Устройство для выполнения преобразования Фурье | 1985 |

|

SU1278887A1 |

| Устройство для контроля сигналов с импульсной модуляцией | 1984 |

|

SU1239871A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Цифровой согласованный фильтр для импульсных эхо-сигналов | 1981 |

|

SU964979A1 |

| Устройство для выполнения преобразования Фурье | 1986 |

|

SU1325509A1 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

| Цифровой фильтр | 1988 |

|

SU1566471A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Устройство для решения задач математической физики | 1989 |

|

SU1656552A1 |

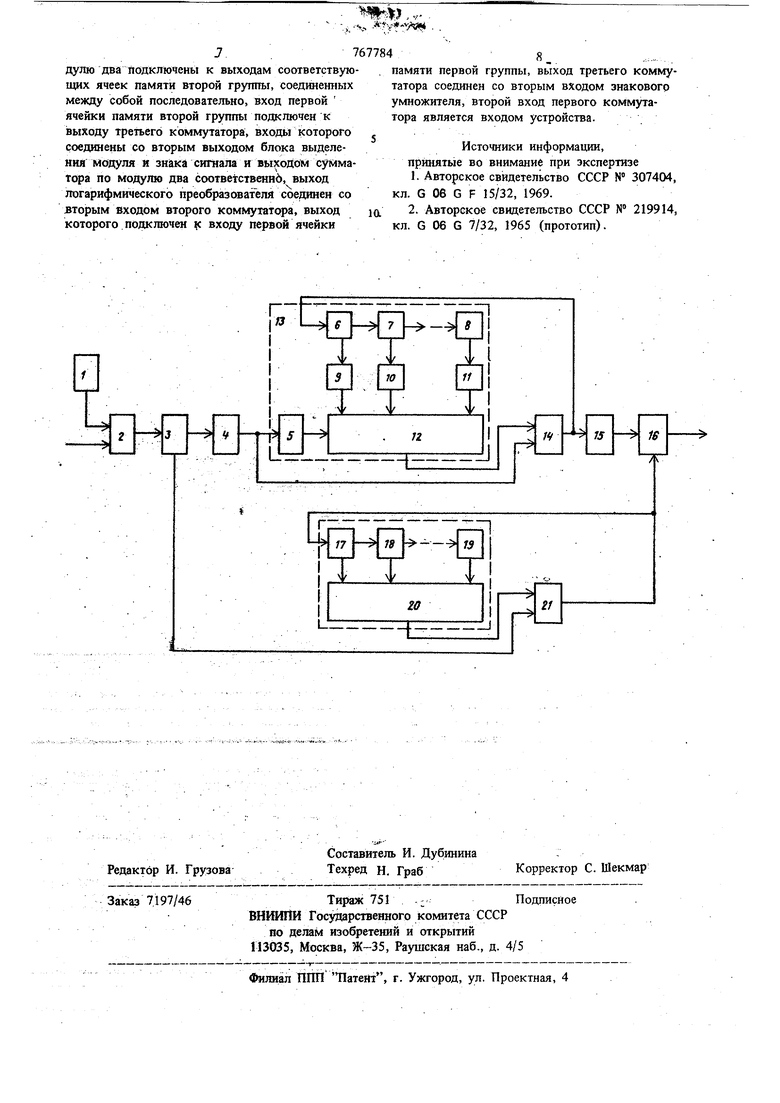

Изобретение относится к автоматике и вычислительной технике, а именно к области решения разностных уравнений, и может найти применение при проектировании спеииализированйых вычислительных устройств и фильтров. Известно устройство для моделирования дифференциальных уравнений, содержаП |её дафр вой блок, аналоговые зайомйнаювдие устройст ва, последовательно включенные два. суммирующих усилителя с цифровыми управляемыми сопротивлениями во входных цепях, интеграторы и ключи 1. Недостаток известного устройства заключается в невозможности решения разностных уравнений. Наиболее близким техническим решение к изобретению является устройство для ретяени разностных уравнений, содержащее первую груп пу последовательно соёдиненнь1х ячеек памяти, выходы которых через соответствующие блоки весовых коэффициентов подключены к группе входов сумматора 2. Однако известное устройство позволяет рещать сравнительно узкий класс уравнений, а Именно класс линейных разностных уравнений. Цель изобретения - расширение класса решаемь1Х уравнений. Указанная цель достигаетс;я тем, что в устройство для рещения разностных уравнений, содержащее первую группу последовательно соединенных ячеямк паглята, выходы которых через соответствумияяе 6noJGH весовых козффициентов подкйючёнь к группе входов сумматора, выведены знаКо вый умножитель, коммутаторы, блок йыделення модуля и знака сигнала, логарифмический прео6раз6ватега, блок весовых коэффициентов, пртенщфующйй преобразователь. Вторая группа ячеек памяти, сумматор по модулю два и блок задания начальных условий, выход котор0 го пощс1вочен к первому входу первого KoMMyTaTOpia, вькодоМ соединенного bo входом блока вьоделения модуля и знака сигнала, первый выход которого через логарифмический преобразователь подключен к входу блока BccoBbtx Коэффициентов, выход которого соединен со входом сумматора, выходом подключенного к первому входу второго коммутатора, выход которого через потенци3рующий преобразователь соединен с первым вдодом знакового умножителя, выход которог является выходом устройства. Входы суммато ра по модулю Два подключены к выходам соответствующих ячеек памяти второй группы соединеннщх между собой последовательно, вход первой ячейки памяти второй группы подключен к выходу третьего коммутатора, входы которого соединены со вторым выходо блока выделения модуля и знака сигнала и выходом сумматора по модулю два соответственно, выход логарифмического преобразова теля соединен со вторым входом второго коМ мутатора, выход которого подключен к входу первой ячейки памяти первой группы , вь1ход третьего коммутатора соединен со вторым входом знакового умножителя, второй вход первого коммутатора является входом устройства.. Структурная схема устройства представлена на чертеже. Устройство для решения разностных уравнений состоит из блока 1 задания начальных ,Перврго коммутатора 2, блока 3 выделения модуля и знака сигнала, логарифми. рующего преобразователя 4, блока 5 весовых Крзгффивдентов, последовательно соединенных ячеек, 6-8 памяти первой груты, группьг . блоков 9-11 весовых козффиодентов, сумматора 12 (ячейки 6-8 памяти, блоки 9-11 и сумматор 12 образуют блок 13 для рещения линейных над полем действительных чисел разностных уравнений), второго коммутатора 14, rtOTeHWipywuiero преббразователя 15, знаКовото умножителя 16, второй группы ячеек 17-19 П амяти; сумматора по модулю два 20, третьего коммутатора 21.. . Устройство предназначено для решения линейн ых над полем дёйствительньк чисел, линейных над полем OF (2) и нелинейных раз йостных урав яёний вида Ul nbiii-ji Hxtiif, РабЬЙ устройства состоит из даз хэтайов. Сначала производится запись йачальных условий, а затем - ре1шение уравнения. Алгорйтмь работы устройства получаем т уравнения (1) при помощи следующих преобразований. Исключая нулевые начал ьные в урувяекш (1), так как при них получаем три виальное решение при « -1, 2, 3, ... запишем уравнение (1) в сйедующем виде Qbs b ti-jlf аЪз Uc-i Jli 1 j; (2) КCJi I nsigTh (vLi-jl) sigViCxt43 tH гдеаЪв(мС-1:-))Ьа5солютиые значения величин ;j;v -1-3 ) v sigfhbti-jD.signWilf, -знаки тех же величин. В уравнении (2) первый сомноиситель (в фигурных скобках) определяет абсолютную величину )Ii , а второй - ее знак, т.е. уравнение (2) распадается на два независимых уравнения(3) qb5 til-- loib5(ti-j f -q1ae . , Sigfn til--nsi v ti-3lf 6ign.UI.)V которые можно решать независимо. Логарифмируя уравнение (3), получаем линейное разностное уравнение относительно логарифмов; N : .. Еп qbsi ti 1 II ailM alDs N t-i-il- iri . -bev c3ibs4ktil которое решается с помощью. блока 5. Откуда.. аЬ5) f 3 i c bSSti l| Приняв ULil1 0 О p-usig-wUtil l-I np-u, XT(,tn)0 0 ftfj-u-CvLi-jafbo ,йЫ-Л1 1 о произведения в уравнении (4) можно заменить суммой по модулю два, т.е. урйвнение (4) принимает вид siofh 01 -- S sip-и (vti-jl) . A-sig-h xi:i-jiA vvod) Уравнение (7) является линейным над поЛем 0F (2) разностным уравнением, решение которого находится с помощью ячеек 17-19 и сумматора по модулю два 20. Рассмотрим работу устройства при записи начальных условий. При этом коммутаторы 2/ 14, 21 протаскают сигналы с, входов блока 1 на выходы, В первом такте пройзводатся запись началыюго условия ЗГ-14 1, которое из блока 1 задания начальных условий через коммутатор 2 поступает в блок 3, на первом выХоде которого получаем ObSS Г-КЗ,а на втором SigfliNt-NjI Сигнал аЪ t-NlnocTynaeT в логарифмирующий преобразователь 4, с выхода которого 57 сигнал СиаЪб C-Nl через коммутатор 14 записывается в ячейку 6 памяти и поступает в потенцирующий преобразователь 15. Сигнал СИЪа jt-N3 с выхода потенцирующего преобра зователя 15 поступает на первый вход знакового умножителя 16 С второго выхода блока 3 сигнал )tN через коммутатор 21 загШсывается в ячейку . 17 памяти и поступает на второй вход знакового умножителя 16. В знаковом умножите- : ле 16 происходит перемножение сигналов ab53C N1 и SiQfM trNl в результате чего на выходе устройства ползд1аем сигнал dC-NI-absst-NlsiQfh L-Nl. в каждом последующем такте работы устройства происходит синхронный сдвиг вправо информащш в ячейках 6, 7, 8 памяти блока 13 и в ячейках 17-19, а в освобождающиеся, ячейки 6 и 17 производится запись других начальных условий ей чЪб S t- tH - Щ ,гу аЪе V) t- ,..., tvi аЪБ -у t-13 W s-ig-n -(N-1), si v I4N-a,.:-,),W. соответственно. . Таким образом, по истечении Н тактов работы, в ячейках 6-8 оказываются записань ,. eУ OlbSS n,lVlaЪSЧП-23,..., a в ячейках 17-19-51 иМ L-ll.sig-vi v) С-С1 3. .SAg-vi-jt-Na. .. После записи начальных условий происходит переключение коммутаторов 2, 14, 21, которые начинают пропускать сигналы с входов на вб1ходы. С Й-И-го такта начинается решение уравнения (1). Рассмотрим работу устройства в Н+1-м такте/ , -. .,, Первое значение входного сигнала lf. 1чере коммутатор 2 преходит в блок 3, где проис ходит вьщеление модуля его с ЪвхС1и знака Sig Xtl-l-Сигнал аЪвкIll лога ифмируется в преобразователе 4; умножается на коэффициент Ъ в блоке 5 и поступает в суМШтор 12. Туда же поступают сщналы СнсяЪв 1 Iv ,...,Е..У с Ъ5 1:--М,умножйшь1е В блоках 9-11 на коэффициенты О,012,.. соответственно. На выходе сумматора в соответствии с уравнением (5) получаем сигнал еу1аЪбз111 -а гмсзЪвзМ a,jt аъе t-a 3 с| еух оЪ«,1 t-H З- ЪВу аЪ5хИ1, который через коммутатор 14 поступает в погенцирующий преобразователь 15 и « следую-, щем такте записывается в освободившуюся в результате сдвига ячейку 6 памяти. Сигнал abs t-ll-iexp С, блока 15 поступает в знаковый умножитель 16. С блока 3 сигнал Si MXltl поступает в сумматор по модулю два 20. Туда же поступают сигналы tn,SAgfh i;-ll,.-,c,ig,} t-Nl. В сумматоре 20 реализуется уравнение (7), в результате чего получаем которое через коммутатор 21 проходит в знаковый умножитель J6 и в следующем такте запись вается в освободивщуюся в результате сдвига ячейку 17 памяти. В знаковом умножителе 16 реализуется операция З С 1--аЬ5 t-tl 113, причем .jj ЩiJ, 61gT JtU-C |- 31Ъва113 Hfstc S-jgrvi JC13 Полученный на выходе блока 16 сигнал Clj является первь1М значением решения уравнения (1). В последующие такты работа устройства аналогичная. Устройство обладает более широкими возможностями по Сравнению с прототипом и аналогами и позволяет получать решения следующих классов разностных уравнений линейных над п0лем действительных чисел, швейных над полем F (2) на выходе, нелинейных м/пьтипликативнь х уравнений. Формула изобретения Устройство для решения разностных уравне НИИ, содержащее первую группу последовательно соединенных ячеек памяти, выходы которых через соохветстгаующие блоки весовых коэффициенто в цодключ ы к группе входов сумматора, о t л я ч а ю 1ц е е с я тем, что, с 1|елью ра:аиир€«мя класса решаемьтх уравнений, в устройство введены знаковый улоюжитель, коммутаторы, блок выделения модуля и знака сигнала, логарифмический преобразователь, блок весовых коэффициентов, потенцируюцщй преобразователь, вторая группа ячеек памяти, сумматор по модулю два и блок задащга начальных условий, выход которого подключен к первому входу первого коммутатора, выход которого соеданен со входом блока выделения и знака сигнала, первый выход которого через Логарифмический преобразователь подключеи к входу блока весовых козффициштов, выход которого соединен со входом сумматора, выход которого подключен к первому входу второго коммутатора, выход которого через потендарующий преобразовател средшен с первым входом знакового умножителя выхОд которого является выходом устройства, вхо; сумматора по модулю два подключены к выходам соответствующих ячеек памяти второй группы, соединенных между собой последовательно, вход первой ячейки памяти второй группы подключен к выходу третьего коммутатора, входы которого соединены со вторым выходом блока выделения модуля и знака сигнала и ВЫХОД01И сумматора по модулю два соответствениб, выход логарифмического преобразователя соединен со вторым входом второго коммутатора, выход которого подключен с входу первой ячейки 7 8 памяти первой группы, выход третьего коммутатора соединен со вторым входом знакового умножителя, второй вход первого коммутатора является входом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 307404, кл. G Об G F 15/32, 1969. 2.Авторское свидетельство СССР № 219914, кл. G 06 G 7/32, 1965 (прототип).

Авторы

Даты

1980-09-30—Публикация

1978-10-16—Подача