и элементы И, первые входы которых соединены с первыми входами адресного блока. Вторые входы элементов И подключены ко вторым выходам адресного блока, выходы - к одним из входов первых счетчиков, другие входы которых подсоединены к третьим входам адресного блока. Третьи входы первых счетчиков соединены с иервымн входами вторых счетчиков и со вторыми входами адресного блока. Выходы первых счетчиков соедииены со входами дешифраторов, выходы которых соединены со вторыми входами вторых счетчиков, третьи и четвертые входы которых соединены соответственно со вторыми входами элементов И и со вторыми входами первых счетчиков. Выходы вторых счетчиков соединены с первыми выходами адресного блока.

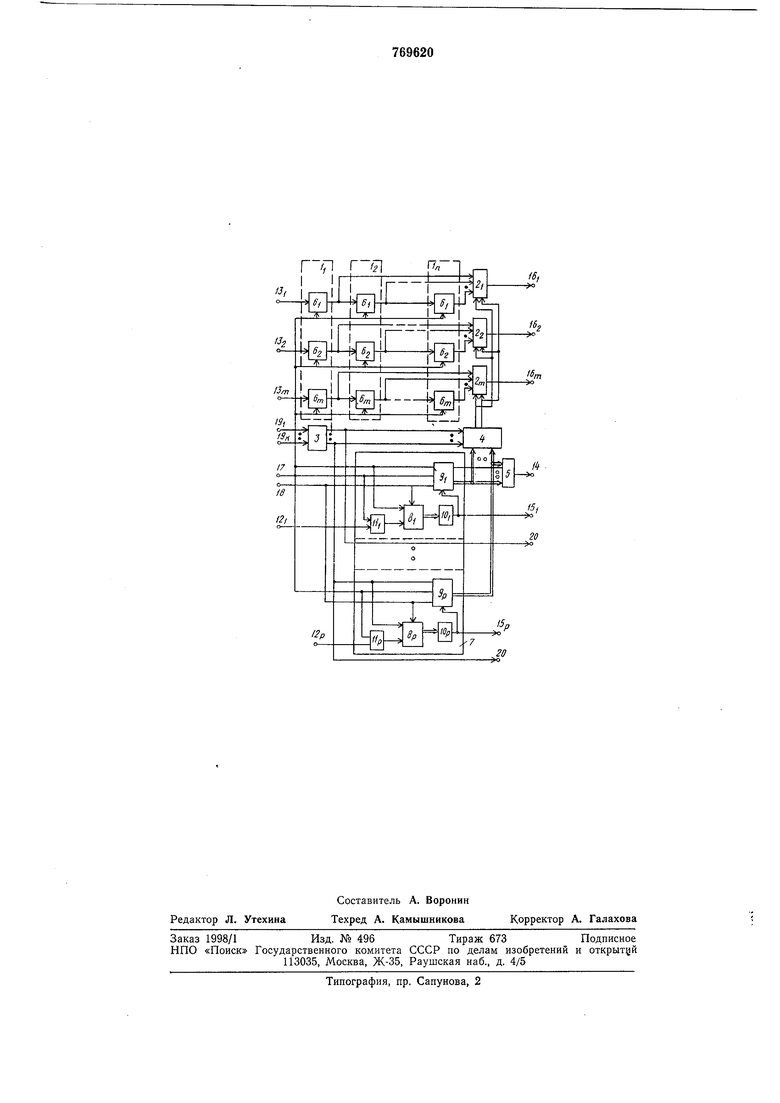

На чертел е представлена функциоиальная схема предложенного ЗУ.

Оно содержнт регистры , разрядные коммутаторы 2i-2™, блок управления 3, коммутатор выборки 4, дешифратор занятости 5, ячейки памяти 6i-6„г, адресный блок 7, содержаш,ий иервые счетчики 8i-8р, вторые счетчики 9i-9р, дешифраторы lOi-Юр, элементы И lli-lip, шииы выборки 12i-12р, информационные входы устройства , нервый выход 14 н вторые выходы устройства 15i-15р, третьи выходы устройства 16i-16m, шину управления записью 17, шину синхронизируюших импульсов 18, шнны запроса считывания 19i-19/i и шины разрешения считывания 20.

Устройство предполагает поблочную передачу данных от одного источника к одному или нескольким приемникам. Каждый блок данных адресуется соответству1ош,ему приемнику. Адресация блока данных осуш,ествляется источником путем выдачи уровня логической «1 на шине 12 на соответствуюш,ем входе адресного блока 7 на времй заниси блока данных. Длина блока данных может быть произвольной в пределах объема намяти устройства. Ввод блока данных должен начинаться при возбужденном индикаторе соответствуюшего приемника. Прекраш,енне записн ннициируется источником данных с учетом состояния индикатора занятости.

Чтение данных осуществляется по инициативе приемника с учетом состояния соответствуюш,его индикатора путем подачи сигиала запроса чтения на соответствующую шину 19. Сигиал на шине 19 должен сохраняться до появления снгнала разрешения чтения на соответствующей шине 20. После этого сигнал на шине 19 должен быть снят в течение одного такта на шине 18.

Устройство работает следующим образом.

В исходном состоянии счетчики, например, 8i и 9i, а следовательно, выход 14 установлены в «нулевое состояние, а выходы 15 - в «единичное.

При записи слова данных на входах ISj-13m устанавливается соответствующий код, устанавливается «1 на одной из шин 12 выбора нулсного нриемника, затем подается сигнал записи на шину 17. При этом код с шин 13i-13m заноснтся в младший регистр li устройства, к содержимому счетчика 9i блока 7 выбранного приемника через открытый элемент И lli нрибавляется «1. Счетчик 9i остается в «нулевом состояиии, так как в момент ностунления сигнала на счетный вход счетчика на его вход

установки с выхода дешифратора IQi поступает уровень «О. После перехода счетчика 8i в нулевое состояиие уровень «О на выходе дешифратора lOj исчезает и устанавливается в состояние «О нндикатор по

шине 15i. При иоступлении иа шины 13i-18m следующего слова данных по сигналу записи с шины 17 осуществляется сдвиг записанной ранее информации на один шаг в сторону старших разрядов намяти, а в младший регистр li заносится новое слово данных, и содержимое счетчиков 8 и 9 соответствующего блока 7 увеличивается на «1. Таким образом, процесс продоллсается до момента снятия сигнала на

шинах 12i-12р. После этого источник выставляет уровень «1 на шине 12 следующего приемника и вьшолпяет запись нового блока данных. Счетчики 9i-9р блока 7 продолжают накапливать «1 по любым

сигналам записи, сохраняя, таким образом, адрес начала «своего блока данных, который смещается в сторону старших регистров li-IP устройства. По мере поступления новых слов данных однн из счетчиков

адресного блока 7 выбранного приемника наканливает «1 синхронно соответствующему счетчику 9, а состояние счетчиков 82-8р других приемников не изменяется. При чтении данных приемиик подает сигнал на одну из шин 19i-19;; заироса чтения. Этот сигнал через блок унравления 3 запросами поступает на соответствующий вход коммутатора выборки, иодключая к управляющим входам одного из коммутаторов 2i-2m выходы одного из счетчиков 9i-9р адресного блока 7. Таким образом, коммутируется на шины 16i-16m очередное слово блока данных, адресованное занрашивающему приемнику. Слово данных с

шин 14 считывается приемником, и содержимое соответствующих счетчиков 9 н 8 адресного блока 7 уменьшается на «1 и сигнал с одной из шин 19 сни.мается. Следующее слово да иных читается аналогично.

Чтение данных разными нриемииками осуществляться в нроизвольной последовательности. Чтение нродолжается до перехода соответствующего счетчика 8 в

нулевое состояние, после чего обнуляется

соответствующий счетчик 9, и возбуждается соответствующий иНлТ,икатор по одному из выходов 15i-15р исчерпания блока данных, запрещающий приемнику запращивать данные и сигнализирующий источнику о необходимости записи нового блока данных по адресу данного приемника.

При одновременном поступлении сигнала записи на щину 17 и сигнала чтения на одну из шин 19 данные «читаемого регистра коммутируются на щины 16i-16т- Счетные входы соответствующих счетчиков 9i-9р блока 7 приемника, «выбранного по щине чтения или счетчиков 9i-9р и 8i-8р, и блока 7 приемника, «выбранного по щинам чтения и записи, взаимио блокируются.

Положительный эффект от использования ЗУ заключается в следующем.

Применение ЗУ позволяет организовать передачу данных от одного источника к одному или нескольким приемникам с минимальными аппаратурными затратами как со стороны источника данных, так и со стороны каждого из приемников. Число подключаемых приемников принципиально неограничено.

ЗУ позволяет организовать эффективную передачу данных в системах с разноскоростными приемниками, например с приемниками с «плавающим циклом чтения (графическими терминалами) за счет динамического распределения памяти.

ЗУ может быть успещно применено в качестве быстродействующего межпроцессорного буфера в мультипроцессорных системах с последовательной обработкой данных.

ЗУ позволяет исключить влияние источника на быстродействие каждого из приемников и наоборот за счет возможности совмещения циклов записи и чтения.

Предложенное ЗУ в качестве межпроцессорного буфера в системе с одним источником и одним приемником применено в «Широкоформатном графическом экранном пульте проектировщика, А54310, предназначенном к серийному производству с 1980 г

ЗУ на 5 40-разрядных слов выполнено на интегральных микросхемах (ИМС) средней степени интеграции серии К155 и проверено на экспериментальном образце А54310.

Внедрение предложенного ЗУ дает экономию за счет сокращения по сравнению с прототипом аппаратуры на реализацию запоминающих элементов. На каждых 8 бит памяти экономится 3 шт. ИМС, т. е. 75 шт. ИМС на каждое ЗУ, что с учетом стоимости изготовлеиия печатных плат, стоимости ИМС, других материалов и сборки блоков элементов составляет около 300 рублей.

При планируемом объеме выпуска 100 ЗУ в год годовой экономический эффект составит 30 тыс. рублей.

Вследствие регулярности структуры ЗУ

может быть выполнено на базе ИМС с большой степенью интеграции.

Формула изобретения

1. Буферное запоминающее устройство, содержащее последовательно соединенные регистры, первые входы первого регистра подключены к информационным входам устройства, блок управления, адресный

блок, щины запроса считывания, шину управления записью, шины выборки и щину синхронизирующих импульсов, отличающееся тем, что, с целью расщирения области применения устройства и его упрощения, в него введены разрядные коммутаторы, коммутатор выборки и дешифратор занятости, входы которого соединены с первыми выходами адресного блока и первыми входами коммутатора выборки, выход дешифратора занятости подключен к первому выходу устройства, вторые выходы коммутатора выборки соединены с выходами блока управления, входы которого соединены с шинами запроса считывания, первые входы адресного блока подключены к щинам выборки, вторые входы - к шине синхронизирующих импульсов, третьи входы - к выходам блока управления, вторые выходы адресного блока соединены со вторыми

входами регистров и щиной управления записью, третьи выходы - со вторыми выходами устройства, выходы регистров соединены с одннм из входов разрядных коммутаторов, другие входы которых соедииены с выходами коммутатора выборки, выходы разрядных коммутаторов соединены с третьими выходами устройства.

2. Устройство по и. 1, отличающееся тем, что адресный блок содержит счетчики,

дещифраторы и элементы И, первые входы которых соединены с первыми входами адресного блока, вторые входы элементов И подключены ко вторым выхода.м адресного блока, выходы элементов И соединены с

одними из входов первых счетчиков, другие входы которых подсоединены к третьим входам адресного блока, третьи входы первых счетчиков соединены с первыми входами вторых счетчиков и со вторыми входами

адресного блока, выходыиервых счетчиков соединены со входами дещифраторов, выходы которых соединены со вторыми входами вторых счетчиков, третьи и четвертые входы которых соединены соответственно со

вторыми входами элементов И и со вторыми входами первых счетчиков, выходы вторых счетчиков соединены с первыми выходами адресного блока.

Источники информации,

принятые во внимание при экспертизе

1.Экспресс-информация серии «Вычислительная техника, № 26, 1978.

2.Авторское свидетельство СССР № 519761, кл. G ПС 19/00, 07.05.74 (прототип).

Г /Л Г /Л

I I Г11,

3

/J/л

О

tr5d-Ь

/9,

/7

/S t2i

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Ассоциативное оперативное запоминающее устройство | 1986 |

|

SU1324071A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1615803A1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-02—Подача