1

Изобретение относится к области вычислительной техники и может быть исиользовано при обработке информации от абонентов в порядке ее поступления.

Известно запоминающее устройство, со- 5 держащее последовательно соединенные группы запоминающих ячеек и управляющие ячейки, соответствующие каждой группе и состоящие из бистабильного элемента памяти, элемента совпадения и элемента ю задержки. В таком устройстве сдвиг по окончанию обработки информации, находящейся в последней группе запоминающих ячеек, проводится последовательным переписыванием информации из предществую- is щих ячеек в освободившиеся последующие ячейки, а это снижает быстродействие всего устройства 1.

Известно другое буферное запоминающее устройство, предназначенное для накопле- 20 ния поступающей в него информации и выдачи ее в порядке поступления и содержащее многоступенчатый накопитель и блок опроса, в состав которого входят сдвигающая цепочка элементов и логические вен- 25 тили. Необходимость применения в этом устройстве логических вентилей для параллельного вывода информации из каждой ступени накопителя, а также дополнительные регистры для хранения информации, 30

находящейся на обслуживании, приводят к увеличению количества элементов в устройстве, что снижает его надежность 2.

Наиболее близким техническим рещением к данному является буферное запоминающее устройство, содерл ащее запоминающие регистры, первые входы установки которых, кроме первого, соединены с выходами первых элементов И, первые входы одних-элементов И соединены с прямыми выходами других запоминающих регистров, вторые входы первых элементов И соединены с инверсными выходами соответствующих триггеров состояния, первые входы сброса которых соединены со вторыми входами первых элементов ИЛИ и с щиной сброса, первые входы первых элементов ИЛИ соединены с тактовой щиной, выходы которых соединены со входами сброса соответствующих запоминающих регнстров, третьи входы соответствующих первых элементов ИЛИ соединены с прямыми выходами соответствующих триггеров состояния, входы установки основных разрядов первого запоминающего регистра соединены со входами второго элемента ИЛИ и с выходами других первых элементов И 3.

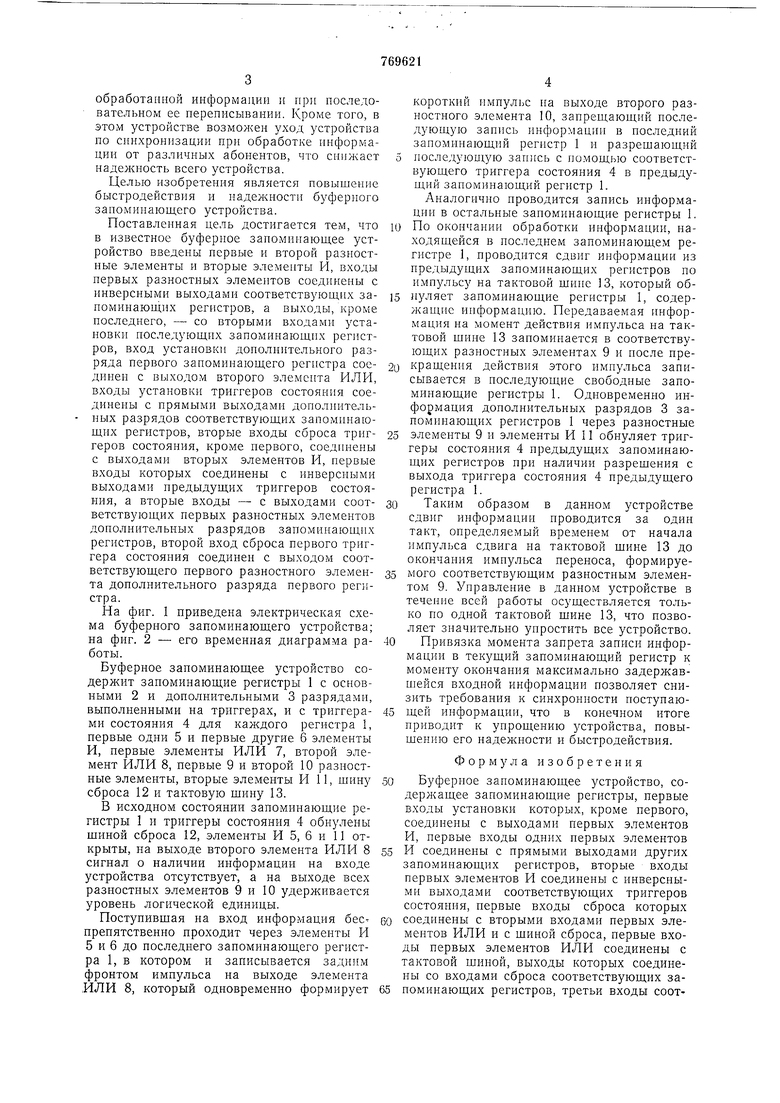

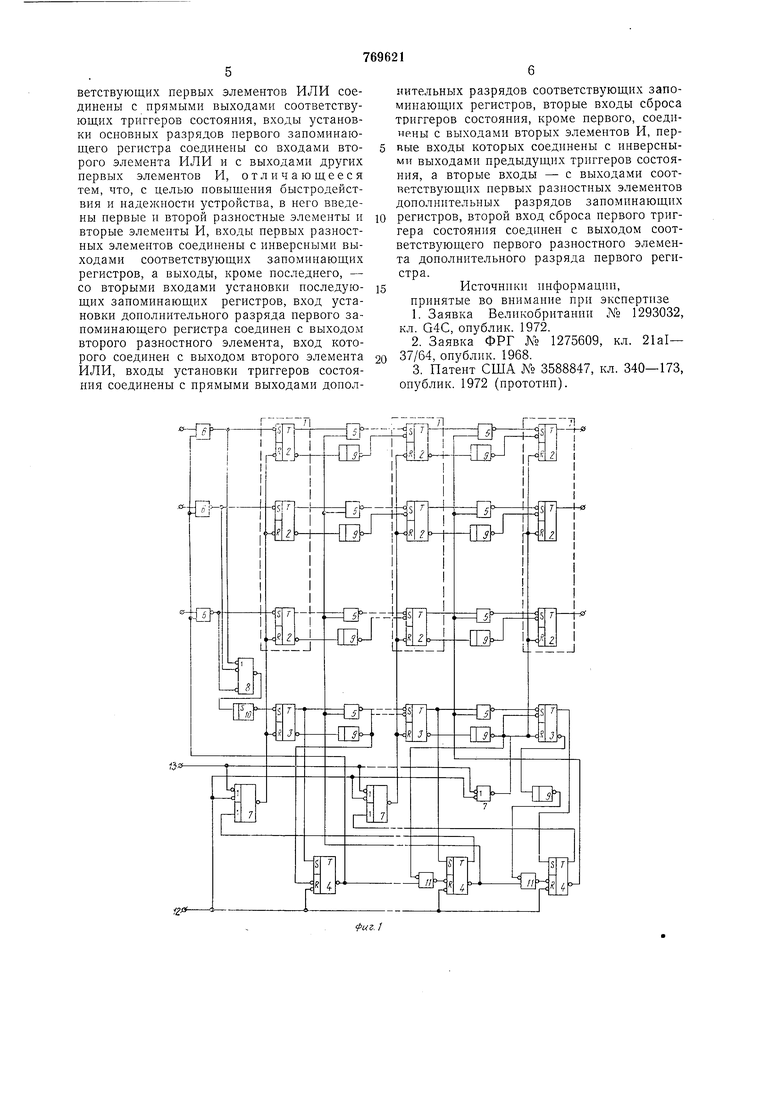

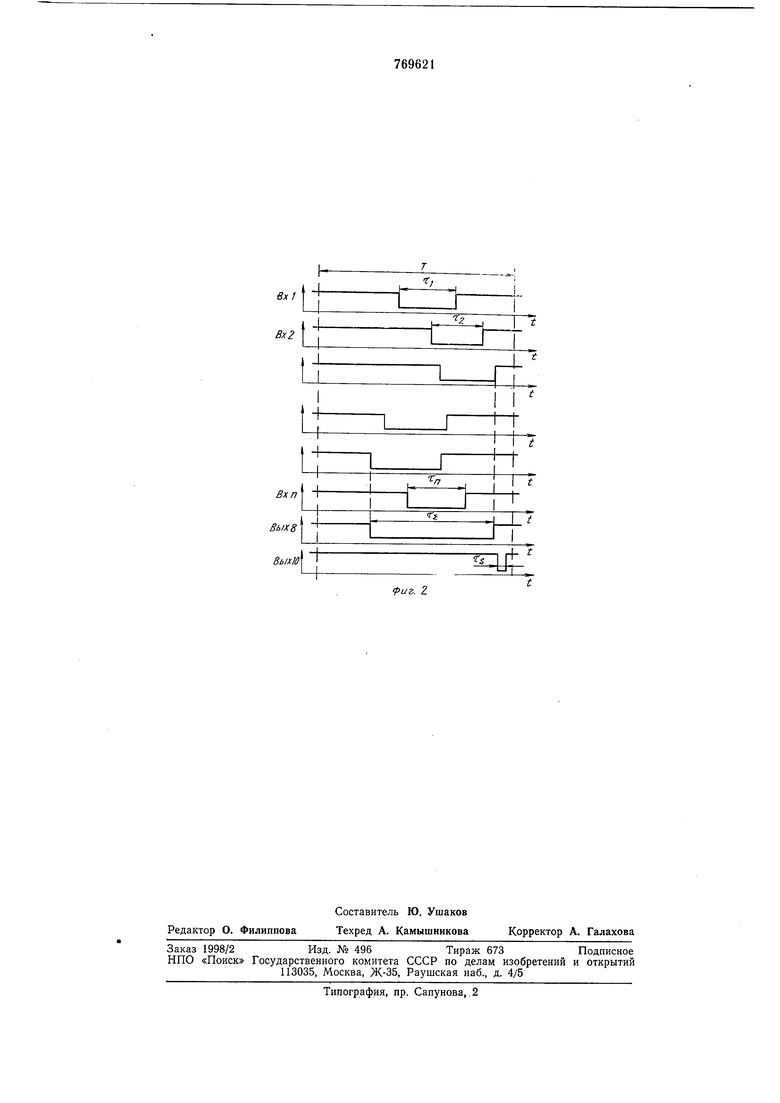

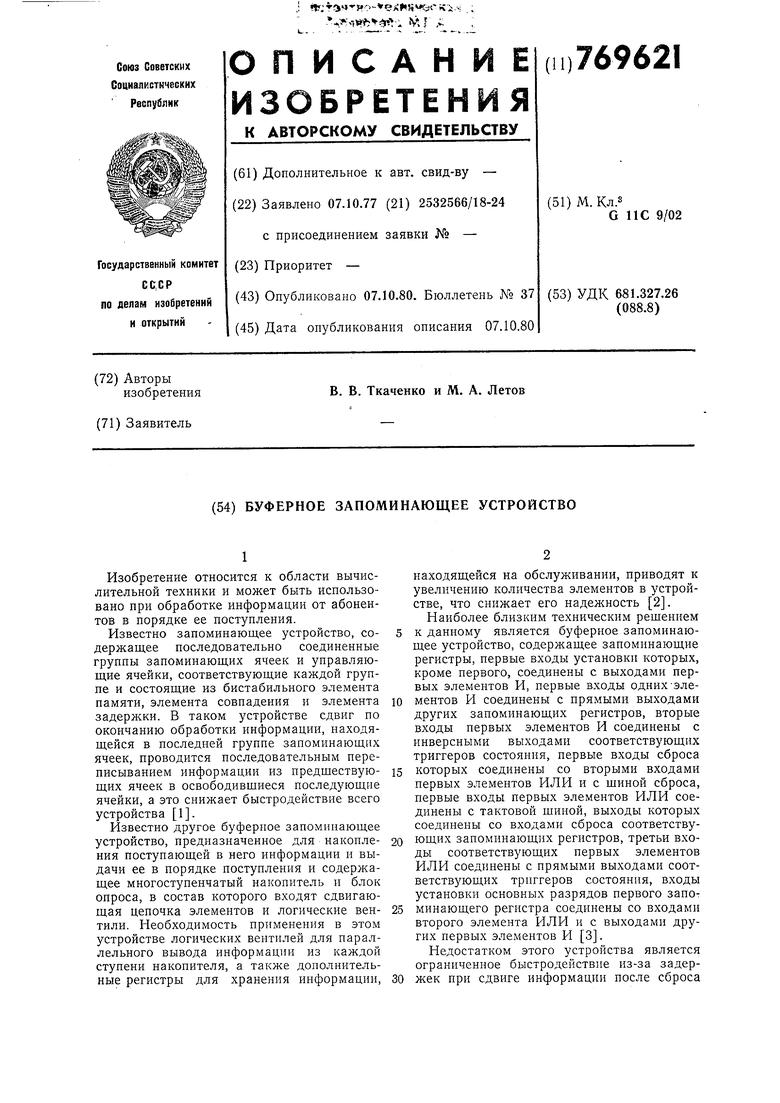

Недостатком этого устройства является ограниченное быстродействие из-за задержек при сдвиге информации после сброса обработанной информации и ири иоследователы-юм ее иереписываиии. Кроме того, в этом устройстве возможен уход устройства по синхронизации при обработке ииформации от различных абонентов, что снижает надежность всего устройства. Целью нзобретення является повышение быстродействия н надежности буферного запоминающего устройства. Поставленная цель достигается тем, что в известное буферное запомииающее устройство введеиы первые и второй разностные элементы и вторые элементы И, входы первых разностных элементов соединены с инверсными выходами соответствующих запоминающих регистров, а выходы, кроме последнего, - со вторыми входами устаиовки последующих запоминающих регистров, вход установки доиолнительного разряда первого запомииающего регистра соединен с выходом второго элемента ИЛП, входы установки триггеров состояния соединены с прямыми выходами дополиительиых разрядов соответствующих запомииающих регистров, вторые входы сброса триггеров состояния, кроме первого, соедпнены с выходами вторых элементов И, первые входы которых соединены с инверсными выходами предыдущих триггеров состояния, а вторые входы - с выходами еоответствующих первых разиостных элементов доиолнительных разрядов запоминающих регистров, второй вход сброса первого триггера состояния соединен с выходом соответствующего первого разностного элемента дополнительного разряда первого регистра. На фиг. 1 приведена электрическая схема буферного запоминающего устройства; на фиг. 2 - его временная диаграмма работы. Буфериое запоминающее устройство содержит запоминающие регистры 1 с основными 2 и дополнительными 3 разрядами. выполненными иа триггерах, и с триггерами состояния 4 для каждого регистра 1, первые одни 5 и первые другие 6 элемеиты И, первые элементы ИЛИ 7, второй элемент ИЛИ 8, первые 9 и второй 10 разностные элемеиты, вторые элементы И 11, шину сброса 12 и тактовую щину 13. В исходном состоянии запоминающие регистры 1 и триггеры состояния 4 обнулены шиной сброса 12, элемеиты И 5, 6 и 11 открыты, на выходе второго элемента ИЛИ 8 сигнал о наличии информации на входе устройства отсутствует, а на выходе всех разностных элементов 9 и 10 удерживается уровень логической единицы. Поступившая иа вход ииформация бес препятствеино проходит через элементы И 5 и 6 до последнего запомииающего регистра 1, в котором и записывается задним фронтом импульса на выходе элемента :ИЛИ 8, который одновременно формирует короткий импульс иа выходе второго разностного элемента 10, запрещающий последующую запись информацнн в последний запоминающий регистр 1 и разрещающнй последующую запись с помощью соответствующего триггера состояния 4 в предыдущий запоминающий регистр 1. Аналогично проводится запись ипформацни в остальные запоминающие регистры I. По окончании обработки информации, находящейся в последнем запоминающем регистре 1, проводится сдвиг информации из предыдущих запоминающих регистров по импульсу на тактовой щиие 13, который обпуляет запоминающие регистры 1, содержащие информацию. Передаваемая информация на момент действия импульса на тактовой Н1ине 13 запомииаетея в соответствующих разностных элементах 9 и носле прекращения действия этого имиульса записывается в последующие свободные запоминающие регистры 1. Одиовременно информация дополнительных разрядов 3 запомппающих регистров 1 через разностные элементы 9 и элементы И 11 обнуляет триггеры состояния 4 предыдущих запоминающих регистров при наличии разрешения с выхода триггера состояпия 4 предыдущего регистра 1. Таким образом в данном устройстве сдвиг информации проводится за один такт, определяемый времеием от начала импульса сдвига на тактовой шине 13 до окончапия имиульса переноса, формируемого соответствующим разиостиым элементом 9. Управление в данном устройстве в течение всей работы осуществляется только по одной тактовой шине 13, что позволяет зпачителы-ю упростить все устройство. Привязка момента запрета записи информации в текущий запоминающий регистр к моменту окончания максимально задержав иейся входиой информации позволяет снизить требования к синхронности поступающей ииформацин, что в конечном итоге приводит к упрощению устройства, повышению его иаделсности и быстродействия. Формула изобретения Буферное запоминающее устройство, содержащее запоминающие регистры, первые входы установки которых, кроме первого, соединены с выходами первых элементов И, первые входы одних иервых элементов И соединены с прямыми выходами других запоминающих регистров, вторые входы первых элементов И соединены с инверсными выходами соответствующих триггеров состояния, первые входы сброса которых соединены с вторыми входами иервых элементов ИЛИ и с щииой сброса, первые входы первых элементов ИЛИ соединены с актовой щиной, выходы которых соединены со входами сброса соответствующих запоминающих регистров, третьи входы соответствующих первых элементов ИЛИ соединены с прямыми выходами соответствующих триггеров состояния, входы установки основных разрядов первого запоминающего регистра соединены со входами второго элемента ИЛИ и с выходами других первых элементов И, отличающееся тем, что, с целью повышеиия быстродействия и надежности устройства, в него введены первые и второй разностные элементы и вторые элементы И, входы первых разностных элементов соединены с инверсными выходами соответствующих запоминающих регистров, а выходы, кроме последнего, - со вторыми входами установки иоследующих запоминающих регистров, вход установки донолнительного разряда первого запоминающего регистра соединен с выходом второго разностного элемента, вход которого соединен с выходом второго элемента ИЛИ, входы установки триггеров состояния соединены с прямыми выходами дополнительных разрядов соответствующих запоминающих регистров, вторые входы сброса триггеров состояния, кроме первого, соединены с выходами вторых элементов И, иервые входы которых соединены с инверсными выходами предыдущих триггеров состояния, а вторые входы - с выходами соответствующих первых разностных элементов дополнительных разрядов запоминающих

регистров, второй вход сброса первого триггера состояния соедииеп с выходом соответствующего первого разностного элемента дополнительного разряда первого регистра.

Источники информацтп,

принятые во внимание при экспертизе

1.Заявка Великобритаиии № 1293032, кл. G4C, оиублик. 1972.

2.Заявка ФРГ №. 1275609, кл. 21а1- 37/64, опублик. 1968.

3.Патент США № 3588847, кл. 340-173, опублпк. 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты | 1979 |

|

SU828418A1 |

| Регистр сдвига | 1976 |

|

SU682950A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Буферное запоминающее устройство с самоконтролем | 1976 |

|

SU595796A1 |

| Буферное запоминающее устройство | 1977 |

|

SU733018A1 |

| Устройство для сопряжения | 1983 |

|

SU1124276A1 |

| БИБЛИОТЕКА 1 | 1971 |

|

SU319907A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU407396A1 |

| Многоканальное устройство синхронизации | 1988 |

|

SU1642473A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU269215A1 |

Авторы

Даты

1980-10-07—Публикация

1977-10-07—Подача