1

Изобретение относится к вычислитель.ной технике, может быть использовано при обслуживании запросов абонентов в порядке их поступления.

Известно устройство для накопления поступающей информации, содержащее многоступенчатый сдвигающий накопитель, блок опроса и элементы И .

Входящий в схему дополнительный регистр для хранения информации, находящейся на обслуживании, снижает надежность устройства

Известно буферное запоминающее устройство, содержащее последовательно соединенные группы запоминающих ячеек и управляющие ячейки, соответствующие каждой такой группе и состоящие из бист бильного элемента памяти, элемента совпадения и элемента сзадержки Г2 .

В таком устройстве передача информа-. ции к группе свободных запоминающих ячеек проводится через пред1иествующих ячеек, что снижает бьютродействие схемы.

Наиболее близким к данному техническому решению является буферное запоминающее устройство, содержащее матрицу запоминающих регистркэв, установо ные входы KOTOpbJX соединены с выходами первых элементов И, первые входы которых, подключены ко входным шинам устройства, а вторые входы - к инверсным выходам регистра управления, установочные входы которого подключены к выходам первых элементов ИЛИ, входы которых соединены с инверюными выходами соответствующих запоминающих регистров зЗ .

Недостатком известного устройства является ограниченное быстродействие иэ-за последовательного срабать1вания регистров и задержки обработки очередного запроса абонента.

Целью настоящего изобретения является повыщеиие быстродействия и надежности устройства.

Поставленная цель достнгпстся тем, что в буферное запоминаются vcrpoiV-Too

введены распределитель импульсов, формирователи импульсов, элементы И и элементы ИЛИ, прямые выходы регистра управления соединены с третьими входа ми первых элементов И соответствующих запоминающих регистров и со входами второго элемента ИЛИ, выход которого подключен к управляющему входу распре- делителя импульсов, выходы которого под ключены ко входам соответствующих формирователей импульсов и к первым входам вторых элементов И, вторые входы которых соединены с прямыми выходами соответствующих запоминающих регистров а выходы вторых элементов И соединены со входами третьих элементов ИЛИ, вь ходы которых подключены к выходным шинам устройства, вькоды формирователей импулЕзсов соединены с соответствующими входами сброса запоминающих регистров к регистра управления, инверсный выход последне1Т1 разряда которого подюгючен к первьм входам третьих элементов й, . вторые входы которых подключены к прямым выхойЬм регистра управления, кроме первого и последнего, а выходы третьих элементов И соединены со входами четвертого элемента ИЛИ, выход которого роединен с третьими входами первых элементов И первого запоминающего регистра.

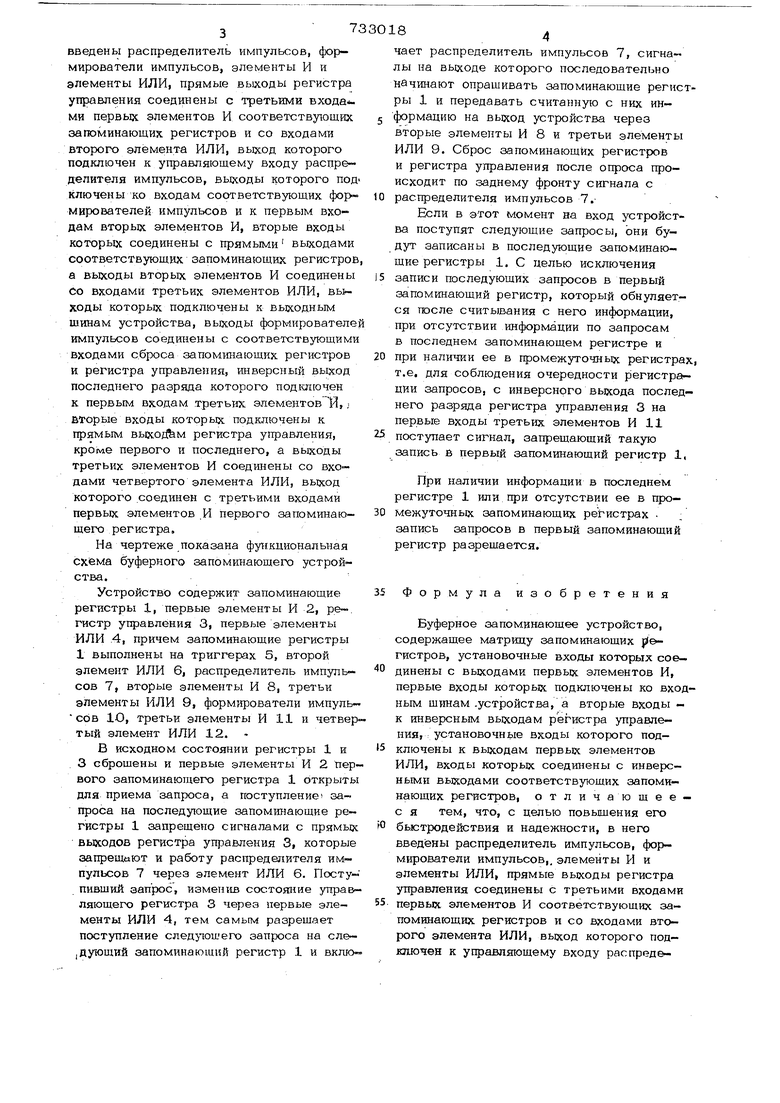

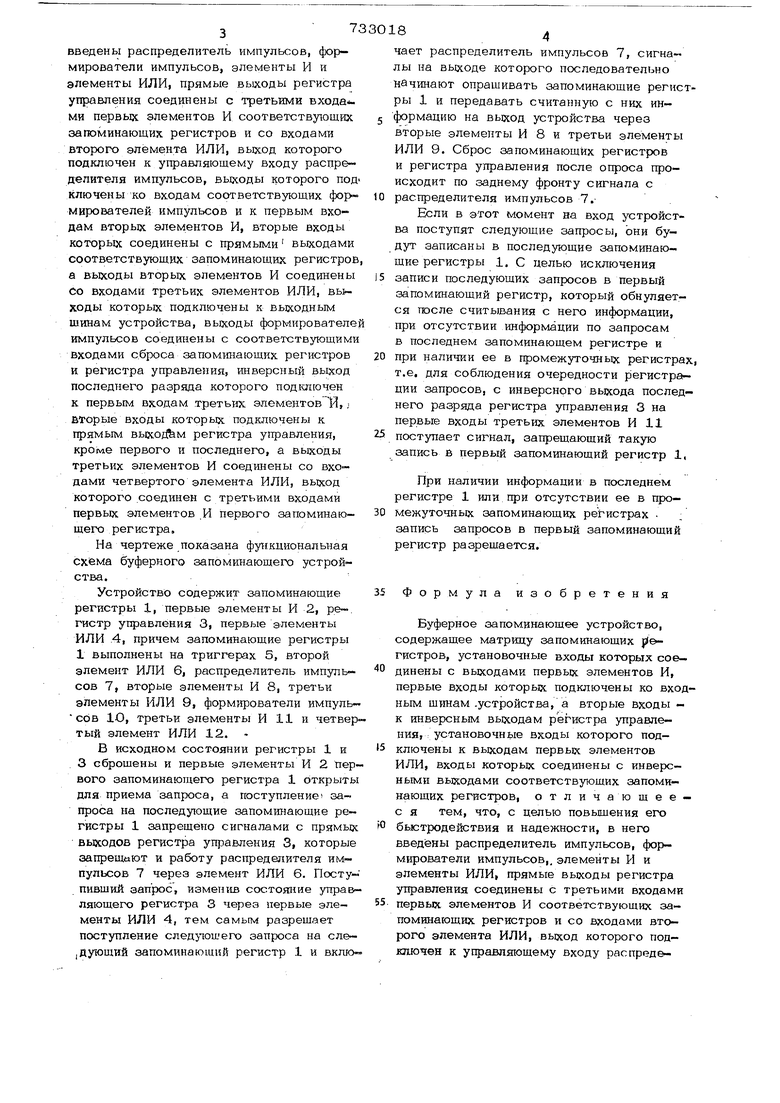

На чертеже показана функциональная схема буферного запоминающего устройства.

Устройство содержит запоминающие регистры 1, первые элементы И 2, ре-. гистр управления 3, первые элементы ИЛИ .4, причем запоминающие регистры 1 выполнены на триггерах 5, второй элемент ИЛИ 6, распределитель импульсов 7, вторые элементы И 8, третьи элементы ИЛИ 9, формирователи импульсов Ю, третьи элементы И 11 и четвертый элемент ИЛИ 12. В исходном состоянии регистры 1 и 3 сброшены и первые элементы И 2 первого запоминающего регистра 1 открыты для приема запроса, а поступление запроса на последующие запоминающие регистры 1 запрещено сигналами с прямых выходов регистра управления 3, которые запрещают и работу распределителя импульсов 7 через элемент ИЛИ 6. Поступивший запрос, изменив состояние управляющего регистра 3 через первые элементы ИЛИ 4, тем самым разрешает поступление следующего запроса на еле- ,дующий запоминающий регистр 1 и вклю

чает распределитель импульсов 7, сигналы на выходе которого последовательно начинают опрашивать запоминающие регистры 1 и передавать считанную с них ин-

формацию на выход устройства через вторые элементы И 8 и третьи элементы ИЛИ 9. Сброс запоминающих регистров и регистра управления после опроса происходит по заднему фронту сигнала с

распределителя импульсов 7.

Если в этот момент на вход устройства поступят следующие запросы, они будут записаны в последующие запоминающие регистры 1. С целью исключения

записи последующих запросов в первый запоминающий регистр, который обнуляется госле считывания с него информации, при отсутствии информации по запросам в последнем запоминающем регистре и

при наличии ее в промежуточных регистрах, т.е. для соблюдения очередности р1егистрации запросов, с инверсного выхода последнего разряда регистра управления 3 на первые входы третьих элементов И 11

поступает сигнал, запрещающий такую

запись в первый запоминающий регистр 1,

При наличии информации в последнем регистре 1 или при отсутствии ее в промежуточных запоминающих регистрах . : запись запросов в первый запоминающий регистр разрешается.

35 Формула изобретения

Буферное запоминающее устройство, содержащее матрицу запоминающих р&гистров, установочные входы которых соединены с выходами первых элементов И, первые входы которых подключены ко входным шинам .устройства, а вторые входы к инверсным выходам регистра управления,/установочные входы которого подключены к выходам первых элементов ИЛИ, входы которых соединены с инверс- нь1ми вькодами соответствующих запоминающих регистров, отличающеес я тем, что, с целью повыщения его быстродействия и надежности, в него введены распределитель импульсов, формирователи импульсов,, элементы И и элементы ИЛИ, прямые вь1ходы регистра управления соединены с третьими входами первых элементов И соответствующих запоминающих регистров и со входами второго элемента ИЛИ, выход которого подключен к управляющему входу распреде-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения измерительного прибора с цифровой вычислительной машиной | 1981 |

|

SU1013940A1 |

| Устройство для управления записью и считыванием информации | 1981 |

|

SU1014028A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287238A1 |

| Автоматизированный класс для контроля знаний обучаемых | 1981 |

|

SU963065A1 |

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

| Буферное запоминающее устройство | 1977 |

|

SU769621A1 |

| Дискретно-цифровой электропривод | 1985 |

|

SU1350800A1 |

| Многоканальное устройство для прерывания программ | 1983 |

|

SU1124301A1 |

| Устройство сопряжения | 1981 |

|

SU1121667A1 |

Авторы

Даты

1980-05-05—Публикация

1977-10-12—Подача