1

Предложенное изобретение относится к области вычислительной техники и -может быть использовано при построении устройств храпения дискретной информации.

Известно буферное запоминающее устройство, содержащее регистры хранения чисел, логические эле.менты «И п управляющий двухтактный регистр сдвига.

Основным недостатком известного устройства является необходимость наличия схем, вырабатывающих код адреса для управления устройством, и большое число элементов па.мяти, позволяющих хранить весь объем поступающей информации.

Целью изобретения является «повыщение плотности записи и упрощение известного буферного запоминаюн1,его устройства.

Поставленная цель достигается путем того, что нулевой выход каждого основного триггера управляющего регистра сдвига, кроме первого, подключен к элементу «И предыдущего разряда этого регистра, а выход элемента «И каждого разряда управляющего регистра сдвига соединен с пулевым входом вспомогательного триггера того же разряда, с единичным входом вспомогательного триггера последующего разряда и со входами соответствуюншх элементов «И регистров хранения чисел.

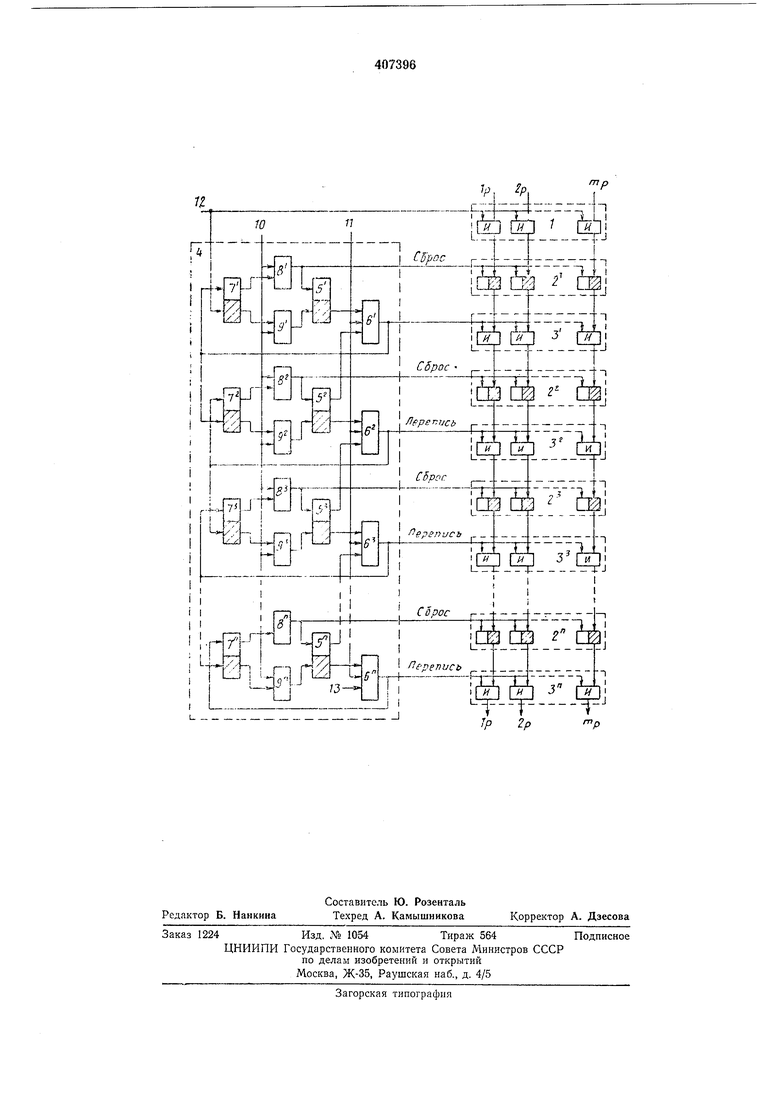

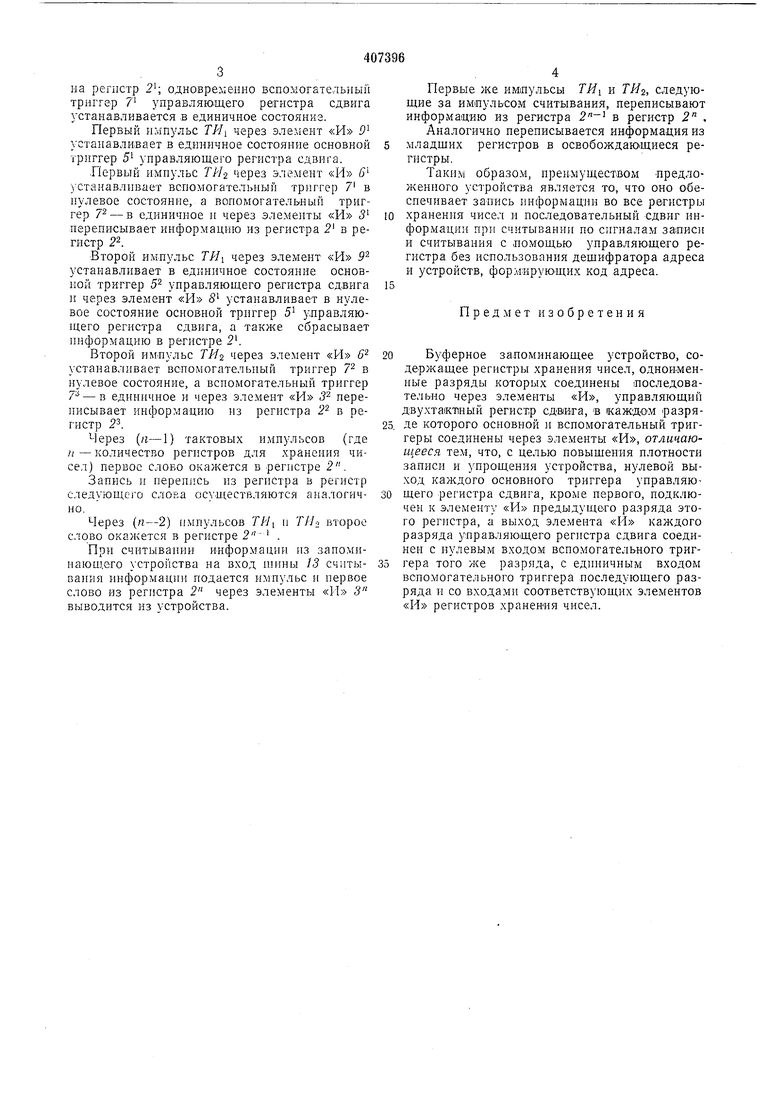

На чертеже изображена функциональная

схема предложенного буферного запоминающего устройства.

Устройство содержит элемеиты «И /, регистры 2-2 хранения т-разрядных чнсе., соединенные через элементы «И 5-3, управляющий двухтактный регистр сдвига 4. выключающий в себя 010но1вные триггеры 5-5, подключенные ко входам элементов «1-Ь (;-6, и вспомогательные триггеры 7-7 , подключенные ко входам элементов «И } элементов «И .9-.9 .

Ко входам элементов «И 8, 9 подключена шина 0 тактовых импульсов ГЯь Ко входа:, элементов «И 5 подключена щина 11 тактовых им.пульсов Т И 2. Ко входам элементов «И 1 и вспомогательного триггера 7 подключена шина 12 записи информации. Ко входу элемента «И 6 подключена ниша 13 считывания информации.

Предложенное устройство работает след ющим образом.

На шину 10 тактовых имнульсов ГЯ, н шину 11 тактовых н.мпульсов ТИ постоянно поступают импульсы, сдвинутые один относительно другого, частота которых не ниже возмолшой частоты заииси информации.

Для записи информации в запоминающее устройство на шину 12 записи информации поступает импульс, по которому через элементы «PI 1 первое т-разрядное слово записывается

на регистр 2; одновре:,:енно вспомогательный трштер 7 управляющего регнстра сдвига }станавливается в единичное состояние.

Первый импульс THi через элемент «И 5 устанавливает в единичное состояние основной триггер 5 управляющего регистра сдвига.

-Первый импульс 77/2 через элемент «И 5 ;устанавлнвает вспомогательный триггер 7 в нулевое состояние, а вспомогательный триггер 7 - в единичное и через элементы «И 5 нереписывает информацию из регистра 2 в регистр 2.

Второй импульс Г// через элемент «И 9 устанавливает в единичное состояние основной триггер 5 унравляющего регистра сдвига и через элемент «И 5 устанавливает в нулевое состояние основной триггер 5 управляющего регистра сдвига, а также сбрасывает информацию в регистре 2.

Второй имлульс ГЯг через элемент «И 6 устанавливает вспомогательный триггер 7 в нулевое состояние, а всномогательиый триггер 7 - в единичное и через элемент «И 3 переписывает информацию из регнстра 2 в регистр 21

Через (п-1) тактовых импульсов (где п - количество регистров для хранеиия чисел) первое слово окажется в регистре 2.

Запись перепись из регнстра в регистр следующоо слова осуществляются аналогично.

Через (п-2) импульсов TWi и Г//о второе слово окажется в регистре 2 .

При считывании информации из заиомннаюи.его устройства на вход шины 13 считывания информации подается импульс и первое слово из регистра 2 через элементы «II 3 выводится из устройства.

Первые же импульсы ТИ и THz, следующие за импульсом считывания, переписывают информацию из регистра в регистр 2 . Аналогично иереписывается информадия из

младщих регистров в освобождающиеся регистры.

Таким образом, преимуществом лредложенного устройства является то, что оно обеспечивает запись информации во все регистры

хранения чисел и последовательный сдвиг информации при считывании по сигналам записи и считывания с помощью унравляющего регистра без использования дещифратора адреса и устройств, фор.мирующих код адреса.

Предмет изобретения

Буферное запоминающее устройство, содержащее регистры хранения чисел, одноименные разряды которых соединены последовательно через элементы «И, управляющий двухтакпиый регистр сдвига, в каждо-м разряде которого основной и всиомогательный триггеры соединены через элементы «И, отличающееся тем, что, с целью новыщения плотности записи и упрощения устройства, нулевой выход каждого основного триггера управляющего регистра сдвига, кроме первого, подключен к элементу «И предыдущего разряда этого регистра, а выход эле.мента «И каждого разряда управляющего регистра сдвига соединен с нулевым входом вспомогательного триггера того же разряда, с едииичным входом вспомогательного триггера последующего разряда п со входа.ми соответствующих элементов «И регистров хранеш-ш чисел.

It

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1978 |

|

SU746720A1 |

| Буферное запоминающее устройство | 1976 |

|

SU750565A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| Постоянное запоминающее устройство с фазо-импульсным представлением чисел | 1976 |

|

SU627542A1 |

| Блок управления для буферного запоминающего устройства | 1974 |

|

SU616654A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Буферное запоминающее устройство | 1977 |

|

SU739645A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Буферное запоминающее устройство | 1981 |

|

SU982094A2 |

ГI

У

т-л i4;qЛ

I

-ij

-

„dJ

I // I И

1р 2р

Даты

1973-01-01—Публикация

1972-08-28—Подача