(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU824418A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Устройство для умножения частоты следования периодических импульсов | 1981 |

|

SU1005285A2 |

| Устройство для умножения частотыСлЕдОВАНия пЕРиОдичЕСКиХиМпульСОВ | 1979 |

|

SU824419A2 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Устройство умножения частоты следованияиМпульСОВ | 1979 |

|

SU822327A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU945962A1 |

| Устройство для умножения частоты следования периодических импульсов | 1978 |

|

SU769720A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

Изобретение относится к автоматике измерительной и вычислительной технике в частности к устройствам, предназначенным для генерирования импульсной последовательности методом умножения и .может быть использовано для повышения быстродействия низкочастотных измерительных устройств при обработке сигналов частотных датчиков, для измерения частоты наиболее просты.м методо.м - непосредственным счетом периодов за калиброванный интервал времени.

Известно устройство для умножения частоты следования импульсов, содержащее две схемы измерения периодов умножаемой частоты, две с. генерации умноженной последовательности импульсов и схему блокированияТЛНаиболее близким по своей сущности те.чническим решением к изобретению является устройство для умножения частоты импульсной последовательности, содержащее делигель опорной частоты с коэ(Ьфициентом деления К, равным коэфсЬнциеитч умножения, счетчик импульсов, входной i .ыходной формирователи, счетчик импульсов опорной частоты, блок управлеь{ия,- логические схемы И. запо.минающий регистр 2.

Недостатко.м данного устройства является накапливающаяся от периода к период} ошибка временного расположения импульсов умноженной частоты по отношению к периоду умножаемой частоты. Известно, что счетчик импульсов может насчитать-число импульсов менынее на один, чем действительное чис.ю периодов. С,тедовательно, счетчик импу.1ьсов опорной частоты формир ет мпульсы множенной частоты с у.меньiiieiijii,iM периодом следования, и К-ый имny.ibc сформируется panbnie окончания период; умножаемой частоты, что приводит к ч;1стогной оишбке умноженной частоты. Эт; ошибка накапливается, и через несколько ис1)иодов умножаемой частоты импульсь .,;iii,icM 15 счетчик импульсов опорной частоты и импу,1ьсы обнуления регистра будут р;к-М1)Ложены б.шзко или совпадут, что приBe.i.T к потере целого периода, т. е. произоГмет «сб()Г|.

i 1,е,1ь изобрс iii.i - повьпиение точность- умножения частоты.

Поставленная цель достигается гем, что в умножитель частоты, содержащий делитель опорной частоты, вход которого подключен к шине опорной частоты, а выход - ко входу счетчика импульсов, управляй ш,ий которого через блок управления соединен с формирователем входного сигнала, а информационные выходы через запоминающий резистор связаны с информационными входами счетчика импульсов опорной частоты, вход которого соединен с шиной опорной частоты, введены дешифратор, триггер и элемент ИЛИ, первый вход которого подключен к выходу дополнительного разряда счетчика импульсов, второй вход - к первому выходу блока управления, а выход - ко входу записи информации запоминающего регистра и ко входам сброса делителя опорной частоты и счетчика импульсов опорной частоты, выходы которого подключены ко входам дешифратора, а первый выход дешифратора подключен ко входу записи информации счетчика импульсов опорной частоты и ко входу триггера, другой вход которого подключен ко второму выходу дещифратора.

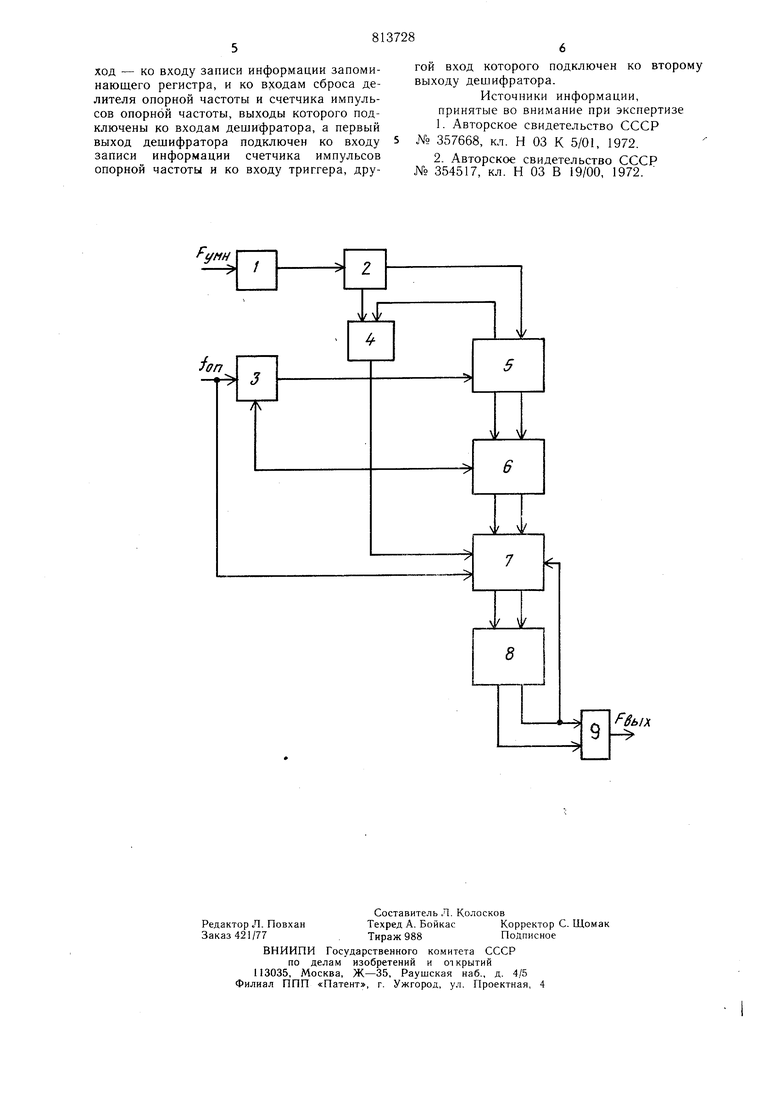

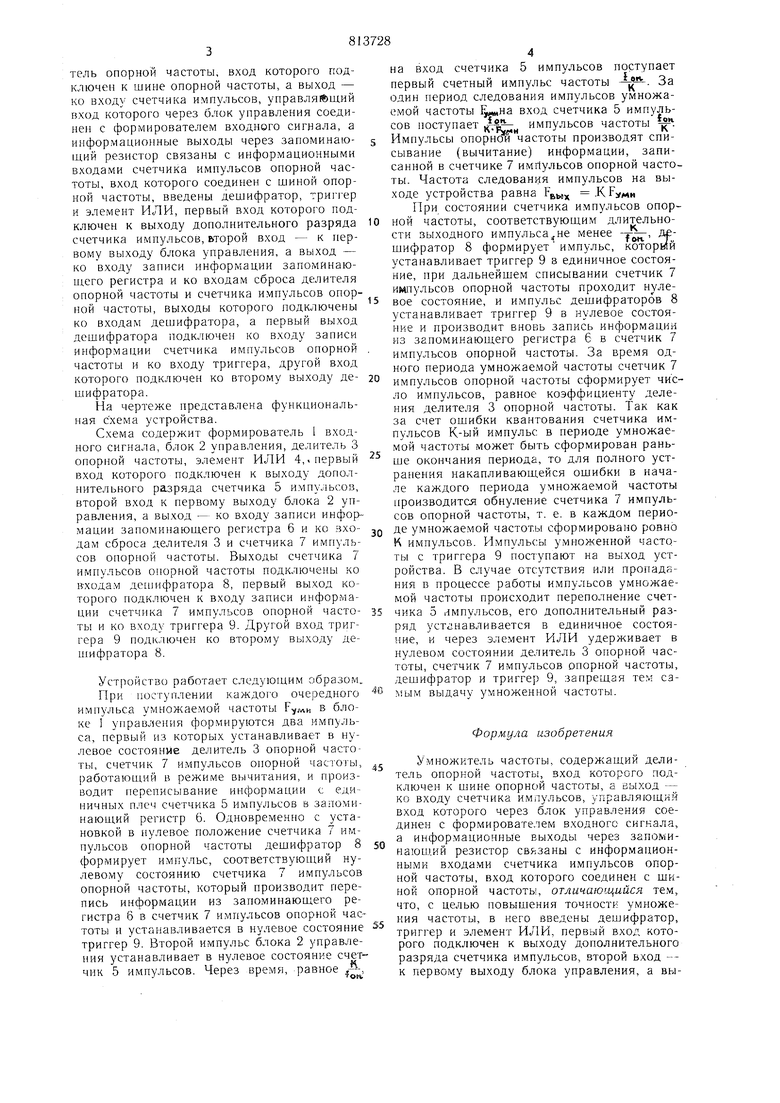

На чертеже представлена функциональная схема устройства.

Схема содержит формирователь 1 входного сигнала, блок 2 управления, делитель 3 опорпой частоты, элемент ИЛИ 4,. первый вход которого подключен к выходу дополнительного разряда счетчика 5 импульсов, второй вход к первому выходу блока 2 управления, а выход - ко входу записи информации запоминающего регистра 6 и ко входам сброса делителя 3 и счетчика 7 импульсов опорной частоты. Выходы счетчика 7 импульсов опорной частоты подключены ко входам дешифратора 8, первый выход которого подключен к входу записи информации счетчика 7 импульсов опорной частоты и ко входу триггера 9. Другой вход триггера 9 подключен ко второму выходу дешифратора 8.

Устройство работает следую цим образом.

При поступлении каждого очередного импульса умножаемой частоты в блоке 1 управления формируются два импульса, первый из которых устанавливает в нулевое состояние делитель 3 опорной частоты, счетчик 7 импульсов опорной частоты, работающий в режиме вычитания, и производит переписывание информации с единичных плеч счетчика 5 импульсов в запоминающий регистр 6. Одновременно с установкой в нулевое положение счетчика 7 импульсов опорной частоты дешифратор 8 формирует импульс, соответствующий нулевому состоянию счетчика 7 импульсов опорной частоты, который производит перепись информации из запоминающего регистра 6 в счетчик 7 импульсов опорной частоты и устанавливается в нулевое состояние триггер 9. Второй импульс блока 2 управления устанавливает в нулевое состояние счетчик 5 импульсов. Через время, равное -,

на вход счетчика 5 импульсов поступает первый счетный импульс частоты За один период следования импульсов умножаемой частоты вход счетчика 5 импульсов поступает ) импульсов частоты .

Импульсы опорнои частоты производят списывание (вычитание) информации, записанной в счетчике 7 импульсов опорной частоты. Частота следования импульсов на выходе устройства равна -КРумн

При состоянии счетчика импульсов опорной частоты, соответствующим длительности выходного импульса не менее -f, АРшифратор 8 формирует импульс, котормй устанавливает триггер 9 в единичное состояние, при дальнейшем списывании счетчик 7 импульсов опорной частоты проходит нулевое состояние, и импульс дешифраторов 8 устанавливает триггер 9 в нулевое состояние и производит вновь запись информации из запоминающего регистра 6 в счетчик 7 импульсов опорной частоты. За время одного периода умножае.мой частоты счетчик 7

импульсов опорной частоты сформирует число импульсов, равное коэффициенту деления делителя 3 опорной частоты. Так как за счет ошибки квантования счетчика импульсов К-ый импульс в периоде умножаемой частоты может быть сформирован раньше окончания периода, то для полного устранения накапливающейся ошибки в начале каждого периода умножаемой частоты производится обну.аение счетчика 7 импульсов опорной частоты, т. е. в каждом периоде умножаемой частоты сформировано ровно К импульсов. Импульсы умноженной частоты с триггера 9 поступают на выход устройства. В случае отсутствия или пропадания в процессе работы импульсов умножаемой частоты происходит переполнение счетчика 5 импульсов, его дополнительный разряд устанавливается в единичное состояние, и через элемент ИЛИ удерживает в нулевом состоянии делитель 3 опорной частоты, счетчик 7 импульсов опорной частоты, дешифратор и триггер 9, запрещая тем выдачу умноженной частоты.

Формула изобретения

j Умножитель частоты, содержащий делитель опорной частоты, вход которого подключен к шине опорной частоты, а выход - ко входу счетчика импульсов, управляющий вход которого через блок управления соединен с формирователегй входного сигнала, а информационные выходы через запоминающий резистор связаны с информационными входами счетчика импульсов опорной частоты, вход которого соединен с шиной опорной частоты, отличающийся тем, что, с целью повышения точности умиожеj ния частоты, в него введены дешифратор, триггер и элемент ИЛИ, первый вход которого подключен к выходу дополнительного разряда счетчика импульсов, второй вход -к первому выходу блока управления, а выход - ко входу записи информации запоминающего регистра, и ко входам сброса делителя опорной частоты и счетчика импульсов опорной частоты, выходы которого подключены ко входам дешифратора, а первый выход дешифратора подключен ко входу записи информации счетчика импульсов опорной частоты и ко входу триггера, другой вход которого подключен ко второму выходу дешифратора.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-03-15—Публикация

1979-04-09—Подача