1

Изобретение относится к области электроники и вычислительной техники и может найти широкое применение при построении интегральных схем на МДПприборах.5

Известно выходное устройство, содержащее парафазный каскад и инвертор с предварительно заряжающим транзистором иемкостной положительной обратной связью. Недостатком известно- 10 .го устройства является уменьшение напряжения на выходе парафазного каскада по сравнению с напряжением питания.

Известно выходное устройство, со- tS держащее парафазный каскад, инвертор с предварительно заряжающим транзистором, емкостной положительной обратной связью и дополнительный конденсатор с зарядной цепью из двух последо-20 вательно включенных транзисторов, на выходе которого напряжение не отличается от напряжения питания. Недостаток устройства заключается в его узких функциональных возможностях, по- 25 скольку оно не может надежно работать при произвольном коде входной информации. Так, например, при длительном непрерывном поступлении на вход напряжения логического нуля 30

происходит разряд емкости обратной . связи с помощью токов утечки, что приводит к изменению выходного напряжения и, в результате, к искажению инфор ации.

Целью изобретения является расширение функциональных возможностей .устройства.

Для достижения поставленной цели в выходное устройство на МДП - транзисторах, содержащее включенные между первой шиной питания и общей шиной инвертор, вход которого подк.гаочен ко входной шине, и выходной парафазный каскад, выход которого подключен к выходной шине, дополнительно введены два парафазных каскада, ВДП-конденсатор, два передаточных транзистора, вторая шиНа питания и две шины тактовых сигналов, причём сток первого передаточного транзистора подключён ко входной шине, затвор - к первой шине тактовых сигналов и к затвору нагрузочного транзистора инвертора, а исток - к прямому входу первого парафазного каскада с емкостной положительной обратной связью, включенного между второй шиной тактовых сигнгтов и общей шиной, выход инвертора подключен к инверсному

входу первого па Ьафазного каскада, к первой обкладке ВДП-конденсатора и к прямому входу второго парафазного каскада, включенного меящу второй шиной питания и общей шиной, выход второго парафазного каскада подключен к прямому входу вьоходного парафазного каскада, выход первого парафазного каскада через второй передаточный транзистор подключен к инверсным входам второго и выходного парафазных каскадов, затвор второго передаточного транзистора подключен ко второй обкладке МДП-конденсатора и ко второй шине тактовых сигналов.

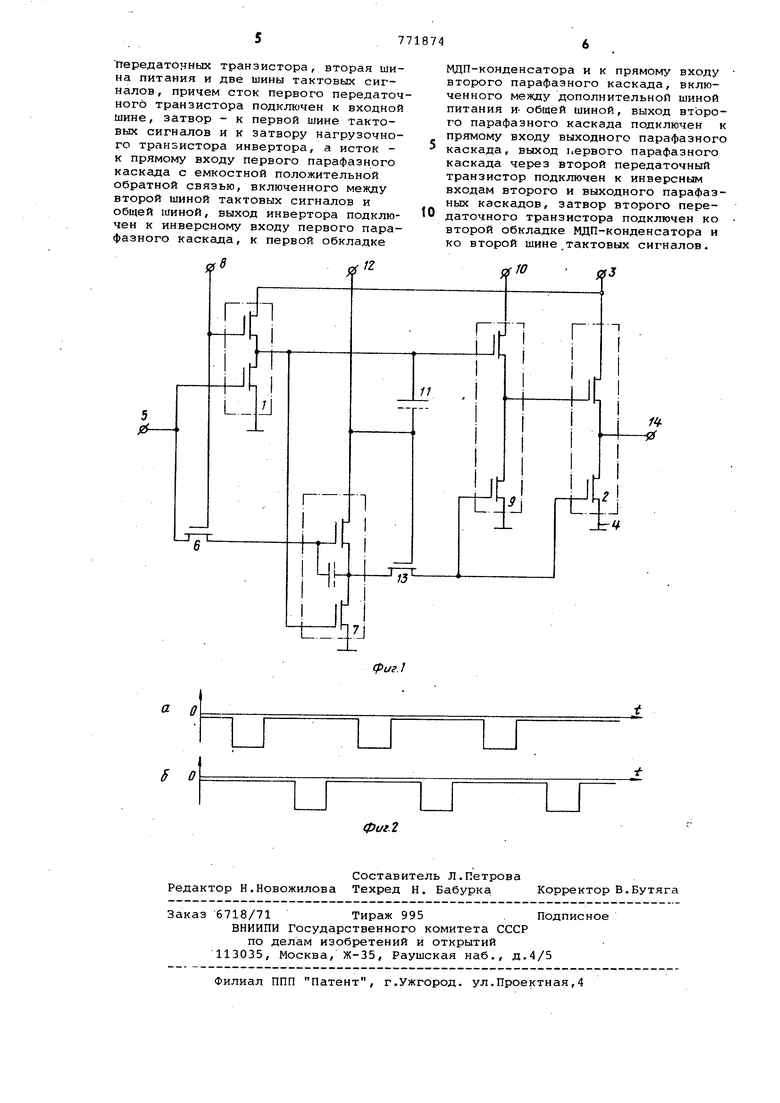

На (Ьиг.1 представлена электрическая принципиальная схема устройства; на фиг,2 - временные диаграммы тактовых сигналов на первой (а) и второй (б) шинах тактовых сигналов.

Инвертор 1 и выходной парафазный каскад 2 включены между первой шиной питания 3 и общей шиной 4, вход инвертора 1 подключен ко входной шине устройства и через первый передаточный транзистор 6 - к прямому входу первого парафазного каскада 7 с емкостной положительной обратной связь затвор нагрузочного транзистора инвертора 1 подключен к затвору транзистора 6 и к первой шине 8 тактовых сигналов, выход инвертора 1 подключен к инверсному входу первого парафазного каскада 7, к прямому входу второго парафазного каскада 9, включенного между второй шиной питания 10 и общей шиной 4, и к первой обкладке МДП-конденсатора 11. Вторая обкладка МДП-конденсатора 11 подключена ко второй шине тактовых сигналов 12 и к затвору второго передаточного транзистора 13, включенного между выходом парафазного каскада 7 и инверсньами входами парафазных каскадов 2 и 9. Парафазный каскад 7 включен между шиной 12 и общей шиной 4. Выход парафазного каскада 9 подключен к прямому входу парафазного каскада 2, а выход парафазного каскада 2 - к выходной шине 14.

Устройство работает следующим образом.

Если на входную щину 5 поступает напряжение логического О, то во время действия тактового сигнала на шине 8 через транзистор 6 на прямой вход парафазного каскада 7 передается напряжение логического О. В это время с выхода инвертора 1 на инверсный вход парафазного каскада 7, на прямой вход парафазного каскада 9 и на первую обкладку МДП-конденсатора 11 -поступает напряжение логической 1. Значение емкости МДП-конденсатора 11 при этом максимальное, так как под его затвором существует канал, служащий второй обкладкой ВДПконденсатора. Во время действия тактового сигнала на шине 12 через МДП. конденсатор 11 на прямой вход парафазного каскада 9 и инверсный вход парафазного каскада 7 поступает дополнительное напряжение. Поэтому с выхода парафазного каскада 9 на прямой вход выходного парафазного кас-. када 2 поступает напряжение логической единицы, равное напряжению второ шины питания 10. На инверсные входы парафазных каскадов 2 и 9 с выхода парафазного каскада 7 через транзистор 13 поступает напряжение логического О. В итоге на ввлходной шине 14 устанавливается напряжение логической 1, равное напряжению первой шины питания 3. Если на входной шине 5 - напряжение логической 1, то во время действия тактового сигнала на шине 8 через передаточный транзистор б на прямой вход парафазного каскада 7 передается напряжение логической 1. В это время с выхода инвертора 1 на прямой вход парафазного каскада 9, на инверсный вход парафазного каскада 7 и на первую обкладку МДП-конденсатора 11 поступает напряжение логического О.Значение емкости МДП-конденсатора при этом минимальное из-за отсутствия канала под его затвором. Поэтому во время действия тактового сигнала на шине 12 на прямой вход парафазного ;Каскада 9 не передается дополнитель ное напряжение. В это время на инверсные входы второго 9 и выходного 2 парафазных каскадов через передаточный транзистор 13 с выхода парафазного каскада 7 поступает напряжение логической 1. В результате на пря.мЬм входе выходного парафазного каскада 2 и на выходной шине 14 устанавливается напряжение логического О.

Таким образом, дополнительно введенные в выходное устройство два парафазных каскада, два передаточных транзистора, МДП-конденсатор, вторая шина питания и две шины тактовых сигналов обеспечивают более широкие функциональные возможности, а именно, устройство может надежно работать при любом коде входного сигИРала При этом в нем сохранены высокая нагрузочная способность и малая длительность фронта нарастания выходного напряжения, так как на прямой вход выходного парафазного каскада передается полностью напряжение источника питания.

Формула изобретения

Выходное устройство на МДП-транзисторах, содержащее включенные между первой шиной питания и общей шиной инвертор, вход которого подключен ко входной шине и выходной парафазный каскад, выход которого подключен к. выходной шине, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей в него дополнительно введены два. парафазных каскада, МДП-кснденсатор,два

передатонных транзистора, вторая шина питания и две шины тактовых сигналов , причем сток первого передаточного транзистора подключен к входной шине, затвор - к первой шине тактовых сигналов и к затвору нагрузочного транзистора инвертора, а исток к прямому входу первого парафазнрго каскада с емкостной положительной обратной связью, включенного между второй шиной тактовых сигналов и общей шиной, выход инвертора подключен к инверсному входу первого парафазного каскада, к первой обкладке

МДП-конденсатора и к прямому входу второго парафазного каскада, включенного между дополнительной шиной питания и- общей шиной, выход второго парафазного каскада подключен к прямому входу выходного парафазного каскада, выход первого парафазного каскада через второй передаточный транзистор подключен к инверсным входам второго и выходного парафазных каскадов, затвор второго пере0даточного транзистора подключен ко второй обкладке МДП-конденсатора и ко второй шине.тактовых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное устройство | 1979 |

|

SU822366A1 |

| Буферное устройство | 1977 |

|

SU622204A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Источник питания | 1980 |

|

SU900376A1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| Выходное устройство на мдп транзисторах | 1975 |

|

SU547970A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

Авторы

Даты

1980-10-15—Публикация

1978-01-10—Подача