(54) ВЫХОДНОЕ УСТРОЙСТВО НА МДП ТРАНЗИСТОР АХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Буферное устройство | 1979 |

|

SU822366A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Буферное устройство | 1977 |

|

SU622204A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Источник питания | 1980 |

|

SU900376A1 |

| Формирователь импульсов | 1984 |

|

SU1170599A1 |

| Способ хранения информации на МДП-транзисторе и запоминающий элемент для осуществления этого способа | 1977 |

|

SU943846A1 |

1

Изобретение относится к импульсной технике и может быть использовано в циф ровой вычислительной технике.

Известны схемы выходных устройств на МДИ-трапзисторах, содержащие парафазлый оконечный усилитель, загвор одного из транзисторов связи с выходом предложенного нарафаз1 ого усили-теля, затвор другого связан с затвором одного из транзисторов предложенного парафаз шго усилит ля п через тактируемый транзистор с выходом инвертора с тактируемым нагрузочным транзистором, вход которого связан с выходONi тактируемого транзистора и затвором второго транзисторапередаточно го парафазного усилителя 1.

Также известно выходное устройство на МДП-транзисторах, содержащее нарафааный конечный каскад и два динамических повторителя, причем вход первого подключе ко входу выходного устройства на МДП-Тра зисторах через гактиру мый передаточный трацзнсто, вход второго - к выходу тактируемог-0 инвертора, вход которого подклюhen ко входу устройства 2.

Известные входные устройства на МДПтранзисторах не обеспечивают получение выходной информации в потенциальной форме.

Цель изобретения - получение выходной информации в потенциальной форме.

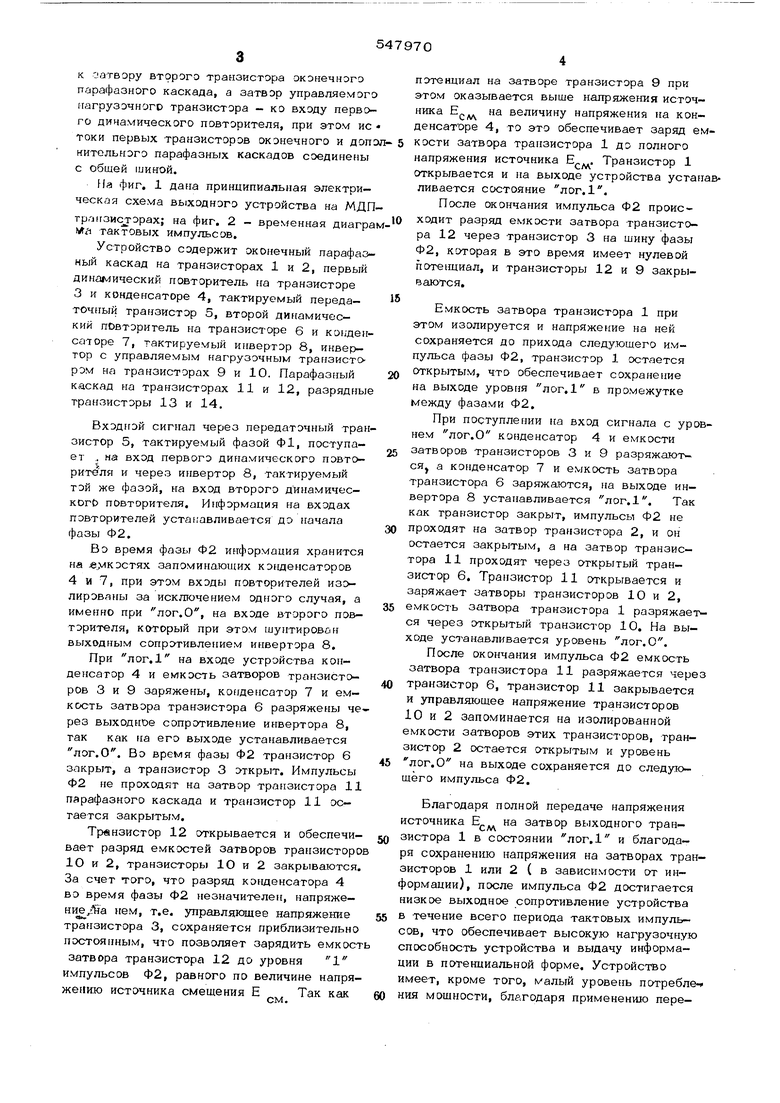

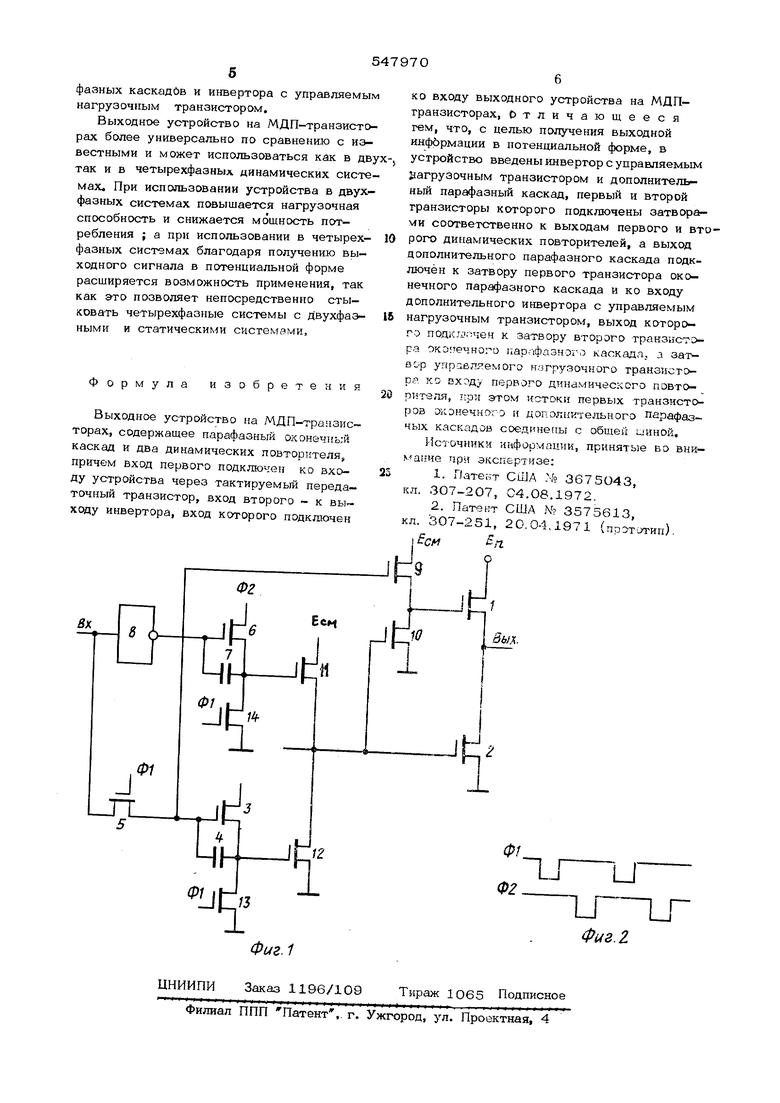

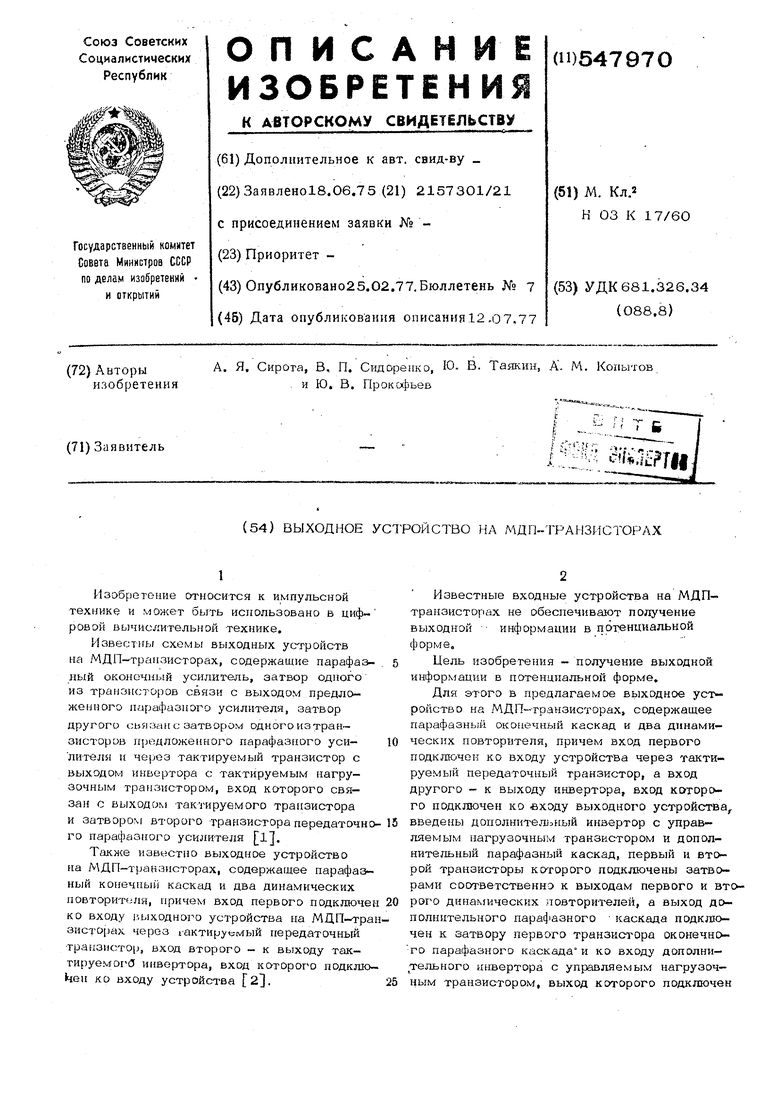

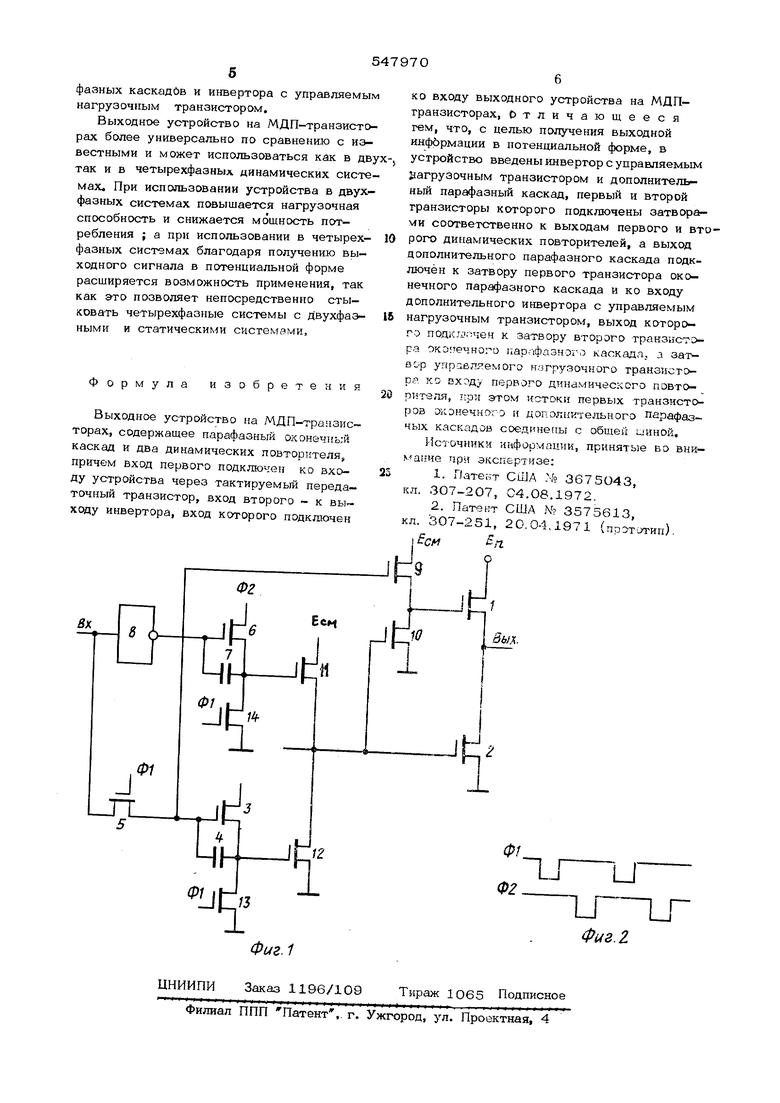

Для этого в предлагаемое выходное уоройство на МДП-транзисторах, содержащее парафазньй оконечный каскад и два динамических повторителя, причем вход первого подключен ко входу устройства через тактируемый передаточный транзистор, а вход другого - к выходу инвертора, вход которого подключен ко еходу выходного устройства введены дополни1 ел ный инвертор с управляемым нагрузочным транзистором и дополнительный парафааный каскад, первый и второй транзисторы которого подключены затворами соответственно к выходам первого и втрого динамических повторителей, а выход дополнительного парафазного каскада подключен к затвору первого транзистора оконечного парафааного каскадаи ко входу дополнительного инвертора с управляемым нагрузочным транзистором, выход которого подключен к затвору второго транзистора оконечного гтарафазного каскада, а затвор управляемог нагрузочного транзистора - ко входу перво го динамического повторителя, при этом ис токи первых транзисторов оконечного и доп кительного парафазных каскадов соединены с обшей шиной. На фиг, 1 дана принципиальная электрическая схема вьJXOднoгo устройства на МДП rp.jFroMCTOpax; на фиг, 2 (енная диагра 1/л тактовых импульсов. Устройство содержит оконечный парафазный каскад на транзисторах 1 и 2, первый динамический повторитель на транзисторе 3и конденсаторе 4, тактируемый передаточный транзистор 5, второй динамический повторитель на транзисторе 6 и конден саторе 7, тактируемый инвертор 8, инвертор с управляемым нагрузочным транзистором на транзисторах 9 и 10. Парафазный каскад на транзисторах 11 и 12, разрядргы транзисторы 13 и 14. Входной сигнал через передаточный тран зистор 5, тактируемый фазой Ф1, поступает .. на вход первого динамического повторителя и через инвертор 8, тактируемый той же фазой, на вход второго динамического повторителя. Информация на входах повторителей устанавливается до начала фазы Ф2, Во время фазы Ф2 информация хранится на je iKостях запоминающих конденсаторов 4и 7, при этом входы повторителей изолированы за исключением одного случая, а именно при лог.О, на входе второго повторителя, ко-торый при этом шунтирован выходным сопро-тивлением инвертора 8, При лог,1 на входе устройства конденсатор 4 и емкость затворов транзисторов 3 и 9 заряжены, конденсатор 7 и емкость затвора транзистора 6 разряжены че рез выходное сопротивление инвертора 8, так как на его выходе устанавливается лог.О. Во время фазы Ф2 транзистор 6 закрыт, а транзистор 3 Открыт, Импульсы Ф2 не проходят на затвор транзистора 11 парафазного каскада и транзистор 11 остается закрытым, Трвнзистор 12 открывается и обеспечивает разряд емКОстей затворов транзисторо 1О и 2, транзисторы 1О и 2 закрываются. За счет того, что разряд конденсатора 4 во время фазы Ф2 незначителен, напряже- ние/йа нем, т,е, управляющее напряжение транзистора 3, сохраняется приблизительно постоянным, что позволяет зарядить емкост затвора транзистора 12 до уровня 1 импульсов Ф2, равного по величине напряжению источника смещения ЕТак как потенциал на затворе транзистора 9 при этом оказывается выше напряжения источника Е- на величину напряжения на конденсаторе 4, то это обеспечивает заряд емкости затвора транзистора 1 до полного напряжения источника Е . Транзистор 1 открывается и на выходе устройства устанавливается состояние лог,. После окончания импульса Ф2 происходит разряд емкости затвора транзистора 12 через транзистор 3 на шину фазы Ф2, которая Б это время имеет нулевой потенциал, и транзисторы 12 и 9 закрываются. Емкость затвора транзистора 1 при этом изолируется и напряжение на ней сохраняется до прихода следуюшего импульса фазы Ф2, транзистор 1 остается открытым, что обеспечивает сохранение на выходе уровня лог, 1 в промежутке между фазами Ф2, При поступлении на вход сигнала с уровнем лог.О кОЕщенсатор 4 и емкости затворов транзисторов 3 и 9 разряжаются, а конденсатор 7 и емкость затвора транзистора 6 заряжаются, на выходе инвертора 8 устанавливается лог. 1, Так как транзистор закрыт, импульсы Ф2 не проходят на затвор транзистора 2, и он остается закрытым, а на затвор транзистора 11 проходят через открытый транзистор 6, Транзистор 11 открывается и заряжает затворы транзисторов 10 и 2, емкость затвора транзистора 1 разряжается через открытый транзистор 10, На выходе устанавливается уровень лог.О. После окончания импульса Ф2 емкость затвора транзистора 11 разряжается через транзистор 6, транзистор 11 закрывается и зттравляющее напряжение транзисторов 10 и 2 запоминается на изолированной емкости затворов этих транзисторов, транзистор 2 остается открытым и уровень лог,О на выходе сохраняется до следуюшего импульса Ф2, Благодаря полной передаче напряжения источника Е на затвор выходного транзистора 1 в состоянии лог,1 и благодаря сохранению напряжения на затворах транзисторов 1 или 2 ( в зависимости от инормации), после импульса Ф2 достигается низкое выходное сопротивление устройства -течение всего периода тактовых импульсов, что обеспечивает высокую нагрузочную пособность устройства и выдачу информации в потенциальной форме. Устройство имеет, кроме того, /апый урове ь потребле- НИН мощности, благодаря применению перефазных каскадбв и инвертора с управляемы нагрузочным транзистором. Выходное устройство на МДП-транзисто рах более универсально по сравнению с известными и может использоваться как в дв так и в четырехфазных динамических систе мах. При использовании устройства в двух фазных системах повышается нагрузочная способность и снижается мощность потребления ; а при использовании в четырехфазных системах благодаря получению выходного сигнала в потенциальной форме расширяется возможность применения, так как это позволяет непосредственно стыковать четырехфазные системы с двухфазными и статическими системами. Формула изобретения Выходное устройство на МДП-транзис торах, содержащее парафазный оконечиьтй каскад и два динамических повторителя, причем вход первого подключен ко вхоДУ устройства через тактируемый передаточный транзистор, вход второго к выходу инвертора, вход которого подключен

см

-п. ко входу выходного устройства на МДПгранзисторах. Отличающееся гем, что, с целью получения выходной инфбрмации в потенциальной форме, в устройство введены инвертор с управляемым 1агрузочным транзистором и дополнительный парафазный каскад, первый и второй транзисторы которого подключены затвора ми соответственно к выходам первого и второго динамических повторителей, а выход дополнительного парафазного каскада подключён к затвору первого транзистора оконечного парафазного каскада и ко входу дополнительного инвертора с управляемым нагрузочным транзистором, выход которого подкя. к затвору второго транзнсг; ра око;течного парафазного каскада, а зат- вс-р управляемого нагрузочного транзистора ко вхэду первого динамического повто- ригеля, при э-том истоки первых транзисторов оконечного и дополнительного парафазчых каскадов соединены с общей ииной, Источники информации, принятые во внимание при экспертизе: 1.Патект США Мд 3675О43, кл. 307-2О7, 04.08.1972. 2.Патевт США № 3575613, кл. 307-251, 20.04.1971 (лрэтЛ-ип).

Авторы

Даты

1977-02-25—Публикация

1975-06-18—Подача