1

Изобретение относится к электронной технике, а именно к области, электроиной коммутационной -техники/ и может быть использовано, например, для сог.пасоваиия МДП и ТТЛ ИС.

Известно буферное устройство,содержащее оконечный парафазный каскад два предоконечных парафазных каскада и три МДП-транзистора 1.

Недостатком этого устройства является низкая нагрузочная способност

Наиболее близким к предлагаемому является буферное устройство, содержащее первый инвертор, вход которого подключен к входной шине, МДП-тран3 стор, затвор которого соединен с У1правляю1цей шиной, первый и второй пЭрафазиые каскады и оконечный парафазный касксш, прямой вход которого подключен к выходу первого парафазного каскада, а инверсный вход соединен с инверсным входом первого и с выходом второго парафазных каскадов 2.

Недостатком данного устройства является низкая нагрузочная способность.

Цель изобретения - повышение нагрузочной способности.

Для достижения этой цели в буферное устройство, содержащее первый инвертор, вход которого подключен к входной шине, МДП-транзистор, затвор которого соединен с управляющей шиной, первый и второй парафазныёкаскады и оконечный парафазный каскад, прямой вход которого подключен к выходу первого парафазного каска0да, а инверсный вход соединен с инверсным входом первого и с выходом второго парафазных каскадов, введены триггер, второй инвертор и два МДП-конденсатора, причем вход триг5гера подключен к входной шине, первый выход триггера через сток-исток МДП-транзистора подключен к инверс-. ному входу второго парафазного каскада, второй выход триггера соеди0нен с входом второго ин вертора, прялые входы первого и .второго парафазных каскадов подключены соответственно к выходам второго и первого инверторов, к которым подключены

5 первые обкладки ВДП-конденсаторов, вторые обкладки которых соединены с управляющей шиной.

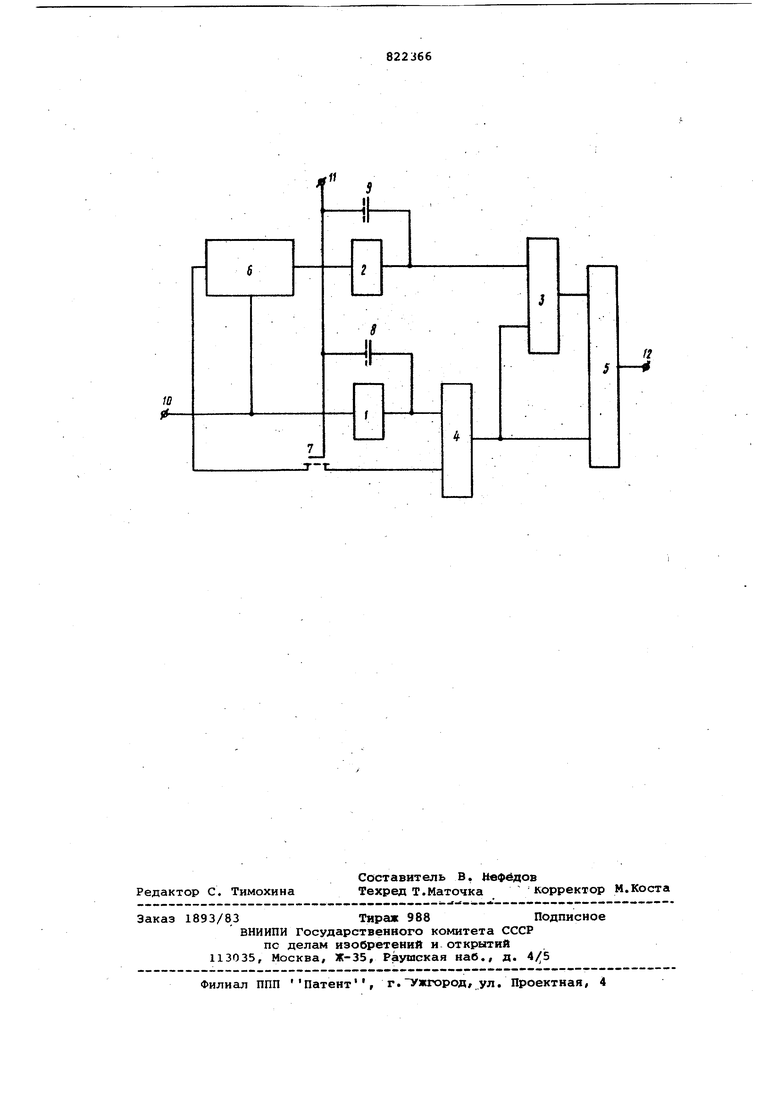

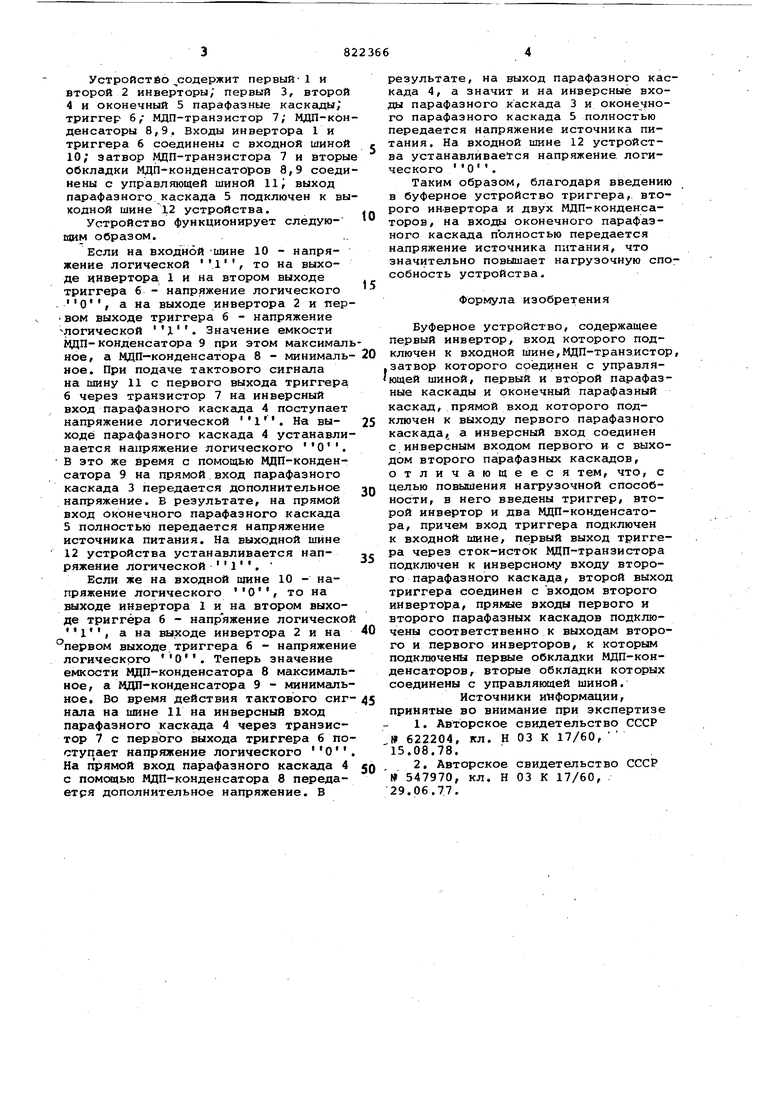

На чертеже приведена принципиальная схема буферного устройства.

0 Устройство ,содержит первый-1 и второй 2 инверторы/ первый 3, второй 4 и оконечный 5 парафазные каскады; триггер 6/ МДП-транзистор 7; МДП-кон денсаторы 8,9, Входы инвертора 1 и триггера 6 соединены с входной шиной 10; затвор адп-транзистора 7 и вторы обкладки МДП-конденсаторов 8,9 соеди нены с управляющей шиной 11j выход парафазного каскада 5 подключен к вы «одной шине 12 устройства. Устройство функционирует следующим образом. Если на входной ошне 10 - напряжение логической . , то на выходе инвертора 1 и на втором выходе триггера 6 - напряжение логического О, а на выходе инвертора 2 и пер вом выходе триггера 6 - напряжение логической . Значение емкости ВДП-конденсатора 9 при этом максимал ное, а МДП-конденсатора 8 - минималь ное. При подаче тактового сигнала на шину 11 с первого выхода триггера 6 через транзистор 7 на инверсный вход парафазного каскада 4 поступает напряжение логической . На выходе парафазного каскада 4 устанавли вается напряжение логического О. В это же время с помощью МДП-конденсатора 9 на прямой вход парафазного каскада 3 передается дополнительное напряжение. В результате, на прямой вход оконечного парафазного каскада 5 полностьк) передается напряжение источника питания. На выходной шине 12 устройства устанавливается напряжение логической . Если же на входной тине 10 - напряжение логического выходе инвертора 1 и на втором выходе триггера 6 - напряжение логической , а на выходе инвертора 2 и на первом выходе триггера б - напряжени логического . Теперь значение емкости МДП-конденсатора 8 максимальное, а МДП-конденсатора 9 - лшнимальное. Во время действия тактового сиг нала на шине 11 на инверсный вход парафаэного каскада 4 через транзистор 7 с первого выхода триггера 6 по ступает напряжение логического На прямой вход парафазного каскада 4 с помсяцью МДП-конденсатора 8 передаетря дополнительное напряжение. В результате, на выход парафазного каскада 4, а значит и на инверсные входы парафазного каскада 3 и оконечного парафазного каскада 5 полностью передается напряжение источника питания. На входной шине 12 устройства устанавливается напряжение логического О . Таким образом, благодаря введению в буферное устройство триггера,, второго ин-вертора и двух МДП-конденсаторов, на входы оконечного парафазного каскада полностью передается напряжение источника питания, что значительно повышает нагрузочную способность устройства. Формула изобретения Буферное устройство, содержащее первый инвертор, вход которого подключен к входной шине,МДП-транзистор, затвор которого срёдинен с управляющей шиной, первый и второй парафазные каскады и оконечный парафазный каскад, прямой вход которого подключен к выходу первого парафазного каскада, а инверсный вход соединен с инверсным входом первого и с выходом второго парафазных каскгщов, отличающеес ятем, что, с целью повышения нагрузочной способности, в него введены триггер, второй инвертор и два МДП-конденсатора, причем вход триггера подключен к входной шине, первый выход триггера через сток-исток ЩП-транзистора подключен к инверсному входу второго парафазного каскада, второй выход триггера соединен с входом второго инвертора, прямые входы первого и второго парафазных каскадов подключены соответственно к выходам второго и первого инверторов, к которым подключены первые обкладки МДП-конденсаторов, вторые обкладки которых соединены с управляющей шиной. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 622204, кл. И 03 К 17/60, 15.08.78. 2.Авторское свидетельство СССР 547970, кл. Н 03 К 17/60, 29.06.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходное устройство | 1978 |

|

SU771874A1 |

| Буферное устройство | 1977 |

|

SU622204A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Выходное устройство на мдп транзисторах | 1975 |

|

SU547970A1 |

| Источник питания | 1980 |

|

SU900376A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

Авторы

Даты

1981-04-15—Публикация

1979-06-26—Подача