(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство взаимной синхронизации тактовых генераторов сети связи | 1979 |

|

SU773945A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1164899A2 |

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство для измерения задержки четырехполюсников | 1989 |

|

SU1677670A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Устройство тактовой синхронизации | 1984 |

|

SU1234984A2 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

1

Изобретение относится к радиотехнике и может использоваться в системах передачи дискретной информации с временнйм уплотнением.

Известно устройство синхронизации, содержащее п каналов, каждый из которых состоит из последовательно соединенных входного ключа, первого делителя частоты, фазового дискриминатора и усилителя, а также управляющий элемент, объединенный по входу с входным ключом, при этом выходы управляющего элемента подключены к другим входам входного ключа и первого делителя частоты, причем выходы всех каналов подключены к входам сумматора, выход которого через последовательно соединенные фильтр нижних частот, управляемый генератор и второй делитель частоты подключен к другим входам фазовых дискриминаторов и управляющих элементов всех каналов ij .

Однако известное устройство обладает низкой надежностью работы в условиях изменяющейся (нестабильности) частоты поступающего синхросигнала и низкой точностью синхронизации.

Цель изобретения - повышение точности синхронизации.

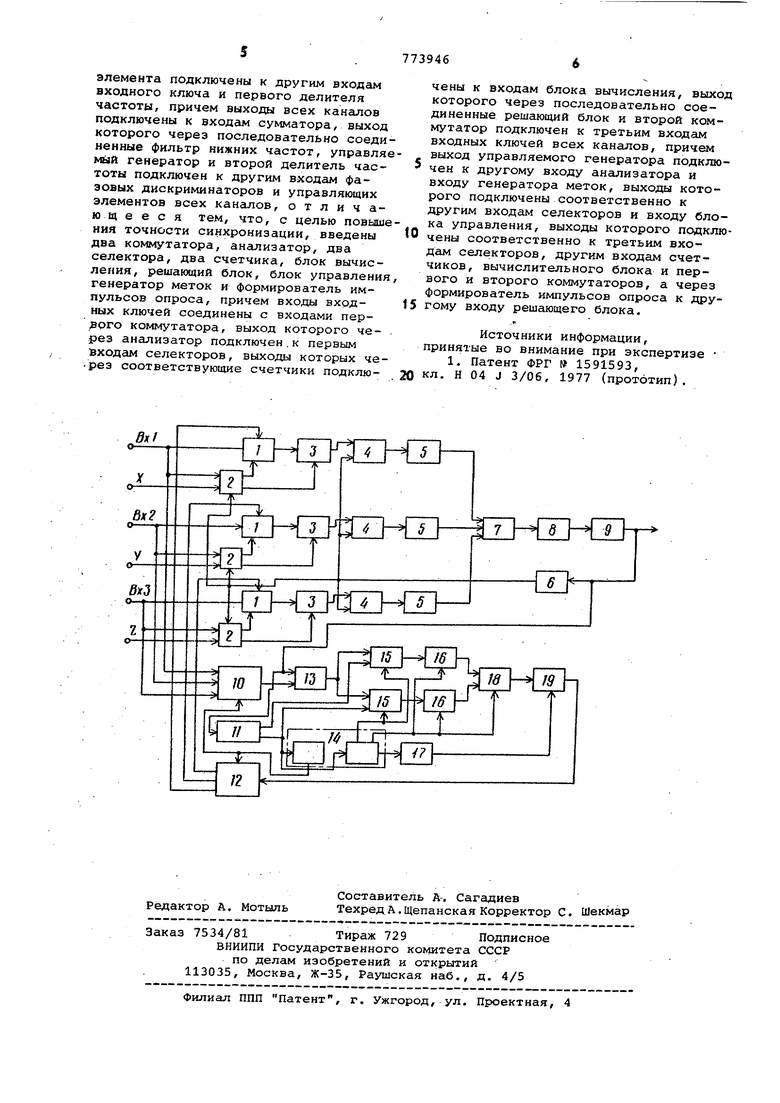

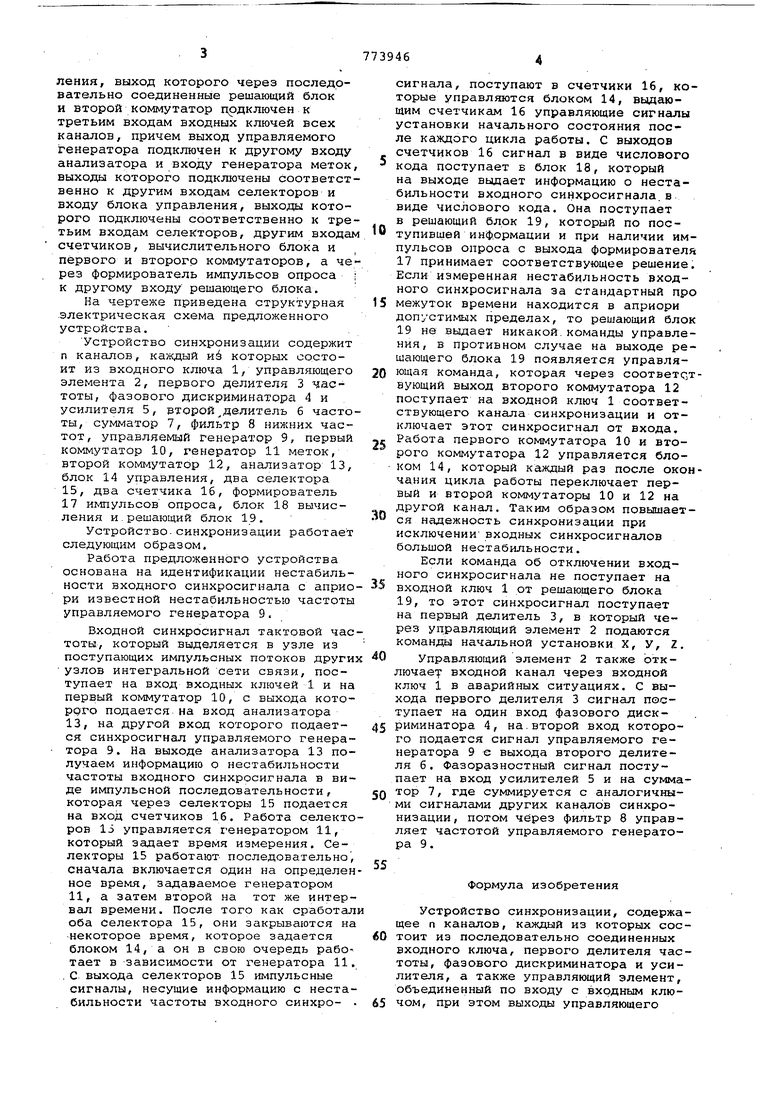

Указанная цель достигается тем, что в устройство синхронизации, содержащее п каналов, каждый из которых состоит из последовательно соединенных входного ключа, первого делителя частоты, фазового дискриминатора и усилителя, а также управляющий элемент, объединенный по входу с входным ключом, при этом выходы управляю0 щего элемента подключены к другим входам входного ключа и первого делителя частоты, причем выходы всех каналов подключены к входам сумматора, выход которого Через последовательно соединенные фильтр нижних частот, управляемый генератор и второй делитель частоты подключен к другим входам фазовых дискриминаторов и управляющих элементов всех каналов,, введены два коммутатора, анализатор, два селектора, два счетчика,-блок вычисления, решающий блок, б,лок управления, генератор меток и форпирователь импульсов опроса, причем ды входных ключей соединены с входами первого коммутатора, выход которого через анализатор подключен к первым входам селекторов, выходы которых через соответствующие счетчики подключены к входам блока вычисления, выход которого через последовательно соединенные решающий блок и второй коммутатор подключен к третьим входам входных ключей всех кансшов, причем выход управляемого генератора подключен к другому входу анализатора и входу генератора меток выходы которого подключены соответственно к другим входам селекторов и входу блока управления, выходы которого подключены соответственно к тре тьим входам селекторов, другим входам счетчиков, вычислительного блока и первого и второго коммутаторов, а че рез формирователь импульсов опроса к другому входу решающего блока. На чертеже приведена структурная .электрическая схема предложенного устройства. Устройство синхронизации содержит п каналов, каждый и6 которых состоит из входного ключа 1, управляющего элемента 2, первого делителя 3 частоты, фазового дискриминатора 4 и усилителя 5, второй делитель 6 часто ты, сумматор 7, фильтр 8 нижних частот, управляемый генератор 9, первый коммутатор 10, генератор 11 меток, второй коммутатор 12, анализатор 13, блок 14 управления, два селектора 15, два счетчика 16, формирователь 17 импульсов опроса, блок 18 вычисления и.решающий блок 19. Устройство-синхронизации работает следующим образом. Работа предложенного устройства основана на идентификации нестабильности входного синхросигнала с априо ри известной нестабильностью частоты управляемого генератора 9. Входной синхросигнал тактовой час тоты, который выделяется в узле из поступающих импульсных потоков други узлов интегральной сети связи, поступает на вход входных ключей 1 и на первый коммутатор 10, с выхода которрго подается на вход анализатора 13, на другой вход которого подается синхросигнал управляемого генератора 9. На выходе анализатора 13 получаем информацию о нестабильности частоты входного синхросигнала в виде импульсной последовательности, которая через селекторы 15 подается на вход счетчиков 16. Работа селекто ров 13 управляется генератором 11, который задает время измерения. Селекторы 15 работают последовательно сначала включается один на определен ное время, задаваемое генератором 11, а затем второй на тот же интер вал времени. После того как сработал оба селектора 15, они закрываются н некоторое время, которое задается блоком 14, а он в свою очередь рабо тает в зависимости от генератора 11 С выхода селекторов 15 импульсные сигналы, несущие информацию с неста бильности частоты входного синхросигнала, поступают в счетчики 16, которые управляются блоком 14, выдаюим счетчикам 16 управляющие сигналы установки начального состояния после каждого цикла работы. С выходов счетчиков 16 сигнал в виде числового кода поступает в блок 18, который на выходе выдает информацию о нестабильности входного синхросигнала.в виде числового кода. Она поступает в решающий блок 19, который по поступившей информации и при наличии импульсов опроса с выхода формирователя 17 принимает соответствующее решение. Если измеренная нестабильность входного синхросигнала за стандартный про межуток времени находится в априори допустимых пределах, то решающий блок 19 не выдает никакой.команды управления, в противном случае на выходе решающего блока 19 появляется управляющая команда, которая через соответс твующий выход второго коммутатора 12 поступает на входной ключ 1 соответствующего канала синхронизации и отключает этот синхросигнал от входа. Работа первого коммутатора 10 и второго коммутатора 12 управляется блоком 14, который каждый раз после окончания цикла работы переключает первый и второй коммутаторы 10 и 12 на другой канал. Таким образом повышается надежность синхронизации при исключении входных синхросигналов большой нестабильности. Бели команда об отключении входного синхросигнала не поступает на входной ключ 1 от решающего блока 19, то этот синхросигнал поступает на первый делитель 3, в который через управляющий элемент 2 подаются команды начальной установки X, У, Z, Управляющий элемент 2 также отключаетр входной канал через входной ключ 1 в аварийных ситуациях, С выхода первого делителя 3 сигнал поступает на один вход фазового дискриминатора 4, на.второй вход которого подается сигнал управляемого генератора 9 е выхода второго делителя 6. Фазоразностный сигнал поступает на вход усилителей 5 и на сумматор 7, где суммируется с аналогичными сигналами других каналов синхронизации, потом через фильтр 8 управляет частотой управляемого генератора 9. Формула изобретения Устройство синхронизации, содержащее п каналов, Кс1ждый из которых состоит из последовательно соединенных входного ключа, первого делителя частоты, фазового дискриминатора и усилителя, а также управляющий элемент, объединенный по входу с входным ключом, при этом выходы управляющего

элемента подключены к другим входам входного ключа и первого делителя частоты, причем выходы всех каналов подключены к входам сумматора, выход которого через последовательно соединенные фильтр нижних частот, управляемый генератор и второй делитель частоты подключен к другим входам фазовых дискриминаторов и управляющих элементов всех каналов, о т л и ч аю щ е е с я тем, что, с целью повышения точности синхронизации, введены два коммутатора, анализатор, два селектора, два счетчика, блок вычисления, решающий блок, блок управления генератор меток и формирователь импульсов опроса, причем входы входных ключей соединены с входами перэого коммутатора, выход которого через анализатор подключен.к первым Входам селекторов, выходы которых через соответствующие счетчики подключены к входам блока вычисления, выход которого через последовательно соединенные решающий блок и второй коммутатор подключен к третьим входам входных ключей всех каналов, причем выход управляемого генератора подключен к другому входу анализатора и входу генератора меток, выходы которого подключены соответственно к другим входам селекторов и входу блока управления, выходы которого подключены соответственно к третьим входам селекторов, другим входам счетчиков, вычислительного блока и первого и второго коммутаторов, а через формирователь импульсов опроса к другому входу решающего блока.

.t

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-10-23—Публикация

1979-02-23—Подача