(54) УСТРОЙСТВО ДЕКОДИРОВАНИЯ Й-ПОСДЕДОВАТЕЛЬНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ диагностики недвоичных блоковых кодов | 2018 |

|

RU2693190C1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| СПОСОБ ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ СООБЩЕНИЙ ХЭШИРУЮЩЕЙ ФУНКЦИЕЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1998 |

|

RU2138126C1 |

| Способ диагностики циклических кодов | 2016 |

|

RU2631142C2 |

| Способ диагностики сверточных кодов | 2015 |

|

RU2616180C1 |

| Устройство для декодирования линейного систематического (п,к) кода | 1984 |

|

SU1327311A1 |

| Способ борьбы с межсимвольными искажениями цифровых сигналов | 2018 |

|

RU2692429C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1042203A1 |

1

Изобретение относится к радиотехнике и может использоваться в системах связи с блочным кодированием информации М-последовательностыо.

Известно устройство декодирования М-последовательности, содержащее генератор поля Галуа, выход которого через первый коммутатор, подключен к входам первого и второго запоминающих блоков, первый регистр и блок выбора максимального сигнала l.

Однако такое устройство имеет невысокую помехоустойчивость.

Цель изобретения - повышение помехоустойчивости .

Для этого в устройство декодирования М-последовательности, содержащее генератор поля Галуа, выход которого черюз первый коммутатор подключен к входам первого и второго запоминающих блоков, первый регистр и Олок выбора максимального сигнала, введены элемент ИЛИ, второй регистр и последовательно соединенные арифме тический блок, третий регистр и второй коммутатор, выходы которого подключены соответственно к входу блока выбора максимального сигнала, соединенного с входом второго регистра и вторым входом первого и второго запоминающих блоков, выходы которых через последовательно соединенные элемент ИЛИ и первый регистр подключены к входам арифметического блока, другой выход которого подключен к второму входу второго коммутатора, третий вход которого соединен с вторым входом первого коммутатора и выходом блока управления, второй выход которого подключен к третьим входам первого и второго запоминающих блоков, третий выход подключен к другим входам первого, второго и третьего регистров, а четвертый выход подключен

15 к третьему входу первого коммутатора.

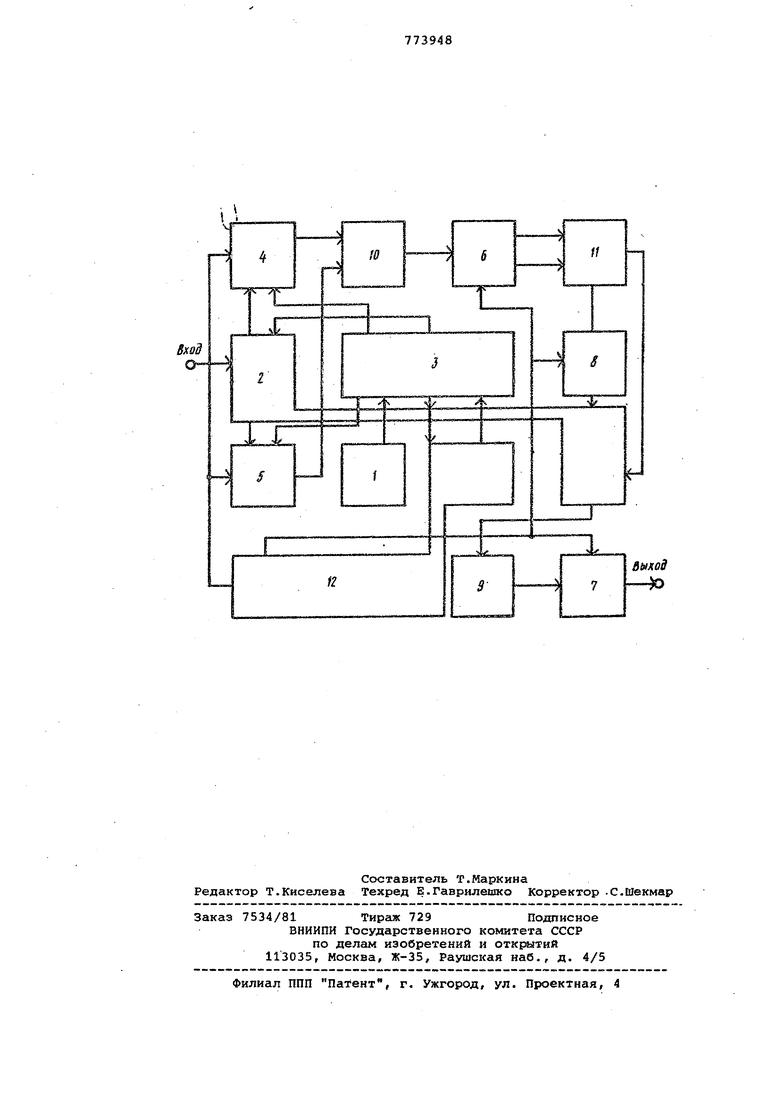

На чертеже дана структурная электрическая схема предложенного устройства.

20 Устройство содержит генератор 1 поля Галуа, коммутаторы 2 и 3, запоминающие блоки 4 и 5, регистры 6-8, блок 9 выбора максимального сигнала, элемент 10 ИЛЯ, арифметический блок

25 11 и блок 12 управления.

Устройство работает следующим образом.

Символы М-посгедовательности в виде двоичных чисел, величина которых

30 пропорциональна знаку и величине принимаег«юго сигнала, поступаю : через кокимутатор 2 на информационные входы, первого запоминающег-о блока 4. в это время к адресныги; входам этого блока с помощь комглутатора 3 подключаются выходы генератора i. В результате этого значения входного сигнала записива5отся в ячейки памяти запоминающего блока 4 по адтресам, oпpeдeляe дым з каждый момент времени номером символа М-последовательности и состоянием аы ходгов генератора-1. Поле генерируется Е соответствии со степенью элемента поля.

Для декодирования необходимо умножить записанную в запоминающий блок реализацию на матрицу Адамара, т.е. вьшислкть коэффициенты корреляции с функциями Уолма. Это может быть сделано с помощью aлгopит sa быстрых преобразований.

Л.пя этого устройство переключается в режШ.-1 эьгаислеиия, когда к адресным входггм запоминающего блока 4 через коммутатор 3 1 одключа,ются выходы блока 12. Запоминающий блок 5 пеpeKJiio-iacTCii на запись символов следующей последовательности и ic его адресным входам через ког-шутатор 3 подключаготся. выходы генератора 1. Происхо.цит суммирование и вычитание Hcip синзолов, стоямих рядом (о и 1, 2 и 3, 4 н 5 и т.д.). Полученные суммь и разности записываются н ячейки памяти запоминающего блока 4, прич€;м, сумма записывегется в ячейку, нз которой бЕЛЛО считано первое слагаемое, а разность записывается в ячейку нэ которой было считано второе слагаеное. При этОлМ,поскольку нулевой симвоп равен О (отсутствует), в ячей ку идля суммы запишется само число а в ячейку для разности - число, умножеиное ка -1. Считанные числа через элемент 10 ИЛИ попадают на вход регистра 6 и запоминаются в нем на время вычисления. В арифметическом блоке 11 происходит вг:гчисление суммы и разности чисел, поступающих с выходов регистра 6. Cy S-1a, через коммутатор 2, непосредственно попадает на информационные входы запоминаю.щего блока 4, а разность записквается в регистр 8.

После произведенных вычислений полученные коэффициенты .начинают анализироваться блоком D. В этом блоке 9 определяется максимальный коэффициент корреляции и номер, под которы 4 оя находится в последовательноЬти всех козффизлиентов. Этот номер в двоичной форме пр дстазляет собой .декодированные симво.пы, при этом первому коэффициенту присваивается номер О,

Декодированные символы, поступающие с выхода блока 9, записываются в регистр 7, с которого выводятся на выход устройства.

На этом заканчивается декодироваНИ8 одной М последовательиости, к этому времени оказывается заполненным запоминающий блок 5 и, после соответствующей коммутации, начинается декодирование вновь записанной

М последовательности.

Назначение блока 12 - формировать соответствующие сигналы для управления режимами записи - чтения запоминающих блоков 4 и 5, управления работой коммутаторов 2 и 3 и синхронизации работы регистров 6-8.

Гредложенное устройство работает не с бинарноквантованными символами, ас числами, осуществляя прием в целом, помехоустойчивость которого выше поэлементного, реализуемого в известном устройстве.

Формула изобретения

Устройство декодирования М-после довательности, содержащее генератор поля Галуа, выход которого через первый коммутатор подключен к входам первого и второго запоминающих блоков, первый регистр и блок выбора максимального сигнала, отличающееся тем, что, с целью повышения помехоустойчивости, введены элемент ИЛИ, второй регистр и последовательно соединенные арифметический блок, третий регистр и второй коммутатор, выходы которого подключены соответственно к входу блока выбора максимального сигнала .соединенного с входом второго регистра и вторым

входом первого и второго запоминающих блоков, выходы которых через последовательно соединенные элемент ИЛИ и первый регистр подключены к входам арифметического блока,

другой выход которого подключен к второму входу второго комг-1утатора, третий вход которого соединен с вторым входом первого ког.мутатора и выходом блока управления, второй

выход которого подключен к третьим входам первого и второго запоминающих блоков, третий выход подключен к другим входам первого, второго и третьего регистров, а четвертый выход подключен к третьему входу

первого KorvsMyTaTopa.

Источники информации, принятые во ЕН1-иу1ание при экспертизе

Авторы

Даты

1980-10-23—Публикация

1977-04-21—Подача