ь.

(54) ПгаОБРАЗОВАТЕЛЬ КОДОВ |

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь позиционного кода в код с большим основанием | 1987 |

|

SU1444959A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750484A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Преобразователь кода в код с большим основанием | 1976 |

|

SU581469A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Преобразователь кода в код с большим основанием | 1985 |

|

SU1332537A1 |

| Вычислительное устройство | 1983 |

|

SU1164701A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1134948A1 |

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

1

Изобретение относится к области автоматики и вычисяительноч техники и может быть использовано лри построении преобразующих устройств.

Известно устройство для преобразования двоичного кода в двоично-десятичный 1, содержащее треугольную матрицу логических ячеек, связанных друг с другом, входы первой строки матрицы соединены с шинами входного кода, а выходы последнего столбца соединены с шинами выходного кода.

Недостатком такого устройства является невозможность преобразования ко;од из любого целого основания в код с любым щ уп11й целым основанием.

Наиболее близким техническим решением к данному изобретению является преобразователь кодов 21, содержащий вычитатель, первую группу элементов И, ячейку преобразования, состоящую из блока умножения на константу и блока суммирования, первый вход Kotoporo соединен с первым входом ячейки преобразования и входом блока умножения на коистанту, первый и второй выходы которого соединены со вторым и третьим входами блока суммй

роваНия соответственно, четвертый вход блока. суммирования соедииен со вторым входом ячейки преобразо1ваНйя, выходы блока суммирования являются вькрдамН ячейки преобразования. Кроме того, это устройство содержит два сдвиговых регистра, информационный регистр и блок управления.

Недостатком этого устройства является относительно низкое быстродействие и сложность управлсиия.

10

Целью изобретения является повышение быстродействия.

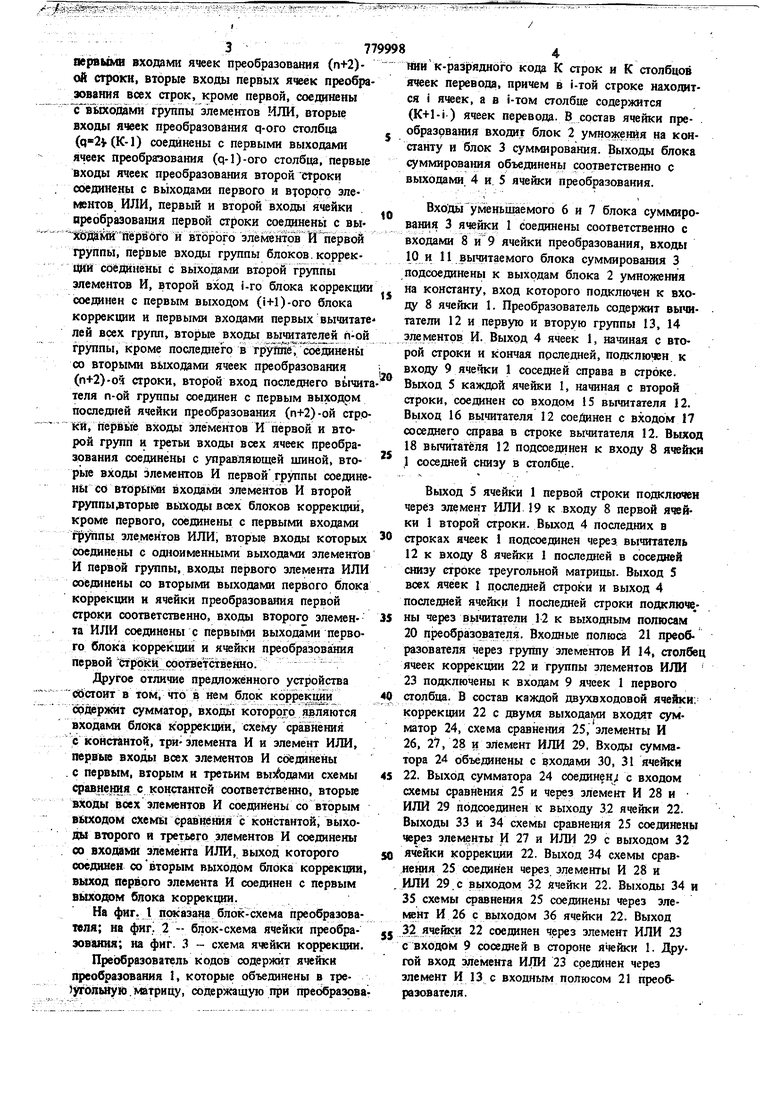

Это достигается тем, что преобразователь содержит дополнительные ячейки преобразования, объединенные в треугольную матрицу,

15 i-ый ((K-l) столбец которой состоит из (K-i) ячеек преобразования, j-ая строка ( i (К-1) состоит из j ячеек преобразования, где К число разряде преобразуемого кода, К бло ков коррекции, вторую группу злементот И,

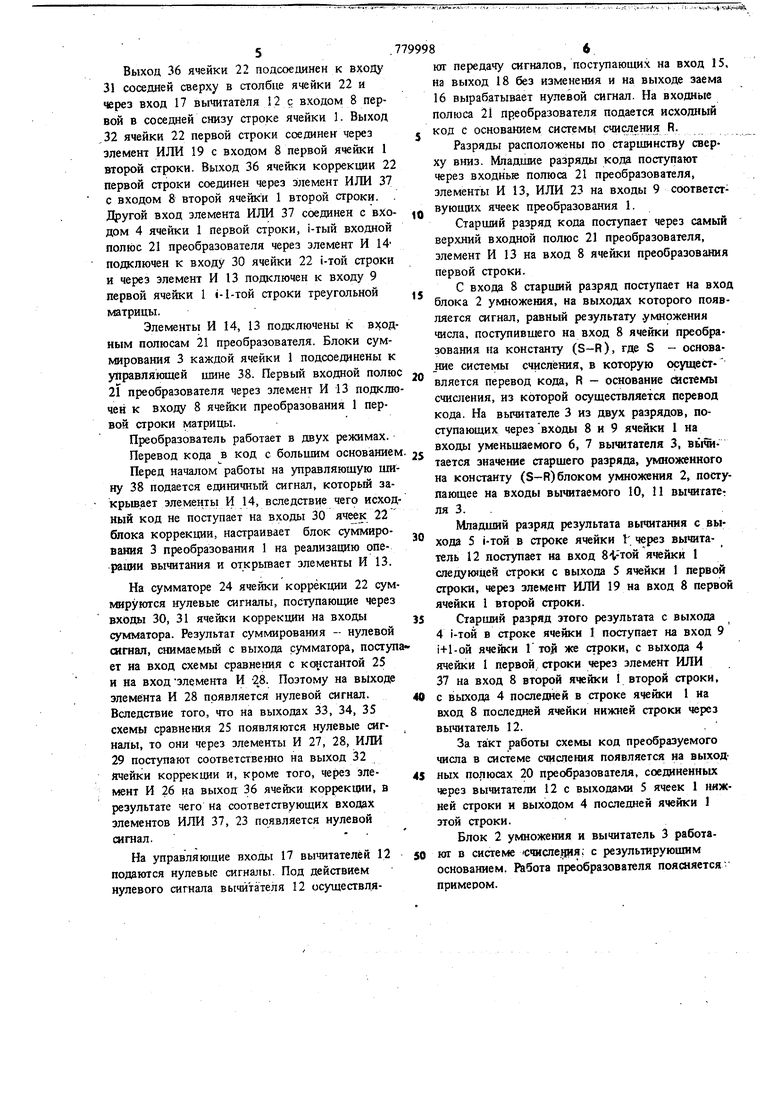

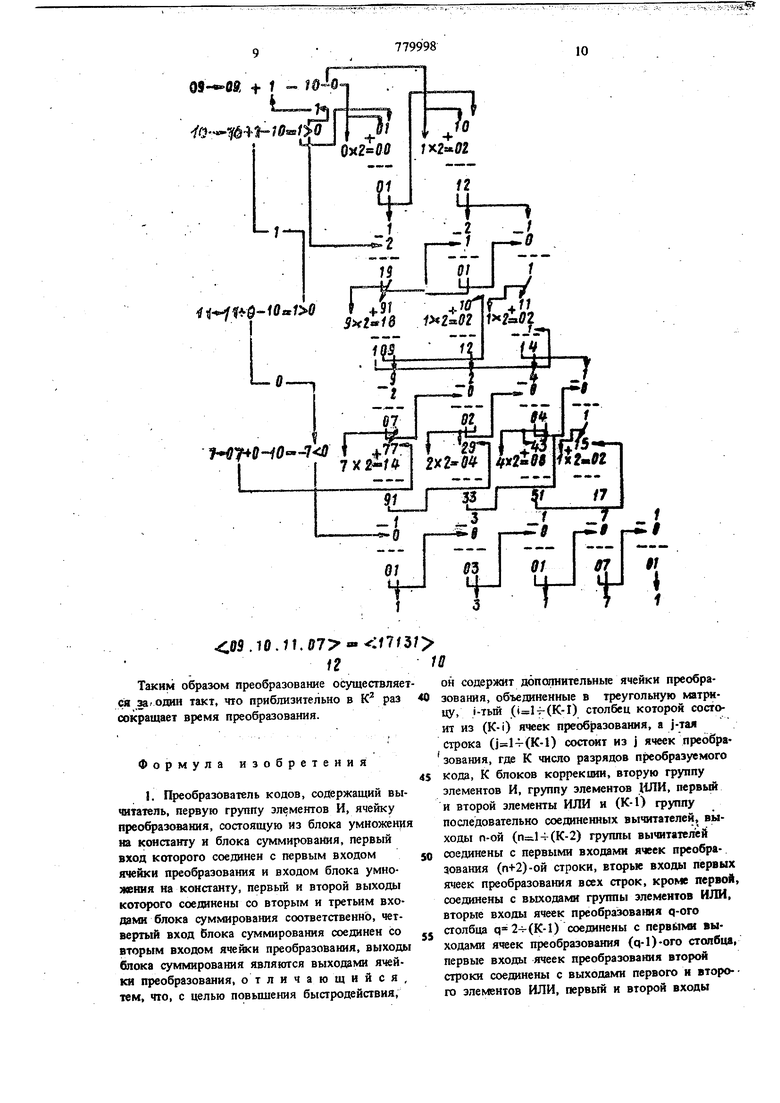

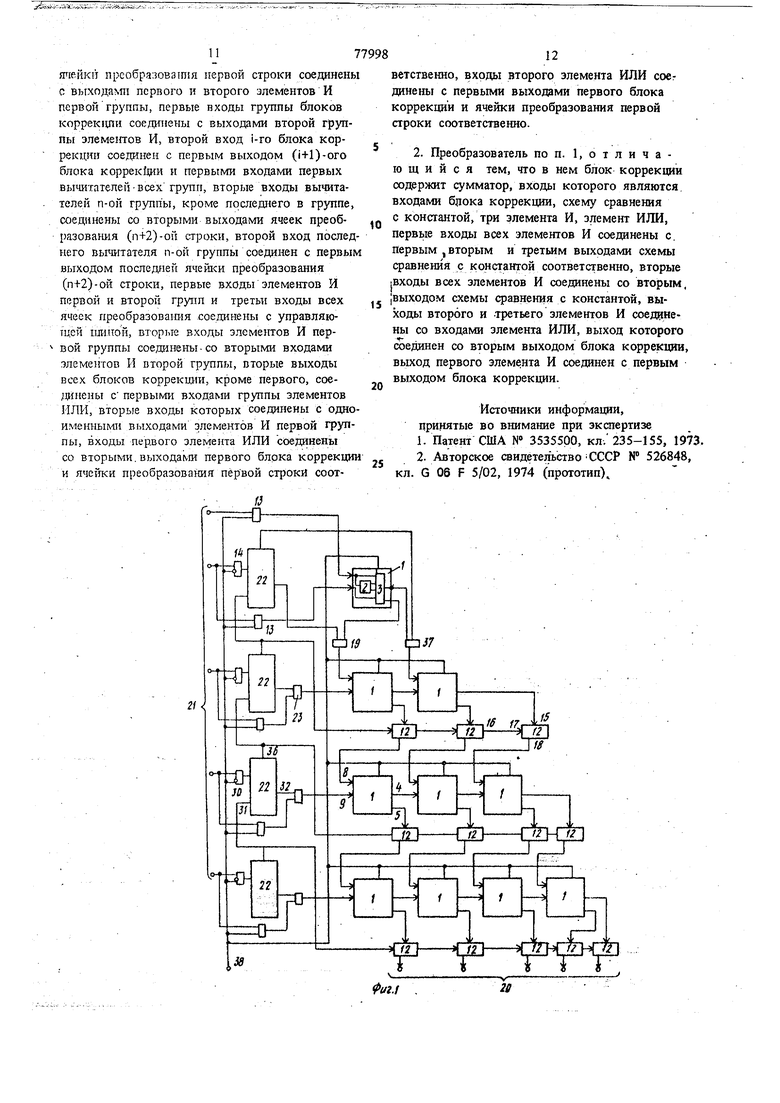

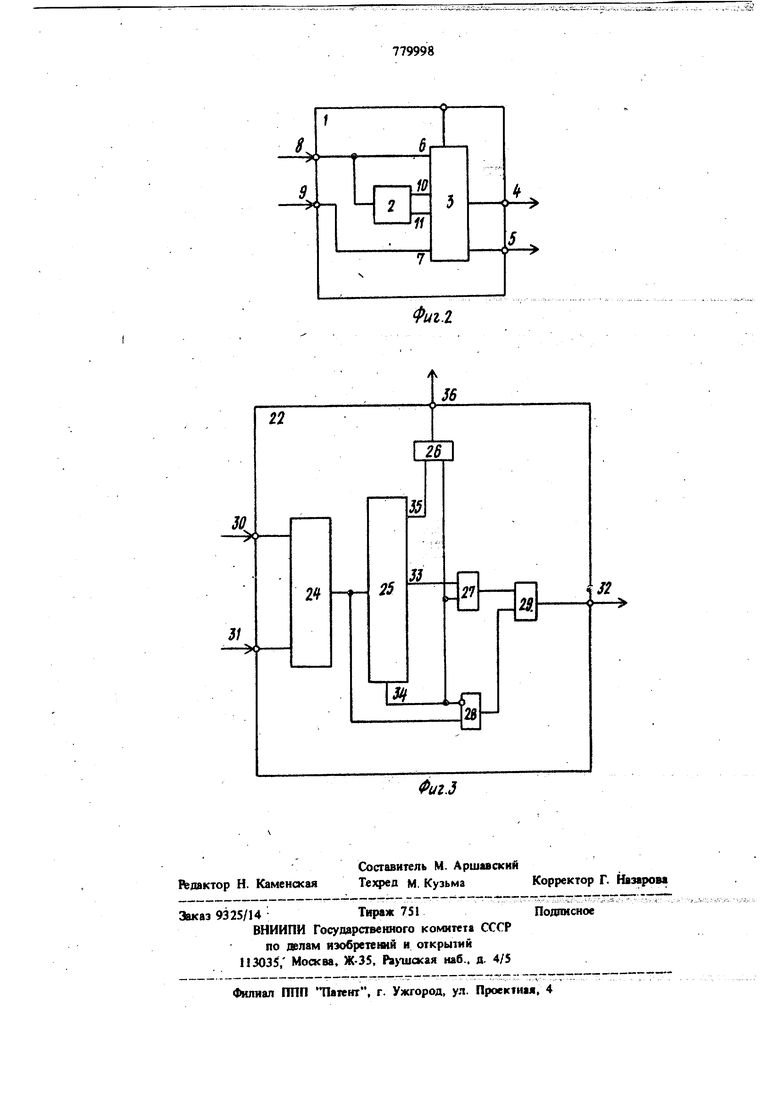

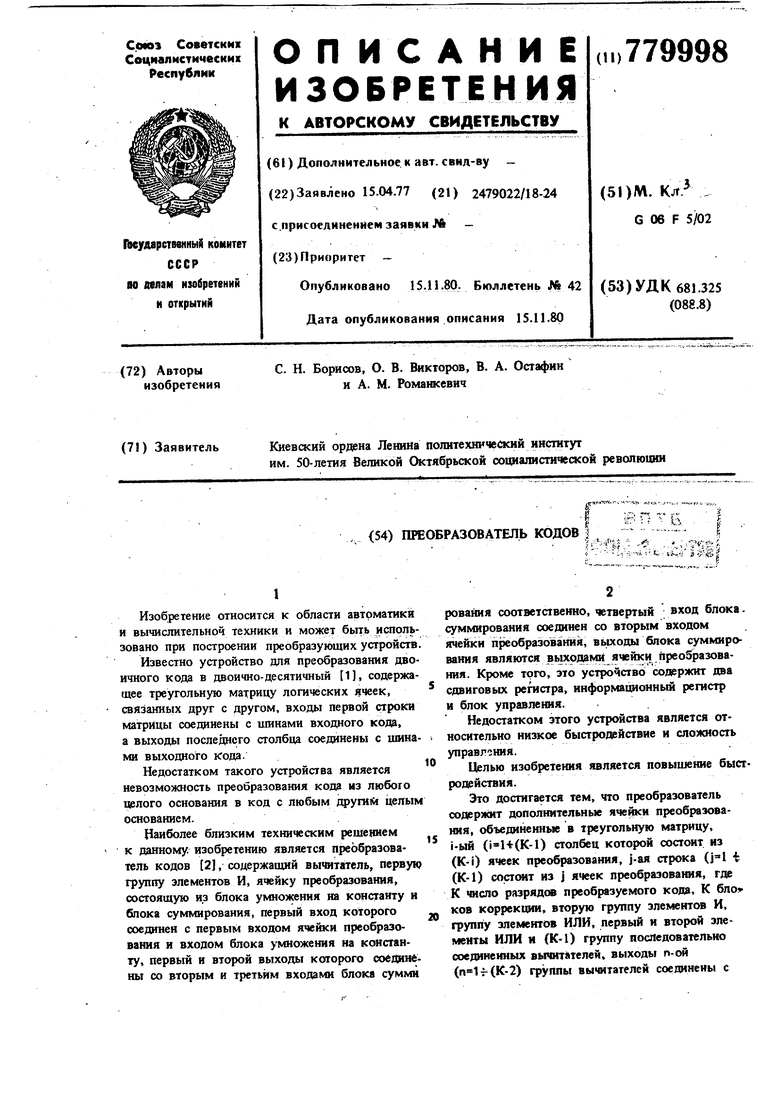

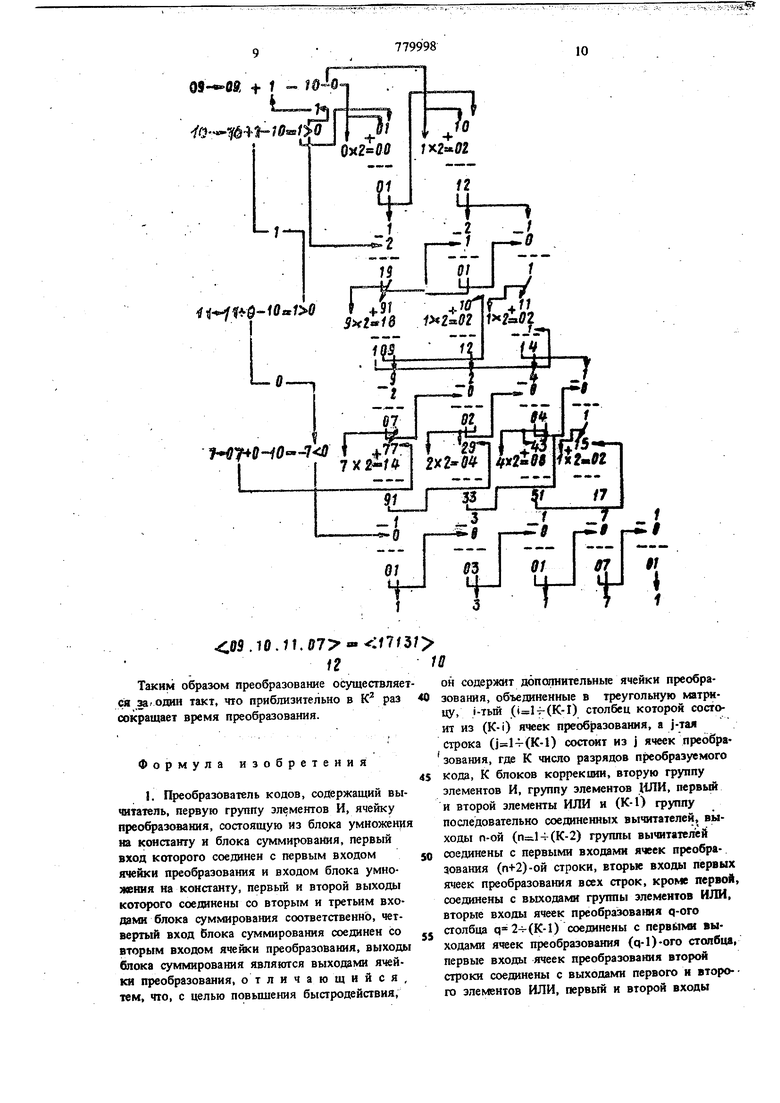

20 группу элементов ИЛИ, первый и второй элементы ИЛИ и (К-1) группу последовательно соединенных вычитателей, выходы п-ой ((K-2) группы вычитателей соединены с 37 аервыми входами ячеек преобразования (п+2)ой строки, вторые входы первых ячеек преобра зования всех строк, кроме первой, соединены с вьк6дами группы элементов ИЛИ, вторые входы ячеек преобразования q-oro столбца (Q«2i(K-l) соединены с первыми выходами ячеек преобразования (q-l)-oro столбца, первые входы ячеек преобразования второй строки соединены с выходами первого и второго элементов ИЛИ, первый и второй входы ячейки преобразовашя первой строки соединены с вы :Шда1йШр1Й6г0 и второго элёментот ЙПпервой группы, первые входы группы блоков, коррек1ЩИ Соединены с выходами второй группы элементов И, второй вход i-ro блока коррекции соединен с первым выходом (i+l)-oro блока коррекции и первыми входами первых вычитате лей всех групп, вторые входы вычитателей п-ой группы, кроме последнего в груШёТ Единены со вторыми вь1ходами ячеек преобразования (п+2)-ой строки, второй вход последнего вычит теля п-ой группы соединен с первым выходом послещгей ячейки преобразования (п+2)-ой стро ки, nepisbie входы элементов И первой и второй групп и третьи входы всех ячеек преобразования соединены с управляющей шиной, вторые входы элементов И первой группы соедине ны сО вторыми входами элементов И второй группызторые выходь всех блоков коррекции, кроме первого, соединены с первыми входами г руппы элементов ИЛИ, вторые входы которых соединены с одноименными выходами элементов И первой группы, входы первого элемента ИЛИ соединены со вторыми выходами первого блока коррекции и ячейки преобразования первой строки соответственно, входы второго элемента ИЛИ соединены с первыми выходами первого блока коррекции и ячейки преобразования первой ётрШн отаётствевдо.Другое отличие предложенного устройства СОСТОИТ в Том, что в нем блок кор рекции ордержит сумматор, входь которого являются входами блока коррекции, схему срШнёния с константой, три-элемента И и элемент ИЛИ, первью входы всех элементов И соёдИнеИы . с первым, вторым и третьим вы одами схемы сравнещя с константой соответственно, вторые входы всех элементов И соедиИены со вторым выходом схемы сравнения с константой, выходы второго и третьего элементов И соединены со входами элемента ИЛИ, выход которого соединен со вторым выходом блока коррекции выход первого элемента И соединен с первым выходом блока коррекции. На фиг. I показана блок-схема преобразователя; на фиг 2- блок-схема ячейки преобразования; иа фиг. Я - схема ячейки коррекции. Пре(эбразователь кодов содержит ячейки преобразования 1, которые объединены в треJyrohuiyiu.матрицу, содеряащую при преобразрв 4. .. НнИк-разрядного кода К строк и К столбцов ячеек перевода, причем в i-той строке иаходится i ячеек, а в i-том столбце содержится (K-H-i ) ячеек перевода. В состав ячейки пре- . образрвания входит блок 2 умножения на константу и блок 3 суммирования. Выходы блока суммирования объединены соответственно с выходами 4 и 5 ячейки преобразования. Входы уменьшаемого 6 и 7 блока суммирования 3 ячейки 1 соединены соответственно с входами 8 и 9 ячейки преобразования, входы 10 и 11 вычитаемого блока суммирования 3 подсоединены к выходам блока 2 умножения на константу, вход которого подключен к входу 8 ячейки I. Преобразователь содержит вычитатели 12 и первую и вторую группы 13, 14 элемЕНТов И. Выход 4 ячеек I, начиная с второй строки и кончая последней, подключен к входу 9 ячейки 1 соседней справа в строке. Выход 5 каждой ячейки 1, начнная с второй строки, соединен со входом 15 вьрштателя 12. Выход 16 вь1читателя 12 соединен с вх:одом 17 соседнего справа в строке вычитателя 12. Выход 18 вычитателя 12 подсоединен к входу 8 ячейки 1 соседней снизу в столбце. ... . . . Выход 5 ячейки 1 первой строки подключен через элемент ИЛИ 19 к входу 8 первой ячейки 1 второй строки. Выход 4 последних в строках ячеек 1 подсоединен через вычитатель 12 к входу 8 ячейки 1 последней в соседней снизу строке треугольной матрицы. Выход 5 всех ячеек 1 последней строки и выход 4 последней ячейки 1 последней строки подключе,ны через вычитзтели 12 к выходным полюсам 20 П{зеобразова1теля. Входные полюса 21 преобразователя через группу элементов И 14, столбец ячеек коррекции 22 и группы злемеитов И.ЛИ 23 подключены к входам 9 ячеек 1 первого столбца. В состав каждой двухвходовой ячейки; коррекции 22 с двумя выходами входят сумматор 24, схема сравнения 25, элементы И 26, 27, 28 и элемент ИЛИ 29, Входы сумматора 24 объединены с входами 30, 31 ячейки 22. Выход сумматора 24 соединен; с входом схемы сравнения 25 и через элемент И 28 и ИЛИ 29 подсоединен к выходу 32 ячейки 22. Выходы 33 и 34 схемы сравнения 25 соединены через элементы И 27 и ИЛИ 29 с выходом 32 ячейки коррекции 22. Выход 34 схемы сравнения 25 соедиИен через элементы И 28 и ИЛИ 29 с выходом 32 ячейки 22. Выходы 34 и 35 схемы сравиения 25 соединены через элемент И 26 с выходом 36 ячейки 22. Выход 32 ячейки 22 соединен через элемент ИЛИ 23 С входом 9 соседней в стороне ячейки 1. Другой вход элемента ИЛИ 23 соединен через элемент И 13 с входньп« полюсом 21 преобразователя. Выход 36 ячейки 22 подсоединен к входу 31 соседней сверху в столбце ячейки 22 и через вход 17 вычитатёля 12 с входом 8 первой в соседней снизу строке ячейки 1. Выход ,32 ячейки 22 первой строки соединен через элемент ИЛИ 19с входом 8 первой ячейки 1 второй строки. Выход 36 ячейки коррекции 22 первой строки соединен через злемент ИЛИ 37 с входом 8 второй ячейки 1 второй строки. Другой вход элемента ИЛИ 37 соединен с вХо дом 4 ячейки 1 первой строки, i-тый входной полюс 21 преобразователя через элемент И 14 подключен к входу 30 ячейки 22 i-той строки и через элемент И 13 подключен к входу 9 первой ячейки 1 i-1-той строки треугольной матрицы. Элементы И 14, 13 подключены к вход ным полюсам 21 преобразователя. Блоки суммирования 3 каждой ячейки 1 подсоед 1нены к управляющей шине 38. Первый входной полю 21 преобразователя через элемент И 13 подклю чен к входу 8 ячейки преобразования 1 первой строки матрицы. Преобразователь работает в двух режимах. Перевод кода в код с большим основанием Перед началом работы на управляющую ши ну 38 подается единичный сигнал, который закрьшает элементы И 14, вследствие чего исход ный код не поступает на входы 30 ячеек 22 блока коррекции, настраивает блок суммирования 3 преобразования 1 на реализацию операции вычитания и открьгаает элементы И 13. На сумматоре 24 ячейки коррекции 22 суммируются нулевые сигналы, поступающие через входы 30, 31 ячейки коррекции на входы сумматора. Результат суммирования - нулевой сигнал, снимаемый с выхода сумматора, поступ ет на вход схемы сравнения с константой 25 и на вход-элемента И 2,8. Поэтому на выходе элемента И 28 появляется нулевой сигнал. Вследствие того, что на выходах 33, 34, 35 схемы сравнения 25 появляются нулевые сигналы, то они через элементы И 27, 28, ИЛИ 29 поступают соответственно на выход 32 ячейки коррекции и, кроме того, через злемент И 26 на выход 36 ячейки коррекции, в результате чего на соответствующих входах элементов ИЛИ 37, 23 появляется нулевой сигнал. На управляющие входы 17 вычитателёй 12 подаются нулевые сигналы. Под действием нулевого сигнала вычитатёля 12 осуществдяют передачу сигналов, поступающих на вход 15, на выход 18 без изменения и на выходе заема 16 вырабатывает нулевой сигнал. На входные полюса 21 преобразователя подается исходный код с основанием системьг счисления R. Разряды расположены по старшинству сверху вниз. Младшие разряды кода поступают через входные полюса 21 преобразователя, элементы И 13, ИЛИ 23 на входы 9 соответствующих ячеек преобразования 1. Старший разряд кода поступает через самый верхний входной полюс 21 преобразователя, элемент И 13 на вход 8 ячейки преобразования первой строки. С входа 8 старший разряд поступает на вход блока 2 умножения, на выходах которого появляется сигнал, равный результату .умножения числа, поступившего на вход 8 ячейки преобразования на константу (S-R), где S - основание системы счисления, в которую осуществляется перевод кода, R - основание системы счисления, из которой осуществляется перевод кода. На вычитателе 3 из двух разрядов, поступающих черезвходы 8 и 9 ячейки 1 на входы уменьшаемого 6, 7 вычитатёля 3, вь1Чнтается значение старшего разряда, умноженного на константу (S-R) блоком умножения 2, поступающее на входы вычитаемого 10, 11 вычитате ля 3. . Младший разряд результата вычитания с выхода 5 i-той в строке яадйки I, через вычитатель 12 поступает на вход 8 i-той ячейки 1 следую1цей строки с выхода 5 ячейки 1 первой строки, через злемет ИЛИ 19 на вход 8 первой ячейки 1 второй строки. Старший разряд этого результата с выхода 4 i-той в строке ячейки 1 поступает на вход 9 i+1-ой ячейки Г той же строки, с выхода 4 ячейки 1 первой строки через элемент ИЛИ 37 на вход 8 второй ячейки 1 второй строки, с выхода 4 последней в строке ячейки 1 на вход 8 последней ячейки нижней строки через вычитатель 12. За такт работы схемы код преобразуемого числа в системе счисления появляется на выхоД ных по;1юсах 20 преобразователя, соединенных через вычитатели 12 с выходами 5 ячеек 1 нижней строки и выходом 4 последней ячейки 1 этой строки. Блок 2 умножения и вычитатель 3 работают в системе 1Счисле1В1я; с результирующим основанием. Работа преобразователя поясняется примером.

0-п

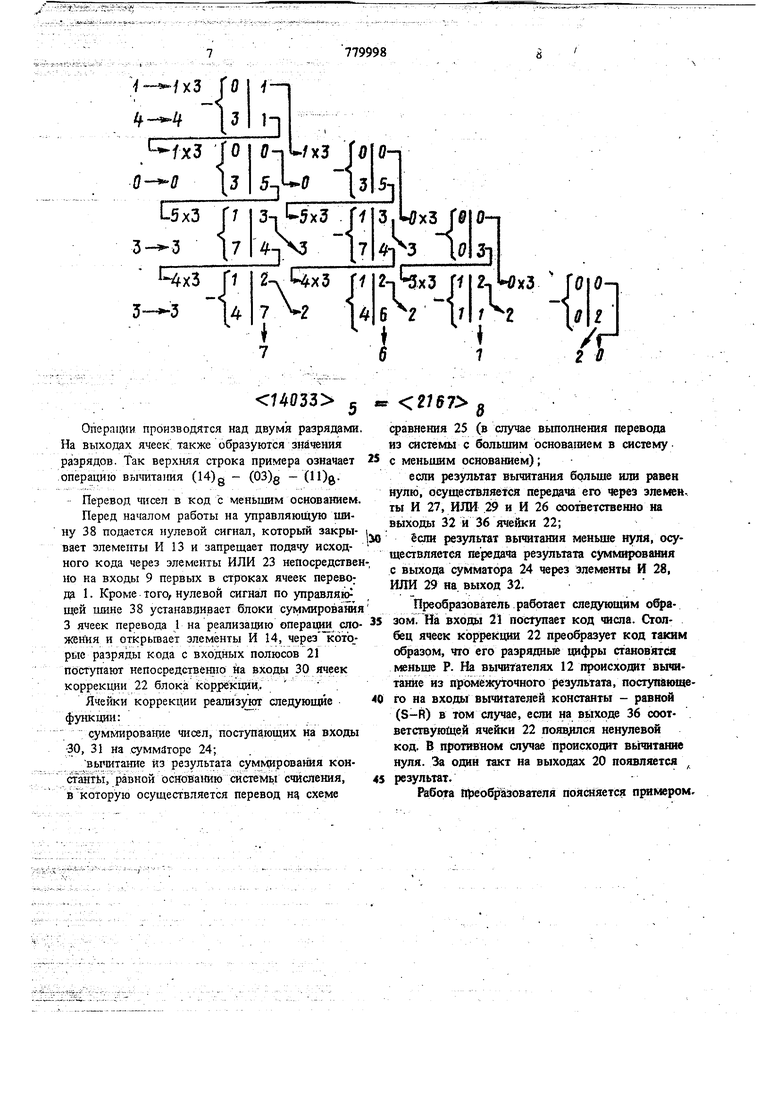

/г

V fc МОЗЗ 5 Операции производятся над двумя разряддми На выходах ячеек также образуются значения разрядов. Так верхняя строка примера означает операцию вытатамия (14)g - (03)g - (ll)g. Перевод чисел в код с меньшим основанием. Перед началом работы на управляющую ишну 38 подается нулевой сигнал, который закрывает элементы И 13 и запрещает подачу исходного кода через элементы ИЛИ 23 непосредствен но на входы 9 первых в строках ячеек перево; да I. Кроме того, нулевой сигнал по управлякь щей шине 38 устанавдивает блоки суммирования 3 ячеек перевода 1 на реализацию операдаи сложения и открьшает элементы И 14, через к6тЬ PLIC разряды кода с входных полюсов 21 Поступают непосредствен1ю йа входы 30 ячеек коррекции 22 блока коррекций.. . Ячейки коррекции реализуют следующие функции: суммироваггие 4iiсел, поступающих на входы -30, 31 На сумматоре 24; . вычитание из результата сум щрования константы, равной основанию системы счисления, некоторую осуществляется перевод щ схеме 2757 сравнения 25 (в случае выполнения перевода из системы с большим основашем в систему с меньшим основадаем); если результат вычитания больше или равен нулю, осуществляется передача его через эпемен. ты И 27, ИЛИ 29 и И 26 соответственно на выходы 32 я 36 ячейки 22; если результат вычитания меньше нуля, осуществляется передача результата суммирования с выхода сумматора 24 через элементы И 28, ИЛИ 29 на. выход 32. Преобразователь работает следующим образом. На входы 21 поступает код числа. Столбец ячеек коррекции 22 преобразует код таким образом, что его разрядные цифры становятся меньше Р. На вычитателях 12 происходит вычитание из прсйлежуточного результата, поступаницего на входы вычитателей константы - равной (S-R) в том случае, если на вь1ходе 36 соответствую1цей ячейки 22 ненулевой код. В противном случае происходит вычитание нуля. За один такт на выходах 20 появляется , результат. Работа Гфеобр1аэователя поясняется примером. W.10.H. 12 Таким образом преобразование осуществляе сй Ж1 сдан такт, что приблизительно в К раз сокращает время преобразования. Формула изобретения . Преобразователь кодов, содержащий вычитатель, первую группу элементов И, ячейку преобразования, состоящую из блока умножени на константу и блока суммирования, первый вход которого соединен с первым входом ячейки преобразования и входом блока умножения на константу, первый и второй выходы которого соединены со вторым и третьим входами блока сумлшрования соответственно, четвертый вход блока суммирования соединен со вторым входом ячейки преобразования, выходы блока суммирования являются выходами ячейки преобразования, отличающийся, тем, что, с целью повьщтення быстродействия. S ой содержит дополнительные ячейки преобразования, объединенные в треугольную матрицу, i-тьй ((K-I) столбец которой состоит из (K-i) яадек преобразования, а j-тая Строка ((K-l) состоит из j ячеек преобразования, где К число разрядов преобразуемого кода, К блоков коррекции, вторую группу элементов И, группу элементов ЦЛИ, первый и второй элементы ИЛИ и (К-1) группу последовательно соединенных вычитателей, выходы п-ой (n il-;-(K-2) группы вычитателей соедаиены с первыми входами ячеек преобразования ()-ой строки, вторые входы первых ячеек преобразования всех строк, кроме первой, соединены с выходами группы элементов ИЛИ, вторые входы ячеек преобразования q-oro столбца (K-l) соединены с первыми выходами ячеек преобразования (q-l)-oro столбца, первые входы ячеек преобразования второй строки соединены с выходами первого и второ- го элемеитов ИЛИ, первый и второй входы шгейкй преобра:ювзш1я первой строки соединены о BbixoMaNni первого и второго элементов И первой группы, первые входы группы блоков коррек1ши соедапены с выходами второй группы элеметов И, второй вход i-ro блока коррекции соединен с первым выходом (i+l)-oro блока KoppeKljjiH и первыми входами первых вы штателей - всехгрупп, вторые входы вычитателей п-ой грулпы, кроме последнего в группе, соединены со вторыми выходами ячеек преобразования (п+2)-ой строки, второй вход послед него выадтателя п-ой группы соединен с первы выходом последней ячейки преобразования (п-1-2)-ой строки, первые входы элементов И первой и второй групп и треты входы всех ячеек преобразования соединены с управляютцей Чиипой, вторые входы элеме1ггов И первой группы соединены-со вторыми входами элементов И второй группы, вторые выходы всех блоков коррекции, кроме первого, соединены с первыми входами группы злементов ИЛИ, BTopbte входы которых соединены с одно именными выходами элементов И первой группы, входы первого элемента ИЛИ соеданены со вторыми, выxoдa ш первого блока коррекци и ячейки преобразовашя первой строки соот12ветственно, входы второго элемента ИЛИ совг данены с первыми выходами первого блока коррекции и ячейки преобразования первой строки соответственно. 2. Преобразователь по п. 1, о т л и ч а ю щ и и с я тем, что в нем блок коррекции содержит сумматор, входы которого являются, входами бдока коррекции, схему сравнения с константой, три элемента И, элемент ИЛИ, первые входы всех элементов И соединены с. первым , вторым и третьим выходами схемы сравнения с константой соответственно, вторые 1ВХОДЫ всех злементов И соединены со вторым, |выходом схемы сравнения с константой, выходы второго и третьего элементов И соединены со входами элемента ИЛИ, выход которого соединен со вторым выходом блока коррекции, выход первого элемента И соединен с первым выходом блока коррекции. Источники информации, принятые во внимание при экспертизе 1. Патент США N 3535500, кл.235-155, 1973. 2- Авторское свидетельство СССР № 526848, кл. G 06 F 5/02, 1974 (прототип).

2

J2

2S.

Авторы

Даты

1980-11-15—Публикация

1977-04-15—Подача