4 4 4 СО СП СО

Изобретение относится к вычисли- тельной технике и автоматике и может быть использовано в устройствах обработки информации, функционирующих S различных системах счисления, для перевода позиционного кода из системы счисления с любым основанием в коды чисел с любым большим основанием. Цель изобретения - повышение скорости преобразования.

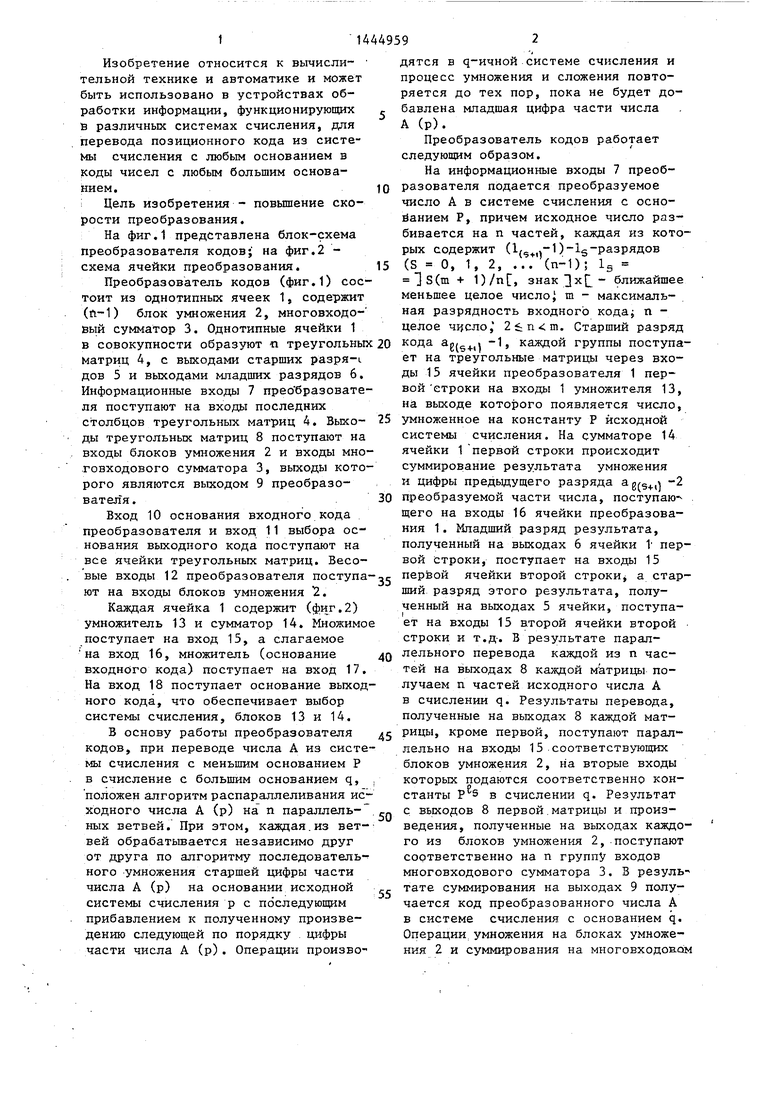

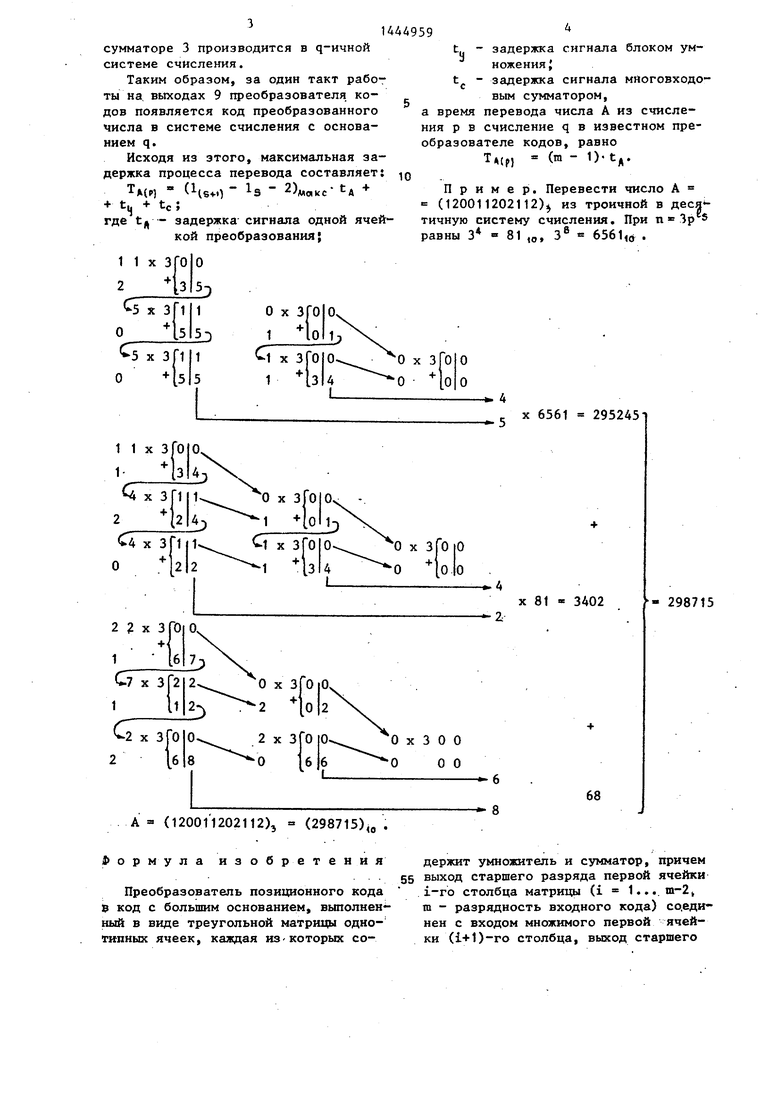

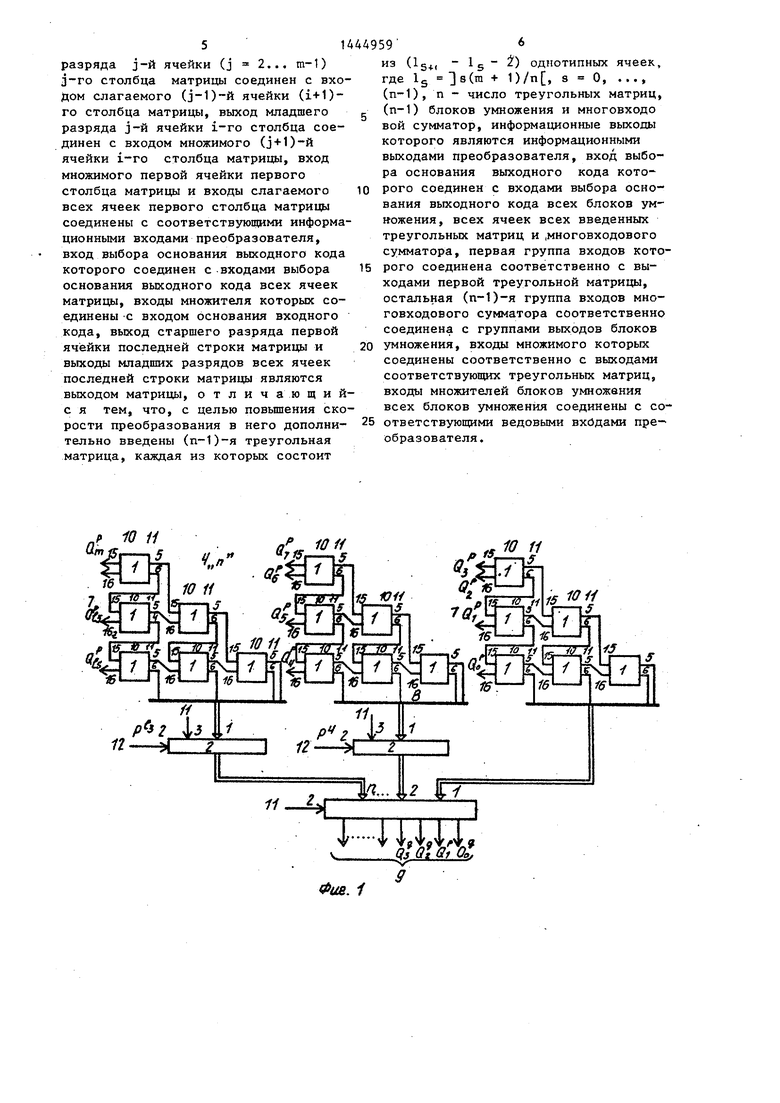

На фиг.1 представлена блок-схема преобразователя кодов; на фиг.2 - схема ячейки преобразования.

Преобразователь кодов (фиг.1) состоит из однотипных ячеек 1, содержит (п-1) блок умножения 2, многовходо- вый сумматор 3. Однотипные ячейки 1 в совокупности образуют п треугольных матриц 4, с выходами старших разря-i дов 5 и вьЕКОдами младших разрядов 6. Информационные входы 7 прео бразовате- ля поступают на входы последних столбцов треугольных матриц 4. Выхо- ды треугольных матриц 8 поступают на входы блоков умножения 2 и входы мно- говходового сумматора 3, выходы которого являются выходом 9 преобразователя.

Вход 10 основания входного кода преобразователя и вход 11 выбора основания выходного кода поступают на все ячейки треугольных матриц. Весовые входы 12 преобразователя поступа ют на входы блоков умножения 2.

Каждая ячейка 1 содержит (фиг.2) умножитель 13 и сумматор 14. Множимо поступает на вход 15, а слагаемое на вход 16, множитель (основание входного кода) поступает на вход 17. На вход 18 поступает основание выходного кода, что обеспечивает выбор системы счисления, блоков 13 и 14.

В основу работы преобразователя кодов, при переводе числа А из системы счисления с меньшим основанием Р в счисление с большим основанием q, положен алгоритм распараллеливания исходного числа А (р) на п параллель- ных ветвей. При этом, каждая.из ветвей обрабатывается независимо друг от друга по алгоритму последователь- ного умножения старшей цифры части числа А (р) на основании исходной системы счисления р с последующим прибавлением к полученному произведению следующей по порядку цифры части числа А (р). Операции произво

г 0

5

0 5 0

с

0

д «

5

дятся в q-ичной системе счисления и процесс умножения и сложения повторяется до тех пор, пока не будет добавлена младшая цифра части числа А (р).

Преобразователь кодов работает следующим образом.

На информационные входы 7 преобразователя подается преобразуемое число А в системе счисления с осно- йанием Р, причем исходное число разбивается на п частей, каждая из которых содержит (l(,-1)-ls-разрядов (S О, 1, 2, ... (п-1); Ig ls(m + 1)/n, знак ДхЦ - ближайшее меньшее целое число m - максимальная разрядность входного кода п - целое число, . Старший разряд кода -1, каждой группы поступает на треугольные матрицы через входы 15 ячейки преобразователя 1 первой строки на входы 1 умножителя 13, на выходе которого появляется число, умноженное на константу Р исходной системы счисления. На сумматоре 14 ячейки 1 первой строки происходит суммирование результата умножения и цифры предыдущего разряда , -2 преобразуемой части числа, поступающего на входы 16 ячейки преобразования 1. Младший разряд результата, полученный на выходах 6 ячейки первой строки, поступает на входы 15 первой ячейки второй строки а старший разряд этого результата, полученный на выходах 5 ячейки, поступает на входы 15 второй ячейки второй строки и Т.Д-. в результате параллельного перевода каждой из п частей на выходах 8 каждой матрицы получаем п частей исходного числа А в счислении q. Результаты перевода, полученные на выходах 8 каждой матрицы, кроме первой, поступают параллельно на входы 15 соответствующих блоков умножения 2, на вторые входы которых подаются соответственно константы Р S в счислении q. Результат с выходов В первой.матрицы и произведения, полученные на выходах каждого из блоков умножения 2, поступают соответственно на п группу входов многовходового сумматора 3. В резуль- тате суммирования на выходах 9 получается код преобразованного числа А в системе счисления с основанием q. Операции умножения на блоках умножения 2 и суммирования на многовходов.с1М

сумматоре 3 производится в q-ичной системе счисления.

Таким образом, за один такт работы на, выходах 9 преобразователя кодов появляется код преобразованного числа в системе счисления с основанием q.

Исходя из этого, максимальная задержка процесса перевода составляет

А(Р)

(1

- 2)

макс

Ч +

ty - задержка сигнала блоком ум- ноже ния{ t - задержка сигнала многовходовым сумматором,

а время перевода числа А из счисления р в счисление q в известном преобразователе кодов, равно

T(pj (m - O t.

10

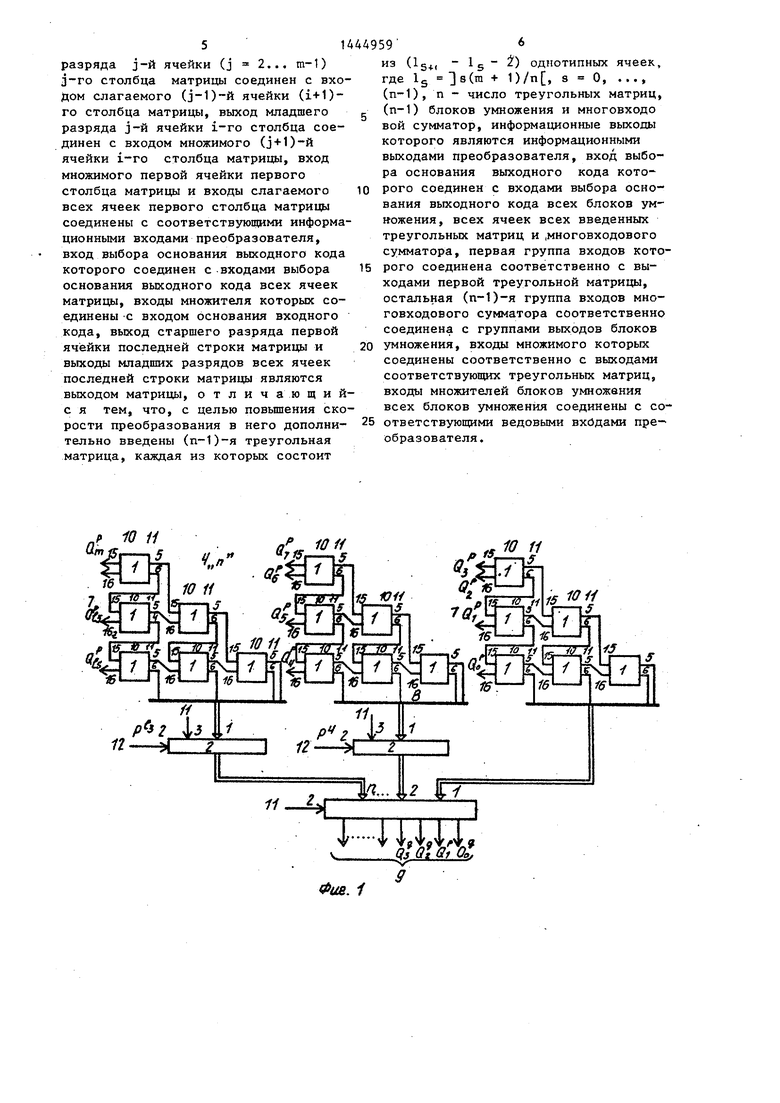

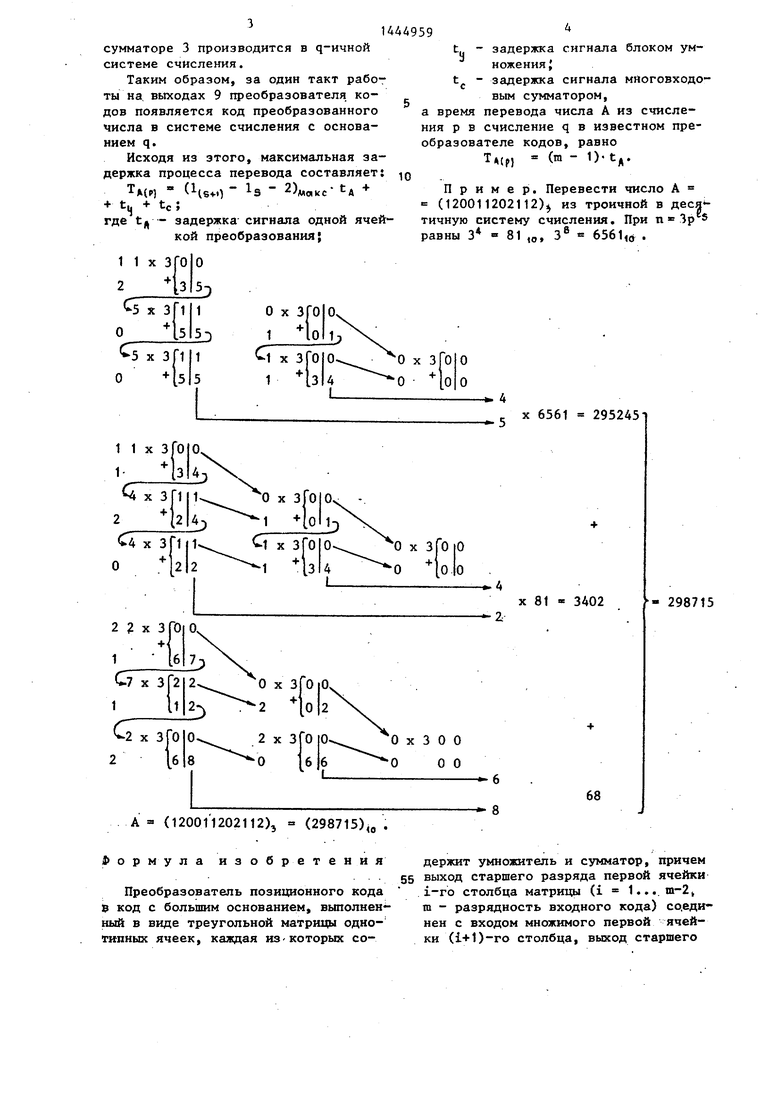

Пример. Перевести число А (120011202112) из троичной в деся счисления. При

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода в код с большим основанием | 1985 |

|

SU1332537A1 |

| Преобразователь кодов | 1977 |

|

SU779998A1 |

| Преобразователь кода в код с большим основанием | 1976 |

|

SU581469A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Преобразователь позиционного кода из одной системы счисления в другую | 1986 |

|

SU1302438A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Матричное устройство для умножения | 1981 |

|

SU972502A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1981 |

|

SU974370A1 |

| Преобразователь кодов | 1986 |

|

SU1381717A1 |

Изобретение относится к области вычислительной техники и автоматики и предназначено для перевода кодов чисел из системы счисления с любым основанием в коды чисел с любым боль- шин .основанием в цифровых системах управления и в устройствах обработки информации. Целью изобретения является повышение скорости преобразования. Поставленная цель достигается тем, что в преобразователь позиционного кода, содержащий треугольную матрицу, введена группа треугольных матриц, группа блоков умножения и многовходовый сумматор, причем каждый элемент треугольных матриц содержит умножитель и сумматор. 2 ил.

А (1200 l l 202112)5 (298715)

Формула изобретениядержит умножитель и сумматор, причем

55 выход старшего разряда первой ячейки

Преобразователь позиционного кода i-ro столбца матрицы (i 1.... m-2i 9 код с большим основанием, выполнен- га - разрядность входного кода) со.еди- ный в виде треугольной матрицы одно- нен с входом множимого первой ячей- типных ячеек, каждая из-которьк со- ки (i+1)-ro столбца, выход старшего

81

о

6561,0 .

X 6561 295245

X 81 - 3402

- 298715

10

51444959

разряда j-й ячейки (j 2.., m-1) j-ro столбца матрицы соединен с входом слагаемого (j-1)-й ячейки (i+1)- го столбца матрицы, выход младшего разряда j-й ячейки i-ro столбца соединен с входом множимого (3+1)-й ячейки i-ro столбца матрицы, вход множимого первой ячейки первого столбца матрицы и входы слагаемого всех ячеек первого столбца матрицы соединены с соответствующими информационными входами преобразователя, вход выбора основания выходного кода которого соединен с входами выбора основания выходного кода всех ячеек матрицы, входы множителя которых соединены с входом основания входного кода, выход старшего разряда первой ячейки последней строки матрицы и выходы младших разрядов всех ячеек последней строки матрицы являются выходом матрицы, отличающий15

из ds+i Ig однотипных ячеек, где Ig 8(m + 1)/п, 8 0,

г .j. --

(n-1), n - число треугольных матриц, (п-1) блоков умножения и многовходо вой сумматор, информационные выходы которого являются информационными выходами преобразователя, вход выбора основания выходного кода кото рого соединен с входами выбора основания выходного кода всех блоков умножения, всех ячеек всех введенных треугольных матриц и .многовходового сумматора, первая группа входов которого соединена соответственно с выходами первой треугольной матрицы, остальная (п-1)-я группа входов мно- говходового сумматора соответственно соединена с группами выходов блоков 20 умножения, входы множимого которых соединены соответственно с выходами соответствующих треугольных матриц, входы множителей блоков умножения всех блоков умножения соединены с сос я тем, что, с целью повьшения скорости преобразования в него дополни- 25 ответствующими ведовыми вхбдами пре- тельно введены (п-1)-я треугольная образователя. матрица, каждая из которых состоит

ФI I fiffiA

QsQlSi Ol

Фие. i

0

4959

15

из ds+i Ig однотипных ячеек, где Ig 8(m + 1)/п, 8 0,

г .j. --

(n-1), n - число треугольных матриц, (п-1) блоков умножения и многовходо вой сумматор, информационные выходы которого являются информационными выходами преобразователя, вход выбора основания выходного кода кото рого соединен с входами выбора основания выходного кода всех блоков умножения, всех ячеек всех введенных треугольных матриц и .многовходового сумматора, первая группа входов которого соединена соответственно с выходами первой треугольной матрицы, остальная (п-1)-я группа входов мно- говходового сумматора соответственно соединена с группами выходов блоков 20 умножения, входы множимого которых соединены соответственно с выходами соответствующих треугольных матриц, входы множителей блоков умножения всех блоков умножения соединены с со25 ответствующими ведовыми вхбдами пре- образователя.

9

г-1

t 5,

/5.

1 ГЗ

f

L

/

1

,г5

фиг.2

| Преобразователь кодов | 1973 |

|

SU526884A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода в код с большим основанием | 1985 |

|

SU1332537A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-05-27—Подача