(54) УСТРОЙСТВО ДЛЯ АНАЛИЗА СТРУКТУРЫ ДВОИЧНЫХ

1

Изобретение относится к области s вычислительной техники, систем автоматического управления и может быть использовано в качестве пристайки к цифровой вычислительной машине для ангитиза и предсказания двоичных последовательностей.

Известный анализатор l снятия случайных процессов, содержащий блок для выделения характеристик процесса , измерительные каналы, имеющие в своем составе счетчики, обладает способностью производить анализ представленного процесса путем разложения его на спектргшьные составляющие и изменения их интенсивностей.

Однако это устройство содержит для каждого измерительного канала свои счетчики и не позволяет осуществлять предсказание будущих значений случайных процессов.

Известен преобразователь код-вероятность Г21, содержащий счетчики, преобразователь код-напряжение, управляемый генератор случайного двоичного знака. Однако это устройство не позволяет предсказывать двоичные последовательности. ПОСЛЕДОВАТЕЛЬНОСТЕЙ

Целью изобретения является расширение функц-иональных возможностей устройства, путем предсказания будущих значений двоичных последовательностей Через определения вероятностей появления будущих .значений последовательности в зависимости от предыдущих ее значений и уменьшение, количества используемых счетчиков.

10

Эта цель достигается тем, что в устройство для анализа структуры двоичных последовательностей , содерЖсодее блок синхронизации, сдвиго 5 вый регистр, вход которого является входом устройства, преобразователь код-напряжение, выход которого подключен ко входу генератора случай-о ного двоичного знака, а выходы преобразователя код-напряжение соединены с разрясдными выходами соответственно первого и второго счетчика, введены первый и второй блоки формирования адреса, два блока злемен25 тов И, блок элементов ИЛИ и блок памяти, информационные входы которого поключены соответственно к выходам первого и второго счетчиков, адресный вход соединен с выходом блока

30 элемента ИЛИ, а управляющий вход подключей к первому выходу блока синхронизации, второй, третий

и четвёртый выхода которого соёдийгёны сбответствёйно и управляйпшМй входами второго счетчика, первого и второго блоков элементов И, вход блока синхронизации соединен с входом устройства, разрядные СДВИГОВОГО регистра; кром;е П(:эсЛёДнегЬ, соединены с соответствующими входами первого блока формиро васнйя адреса, разрядные выходы сдви - рОгвогб регистра, кроме первого; под ТИйЧ11Ш Г сЬотже; ству1оЩим вхвй

второго блока фОЕ 1Ирования адреса, выходы блоков формирования адреса

-.подключены соответственно к информаf цШййьвд входам первого и второго бло,ков элементов И, выходы которых подключены соответственно к первой и второй группе входов блока элементов ИЛИ, выход первого разряда сдвигового регистра соединен с управляющим

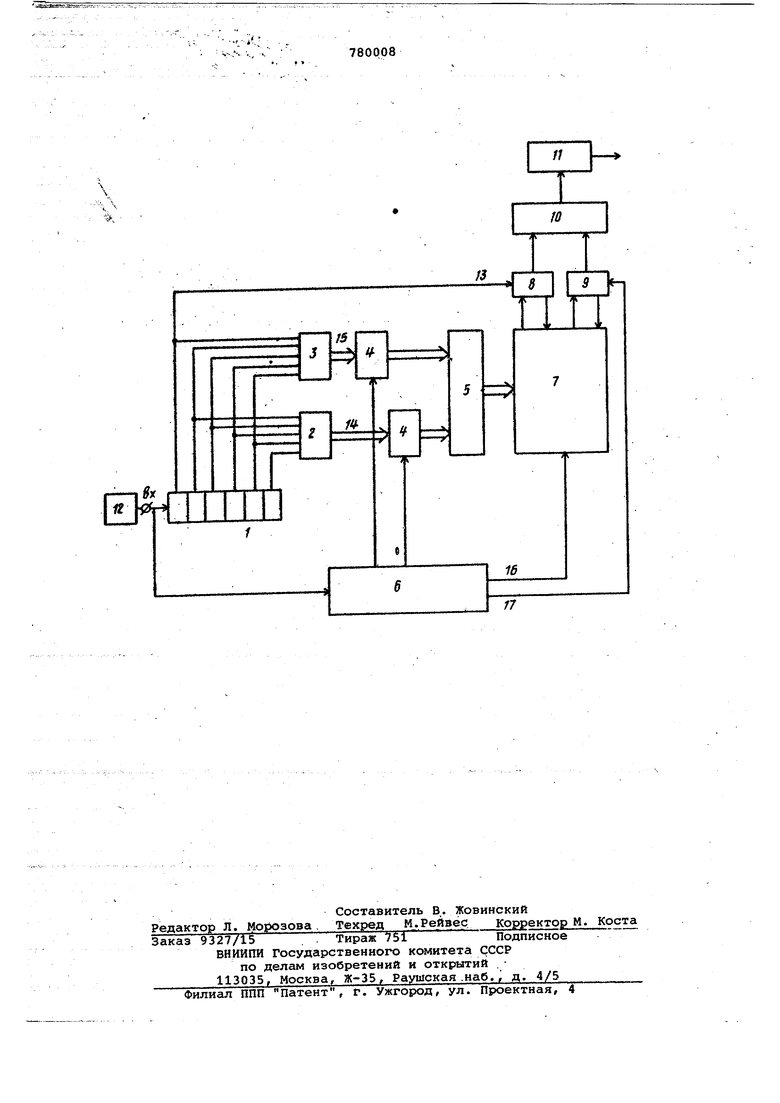

вводом первого счетчика, установочные входы первого и второго счетчи ikOB подключены соответственно к пер-. вЬму и второму выходам блока памяти. Блок-схема описываемого устрой ;;ctBa показана на чертеже. Каждая--- ячейка Влб1йа памйти разделена н& две

части. В старших разрядах содержится информация о числе появления определенного набора значений пос лёДовательности, определякмцего адрес этой 1ячеЙкиГ, § МладШхраШрЩа Г Находится информация о числе появлений значения 1 после данного набора значений. Отношение этих частей информации представляет собой частоту появления сигнала 1 пбсйе ПО яГЖГйГй-аййбго предшествующего набора значений.

Устройство содержит сдвиговый регистр 1, блок 2 формирования адреса пре1Ш1ествующего набора, блок 3 формирования адреса текущего набора, блек 4 элементов И,блок 5 элементов ИЛИ,

16 ШИХрЬнйза ций управления

адресный блок 7 памяти с присоединёнными к нему счетчиками 8 и 9,

преобразователь 10 код-напряжение

и Управляемый генератор 11 случай Ного двоичного знака. Входные сигна л1&1 задаются от источника 12, пере.дача сигналов внутри устройства осу -с ёСтвляется с помощью шин 13, 14, 15, 16, 17.

Устройство работает следующим образом.

ДвоТУчные сигнсшй, постуГОШйе бт источника 12, последовательно подаюг я и записываются в сдвиговый регистр 1 таким образом, что в каждый момент времени на нем записано 1Ш ё зй-а4ение последовЖтЩйьности

,; и предшествующий набор зйачёнйй последовательности. Этот набор значений подается на вход блока 2 формирования адреса, где вычисляется адрес блока-7 памяти, по которому записывается информация о частоте появления значения 1 последовательйости после возникновения на входе устройстваданного предшествующего . набора значений. Например, в качестве адреса может быть выбран двоичный код, который образуют значения набора последовательности.

Блок б управления, открывая и закрывая соответствующие блоки 4 элементов И, пропускает на адресные входы блока 7 памяти через блок 5 элементов ИЛИ информацию с шин 14,

.а также вырабатывает сигнал Чтение на шине 16 для блока 7 памяти. В результате эТогО из записывающего устройства будет прочитана информация о частоте появления 1 после данного набора значений. Эта информация записывается в счетчики 8 и 9 соответственно, после чего сигнал текущего значёЙйя последовательности,

присутствующий на шине 13, поступает на. вход счетчика 8, а блок б управления вырабатывает синхронизирующий сигнал 17, поступающий на вход счетчика 9. В счетчиках 8 и 9 про изводится суммирование, т.е. корректировка частоты появления значения 1 после данного набора. Затем блок 6 управления вырабатывает на шине

0 35 16 сигнал Запись, благодаря которому информация со счетчиков 8 и 9 записывается в соответствующую ячейку блока 7 памяти.

Таким образом, производится формирование распределения частот появления будущих значений, равных 1, в зависимости от предыдущих значений предсказываемой последовательности.

г

По завершении этого этапа блок 6 управления переключает сигналы на блоках 4 так, что на адресные входы блока 7 через блок 5 элементов ИЛИ. поступают сиг-налы с шин 15 блока

5 50 55 3 формирования адреса, соответствующего текущему набору значений последовательности. На шине 16 формируется сигнал Чтение и в счетчики 8 и 9 записывается информация о часпосле данного тетоте появления

ущего набора, которая поступает на входы преобразователя 10 код-напряжение . Этот блок осуществляет преобразование цифрового кода частоты в соответстЁующеепороговое напряже ййе, пойКЯШчеМйОе к уйравляющему входу генератора 11 случайного двоичного знака. Величина порогового напрйжеййя ОПреДеляет распределение

0 65 случайного двоичного знака, соответствующее частоте появления 1 после данного набора последовательности.

Генератор 11 вырабатывает выходной двоичный Сигнал, Который распределен так же, как будущее значение последовательности, равное 1

Этот сигнал интерпретируется как будущее значение двоичной последовательности, поскольку распределение единиц полностью определяет распределение нуЛей, а отсутствие 1 в двоичной последовательности означает присутствие О и наоборот.

С течением времени число появлений двоичных наборов значений последовательности возрастает. Поэтому . из закона больших чисел следует, что частоты, накопленные в ячейках запоминакяцего устройства, стремятся к вероятностям появления значений 1 после соответствующих наборов значений .последовательности.

Если характер предсказываемой последовательности медленно изменяется, то распределение случайной двоичной величины, появляющейся на выходе генератора 11 с вероятностью, стремящейся к единице, все более приближается к распределению искомой величины. Отсюда следует, что вероятность ошибки предсказания будущего значения исследуемой двоичной случайной последовательности, приносимой преобразователем 10 и генератором 11, убывает с течением времени.

Вероятность общей ошибки пред- j. сказания будущего значения определяется длиной предгаествующего набора значений последовательности и будет тем меньше, чем больше указанная длина.

Из написанного видно, что основную задержку при вычислении будущего значения последовательности привносит работа измерительных каналов. Эта задержка равна сумме времени выборки значения ячейки из блока памяти по адресу, определяемому шинами 15 и временем срабатьгоания преобразователя 10 и генератора 11/ временем выборки ячейки, определяемо шинами 14, временем сложения содержимого этой ячейки соответствующими сигналами на счетчиках 8 и 9 и времени записи содержимого счетчиков по адресу, определяемому шинами 14. Однако за счет этой згщержки число счетчиков измерительных каналов уменьшилось до двух и не зависит .от количества каналов, которое, очевидно, определяется длиной учитываемого предшествующего набора значений последовательнсСсти и равно 2 , где п - длина набора.

Таким образом, для случайных последовательностей, у которых среднее время между появлениями зна- чений больше общей временной задержки, вызванной работой всех блоков, предложенное устройство обладает достаточной эффективностью.

Формула изобретения .

Устройство для анализа структуры двоичных последовательностей, содержащее блок синхронизации, сдвиговый регистр, вход которого являет0ся входом устройства, преобразователь код-напряжение, выход которого подключен ко входу генератора случайного двоичного знака, а входы преобразователя код-напряжение соединены

5 с разрядными выходами соответственно первого и второго счетчиков, о тличающееся тем, что , с целью расширения функциональных возможностей за счет предсказания двоичных последовательностей , в устрой0ство введены перчый и второй блоки формирования адреса, два блока элементов И, блок элементов ИЛИ и блок памяти, информационные входы которого подключены соответственно к вы5ходам первого и второго счетчиков адресный вход соединен с выходом блока элемента ИЛИ, а управл5шщий вход подключен к первому выходу блока синхронизации, второй, третий и

0 четвертый выходы которого соединены соответственно с ултравляющими входами второго счётчика, первого и второго блоков элементов И, вход блока синхронизации соединен с входом

5 устройства, разрядные выходы сдвигового регистра, кроме последнего, соединены с соответствуквдими входами первого блока формирования адреса, разрядные выходы сдвигового регистра,

0 кроме первого, подключены к соответствующим входам второго блока формирования адреса, выходы блоков формирования адреса подключены соответственно к информационным входам первого и второго блоков элементов

5 И, выходы которых подключены соответственно к первой и второй группе входов блока элементов ИЛИ, выход первого разряда сдвигового регистра соединен с управляющим входом перво0го счетчика, установочные входы первого и второго счетчиков подключены соответственно к первому и второму выходам блока памяти.

55

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №442434, кл. G 01 R 23/00, 1972.

2.Федоров Р.Ф. и др. СтохастиAQ ческие преобразователи информации,

Машиностроение, М., 1978, с. 110,

131.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОННЫХ СЕТЕЙ | 1990 |

|

RU2045778C1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство сжатия информации | 1980 |

|

SU942109A2 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Генератор случайных процессов | 1984 |

|

SU1309021A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

Авторы

Даты

1980-11-15—Публикация

1978-05-03—Подача