() ДЕШИФРАТОР ДЛЯ ПОСЛЕДОВАТЕЛЬНЫХ ДВОИЧНЬЖ КОДОВ «. . Изобретение относится, к области вычислительной техники и может быть использовано в цифровых системах телемеханики для обнаружения и исправлеиия ошибок типа трансформации или/и стирания символов в принятой кодовой комбинации. Известен дешифратор для последовательных двоичных кодов, содержащий кольцевые регистры сдвига, логически элементы ИЛИ и пороговый логический элемент ll- , Недостатком дешифратора является его нёдоста точная помехоустойчивость Наиболее блйзйии техническим реше нием к данному изобретению является дешифратор для последовательных двоичных кодов, содержаодий Кольцевые ре гистры сдвцга и логические элементы ИЛИ и и 2 . Недостатком известного дешифратора является то, что он не мсйкёт ис,править все возможные варианты ошибо типа стирания символов максимальной кратности Ч/Аокс NVM« т.е. не позволяет полностьюреализовать корректирующую способность кода. Целью изобретения является повышение помехоустойчивости дешифратора для последовательных двоичньк кодов. Поставленная цель достигается путем того, что дешифратор для последовательных двоичных кодов, содержащи основной и дополнительные кольцевые регистры сдвига, выходы каждого последующего дpпoJnнитeльнoгo регистра сдвига соединены со входами предыдущего дополнительного регистра сдвигл, а выходы первого дополнительного региртра сдвига соединены со входами основного регистра сдвига, основные логические элементы ИЛИ, блок сравнения, первый и второй выходы которого соединены со входами первого основного логического элемента ИЛИ, а второй и третий выходил - со входами второго основного логического элемента ИЛИ, выходы основных логических элементов ИЛИ соединены с соответсТвущими входами основного и всех дополнительных регистров сдвига, содержит счетчик импульсов, логические элементы И, дополнительные логические элементы ИЛИ, вход счетчика импульсов соединен со вторым выходом блока сравнения , первый выход счетчика импульсов соединен со входами одних логических элементов И, вторые входы которых соединены с выходами основного регистра сдвига,.второй

выход счетчика импульсов соединен со входами других логических элементов И, вторые входы которых .соединены с выходами первого дополнительного регистра сдвига, выходы логических элементов И, входы которых соединены с одноименньаии выходами основного и первого дополнительного регистров сдвига, соединены со дополнительных логических элементов ИЛИ..

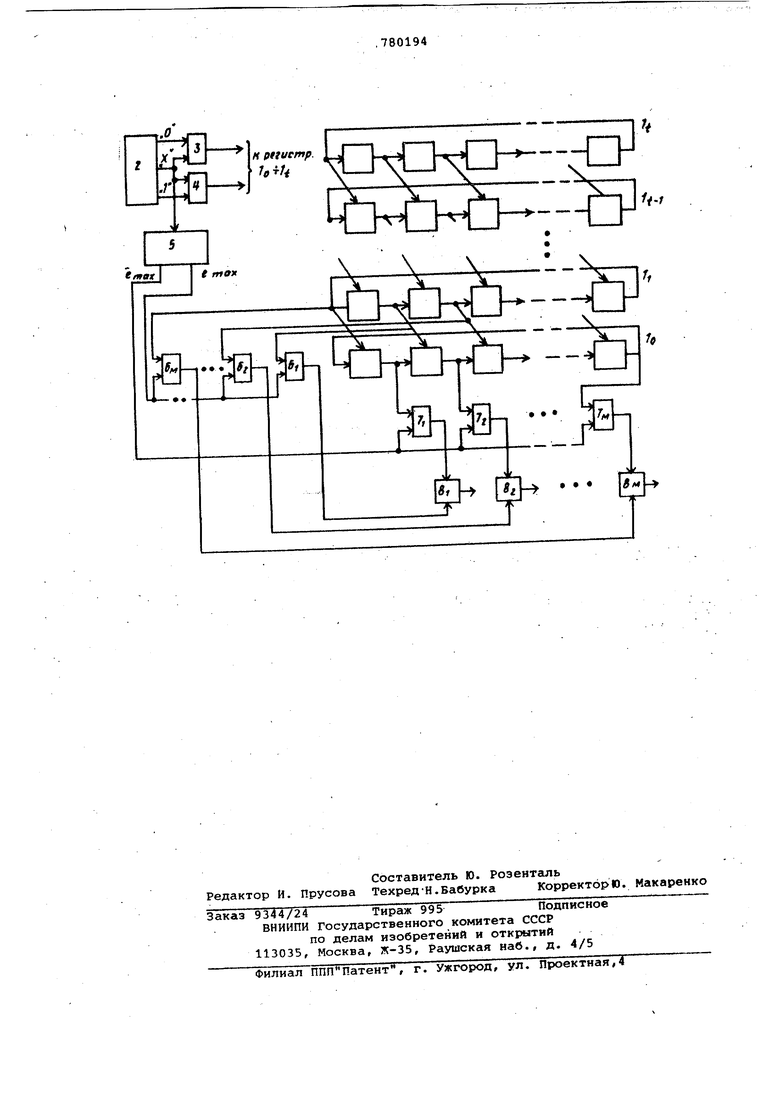

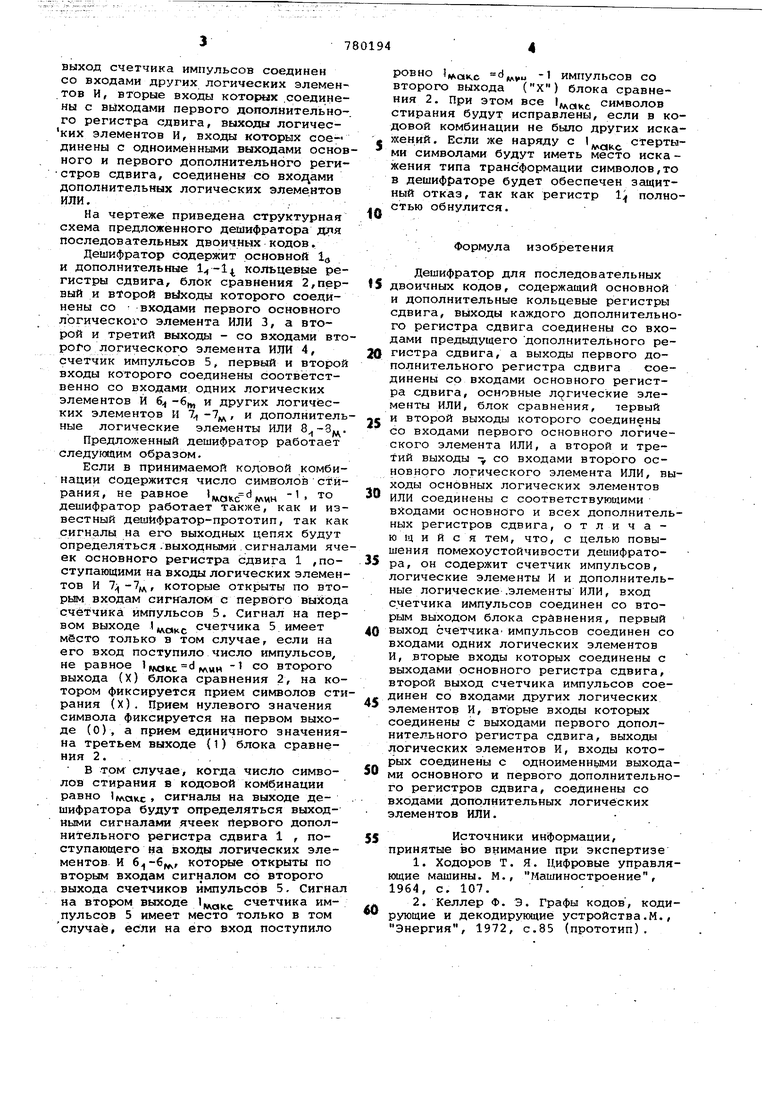

На чертеже приведена структурная схема предложенного дешифратора для последовательных двоичных кодов.

Дешифратор содержит основной (, и дополнительные . кольцевые регистры сдвига, блок сравнения 2,первый и второй вУходы которого соединены со входами первого основного лргическохО элемента ИЛИ 3, а второй и третий выходы - со входами второго логического элемента ИЛИ 4, счетчик импульсов 5 первый и второй входы которого соединены соответственно со входами одних логических элементов И 6 , и других логических элементов И 7, -7, и дополнительные логические элементы ИЛИ .

Предложенный дешифратор работает следующим образом.

Если в принимаемой кодовой комбинации Содержится число симвголов сТйрания, не равное w, дешифратор работает также, как и известный дешифратор-прототип, так как сигналы на его выходных цепях будут определяться .выходными.сигналами ячеек основного регистра сдвига 1 ,поступающими на входы логических элементов И 7;,-7, которые открыты по вторым входам сигналом с первого выхода счётчика импульсов 5. Сигнал на первом выходе I (ленке счетчика 5 имеет место только в том случае, если на его вход поступило число импульсов, не равное плакс WVMH второго выхода (X) блока сравнения 2, на котором фиксируется прием символов стирания (X). Прием нулевого значения символа фиксируется на первом выходе (0), а прием единичного значенияна третьем выходе {1) блока сравнения 2. . , В том случае, когда число символов стирания в кодовой комбинации равно IfActKc сигналы на выходе дешифратора будут определяться выходными сигналами ячеек первого дополнительного регистра сдвига 1 , поступающего на входы логических элементов И , которые открыты по вторым входам сигналом со второго выхода счетчиков импульсов 5, Сигнал на втором выходе 1, счетчика импульсов 5 имеет место только в том случае, если на его вход поступило

ровно .u -1 импульсов со второго выхода (X) блока сравнения 2. При этом все 1ддакс символов стирания будут исправлены, если в кодовой комбинации не было других искажений. Если же наряду с 1..., стертыn dKO

ми символами будут иметь место иска жения типа трансформации символов,то в дешифраторе будет обеспечен защитный отказ, так как регистр 1 полностью обнулится.

Формула изобретения

Дешифратор для последовательных двоичных кодов, содержащий основной и дополнительные кольцевые регистры сдвига, выходы каждого дополнительного регистра сдвига соединены со входами предьщущего дополнительного регистра сдвига, а выходы первого дополнительного регистра сдвига соединены со входами основного регистра сдвига, основные логические элементы ИЛИ, блок сравнения, лервый и второй выходы которого соединены со входами первого основного логического элемента ИЛИ, а второй и третий выходы со входами второго основного логического элемента ИЛИ, выходы основных логических элементов ИЛИ соединены с соответствующими входами основного и всех дополнительных регистров сдвига, отличающийся тем, что, с целью повышения помехоустойчивости дешифратора, он содержит счетчик импульсов, логические элементы И и дополнительные логические .элементы ИЛИ, вход счетчика импульсов соединен со вторым выходом блока сравнения, первый выход счетчика импульсов соединен со входами одних логических элементов И, .вторые входы которых соединены с выходами основного регистра сдвига, второй выход счетчика импульсов соединен со входами других логических элементов И, вторые входы которых соединены с выходами первого дополнительного регистра сдвига, выходы логических элементов И, входы которых соединены с одноименными выходами основного и первого дополнительного регистров сдвига, соединены со входами дополнительных логических элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Ходоров Т. Я. Цифровые управляющие машины. М., Машиностроение, 1964, с. 107.

2.Келлер Ф. Э. Графы кодов , кодирующие и декодирующие устройства.М., Энергия, 1972, с.85 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор для последовательных двоичных кодов | 1978 |

|

SU877789A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| Устройство для приема избыточной информации | 1989 |

|

SU1786498A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДВОИЧНЫХ КОДОВ ХЕММИНГА | 1999 |

|

RU2161369C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

Авторы

Даты

1980-11-15—Публикация

1978-04-10—Подача