1

Изобретение относится к вычислительной технике и может быть использовано в аналогоцифровых вычислительных системах.

Известно цифровое устройство для деления чисел, поступающих в устройство параллельным кодом, содержащее щ{фровые блоки, реализующие операции запоминания, сложения, сдвига и др. 1.

Недостаток устройства - большие аппаратурные затраты на организацию канала связи между цифровыми блоками.

Наиболее близким к предлагаемому является делительное устройство, которое дает возможность вычислить одноразрядные приращения частного при поступлении на его вход одпоразрядных приращений делимого и делителя, что позволяет, по сравнению с цифровыми устройствами для деления чисел, поступающих в устройство параллельным кодом, уменьшить затраты оборудования на организацию каналов связи с другими подобными устройствами, т.е. упростить системную связь. Например, вычислительная структура с составной частью известного устройства позволяет распараллелить процесс вычислений, что дает возможность строить достаточно высокопроизводительные проблемноориентированные процессоры 2.

В известном устройстве процесс деления основан на формуле дифференциального исчисления

.-Ai« ,

где 2. частное;

дх - приращение частного,; - делитель; ) - приращение делителя;

Ж - делимое;

ДХ - приращение делимого, в то время, как точная формула дифференциального исчисления

дх z-Av

Однако Из-за отбрасывания величины uit U V и нем происходит накопление погрешности по мере вычислений.

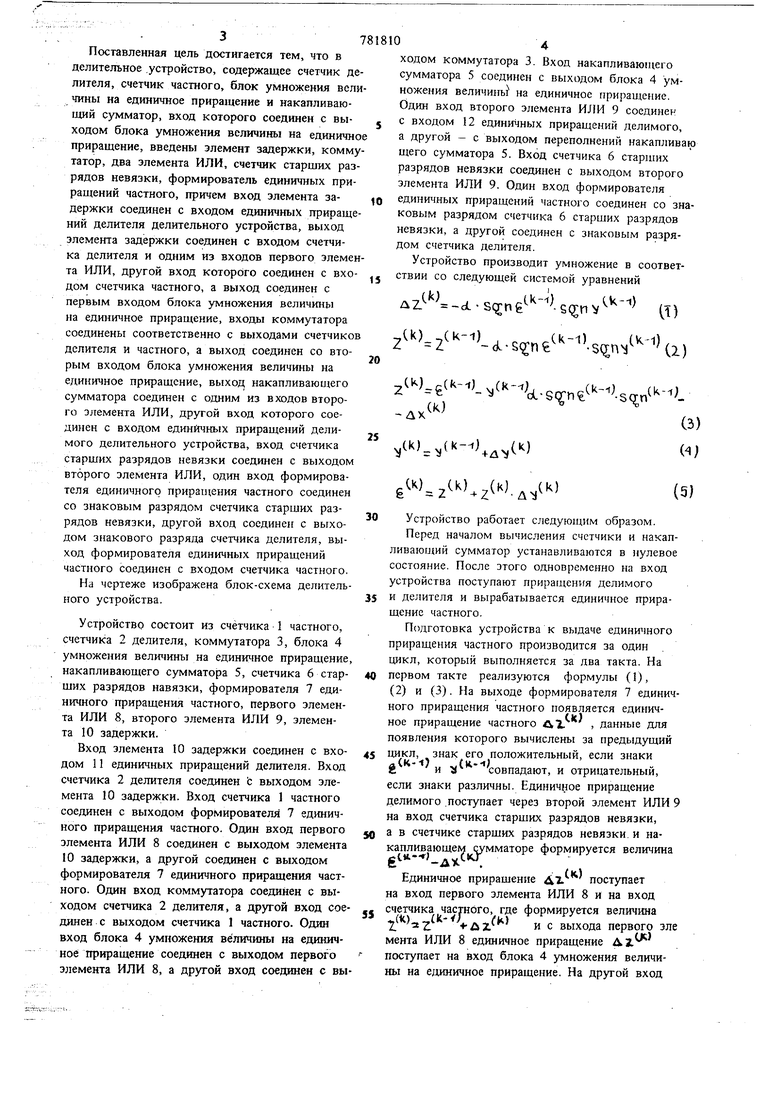

Целью изобретения является повышение точности вычислений. 3 Поставленная цель достигается тем, что в делительное .устройство, содержащее счетчик де лителя, счетчик частного, блок умножения вел чины на единичное приращение и накапливающий сумматор, вход которого соединен с выходом блока умножения величины на единично приращение, введены элемент задержки, комму татор, два элемента ИЛИ, счетчик старщих раз рядов невязки, формирователь единичных приращений частного, причем вход элемента задержки соединен с входом единичных прираще ний делителя делительного устройства, выход элемента задержки соединен с входом счетчика делителя и одним из входов первого элемен та ИЛИ, другой вход которого соединен с вхо дом счетчика частного, а выход соединен с первым входом блока умножент величины на единичное приращение, входы коммутатора соединены соответственно с выходами счетчико делителя и частного, а выход соединен со вторым входом блока умножения величины на единичное приращение, выход накапливающего сумматора соединен с одним из входов второго элемента ИЛИ, другой вход которого соединен с входом единичных приращений делимого делительного устройства, вход счетчика старших разрядов невязки соединен с выходом второго элемента ИЛИ, один вход формирователя единичного приращения частного соединен со знаковым разрядом счетчика старших разрядов невязки, другой вход соединен с выходом знакового разряда счетчика делителя, выход формирователя единичных приращений частного соединен с входом счетчика частного. На чертеже изображена блок-схема делительного устройства. Устройство состоит из счётчика 1 частного, счетчика 2 делителя, коммутатора 3, блока 4 умножения величины на единичное приращение накапливающего сумматора 5, счетчика 6 старщих разрядов навязки, формирователя 7 единичного приращения частного, первого элемента ИЛИ 8, второго элемента ИЛИ 9, элемента 10 задержки. Вход элемента 10 задержки соединен с входом 11 единичных приращений делителя. Вход счетчика 2 делителя соединен t выходом элемента 10 задержки. Вход счетчика 1 частного соединен с выходом формирователя 7 единичного приращения частного. Один вход первого элемента ИЛИ 8 соединен с выходом элемента 10 задержки, а другой соединен с выходом формирователя 7 единичного приращения частного. Один вход коммутатора соединен с выходом счетчика 2 делителя, а другой вход сое динен с выходом счетчика 1 частного. Один вход блока 4 умножения величины на единичное гфиращение соединен с выходом первого элемента ИЛИ 8, а другой вход соединен с вы 0 ходом коммутатора 3. Вход накаплиБаюп1его сумматора 5 соединен с выходом блока 4 умножения величины на единичное приращение. Один вход второго элемента ИЛИ 9 соединен с входом 12 единичных приращений делимого, а другой с выходом переполнений накапливаю щего сумматора 5. Вход счетчика 6 старших разрядов невязки соединен с выходом второго элемента ИЛИ 9. Один вход формирователя единичных приращений частного соединен со знаковым разрядом счетчика 6 старщих разрядов невязки, а другой соединен с знаковым разрядом счетчика делителя. Устройство производит умножение в соответствии со следующей системой уравнений it) /..s,(jn.) CK)(k-.)(K-.;.(K,;(,.,; (3) ). Xk),,.(k) Устройство работает следуЕощим образом. Перед началом вычисления счетчики и накапливающий сумматор устанавливаются в 1улевое состояние. После этого одновременно на вход устройства поступают приращения делимого и делителя и вырабатывается единичное приращение частного. Подготовка устройства к вьщаче единичного приращения частного производится за один цикл, который выполняется за два такта. На первом такте реализуются формулы (I), (2) и (3). На выходе формирователя 7 единичного приращения частного появляется единичное приращение частного АХ данные д;ш появления которого вычислены за предыдущий цикл, знак его положительный, если знаки g У совпадают, и отрицательный, если знаки различны. Единич11ое приращение делимого .поступает через второй элемент ИЛИ 9 на вход счетчика старщих разрядов невязки, а в счетчике старщих разрядов невязки, и накапливающем сумматоре формируется величина Единичное приращение Дг поступает на вход первого элемента ИЛИ 8 и на вход счетчика частного, где формируется величина и с выхода первого эле мента ИЛИ 8 единичное приращение Д1 поступает на вход блока 4 умножения величины на е;ишичное приращение. На другой вход

Плока 4 умножения

величин1 1 иа единичное прира1Г1Сние с коммутатора 3

поступает величиf и

на ду , и иа выходе этого блока формируется величина

d-scjne - U.jnv,).

-д Полученная величина поступает на вход накапли вающего сумматора 5, и в накапливающем сум маторе 5 и счетчике старших разрядов невязки 6 формируется величина ).е(-))(к-1)..,(к-1). SC hviC После окончания переходных процессов в накапливающем сумматоре 5 и счетчике 6 старши разрядов невязки начинается второй такт. На втором такте реализуются формулы (4) и (5). С выхода элемента 10 задержки единимное приращение делителя AV поступает на вход счетчика 2 делителя , где формируется ве...), Кроме этого, через первый элемент ИЛИ 8 единичное приращение поступает на вход блока 4 умножения величины на единичное приращение. Част f ное г со счётчика 1 частного поступает чере коммутатор 3 на вход блока 4 умножения величины на единичное приращение, с выхода которого величина Д поступает на вход накапливающего сумматора 5. В накапливающем сумматоре 5 и в счетчике 6 старших разрядов невязки формируется величина g(KL(K)tK)(K) Частное находится тогда когда единичное приращение делителя, делимого и частного после каждого цикла меняет знак, т.е. когда в счетчике делителя хранится величина, равная задаваемой величине делителя или меньше ее на единичное приращение, в счетчике частного хранится найденная величина частного, а невязка 4 после каждого цикла меняет знак. Алгебраическая сумма приращений, выданных с формирователя единичных приращений частного, равная искомой величине частного, выдается в другое устройство. Устройство позво ляет получать частное без накопления погрешности по мере вычислений. Использование устройства целесообразно для построения блочных вычислительных структзф

с большим временем непрерывного моделирования процесса, где при большом числе итераций не должно происходить накопления погрешности. Формула изобретения Делительное устройство, содержащее счетчик делителя, счетчик частного, блок умножения величины на единичное приращение и накапливающий сумматор, вход которого соединен с ВЫХОДОМ блока умножения ве;шчины на единичное приращение, отличающееся тем, что, с целью повышения точности, в него введены элемент задержки, коммутатор, два элемента ИЛИ, счетчик старших разрядов невязки, формирователь единичных приращений частного, причем вход элемента задержки соединен с входом единичных приращетшй делителя делительного устройства, выход элемента задержки соединен с входом счетчика делителя и одним из входов первого элемента ИЛИ, другой вход которого соединен с входом счетчика частного а выход соединен с первым входом блока умножения на единичное приращение, входы коммутатора соединены соответственно с выходами счетчиков делителя и частного, а выход соединен со вторым входом блока умножения величины на единичное приращение, выход накапливающего сумматора соединен с одним из входов второго элемента ИЛИ, другой вход которого соединен с входом единичных приращений делимрго делительного устройства, вход счетчика старших разрядов невязки соединен с выходом второго элемента ИЛИ, один вход формирователя единичного приращения частного соединен со знаковым разрядом счетчика старших разрядов невязки, другой вход соединен с выходом знакового разряда счетчика делителя, выход формирователя единичных приращений частного соединен с входом счетчика частного. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 549808, л. G 06 F 7/50, 1975. 2.Неслуховский К. С. Цифровые дифференциальные;, анализаторы. М., Машиностроение, 1968, с. 92-94, рис. 28 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1979 |

|

SU781809A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

«r

41

-Jn

Авторы

Даты

1980-11-23—Публикация

1979-03-19—Подача