умножения, начиная с младших разрядов IQразряд вправо и записьгоаются соответмножителя со сдвигом частичного про-ственно в регистре 1 и регистре 24.

изведения и множителя на один разрядОсвоболщающийся разряд слева региствправо вс; время.каждой интерйцни.ра 24 заполняется младшим разрядом

При вьполнении умножения множитель от суммы частичного произведения при

преобразуется из дополнительного кода isсдвиге его вправо на один разряд

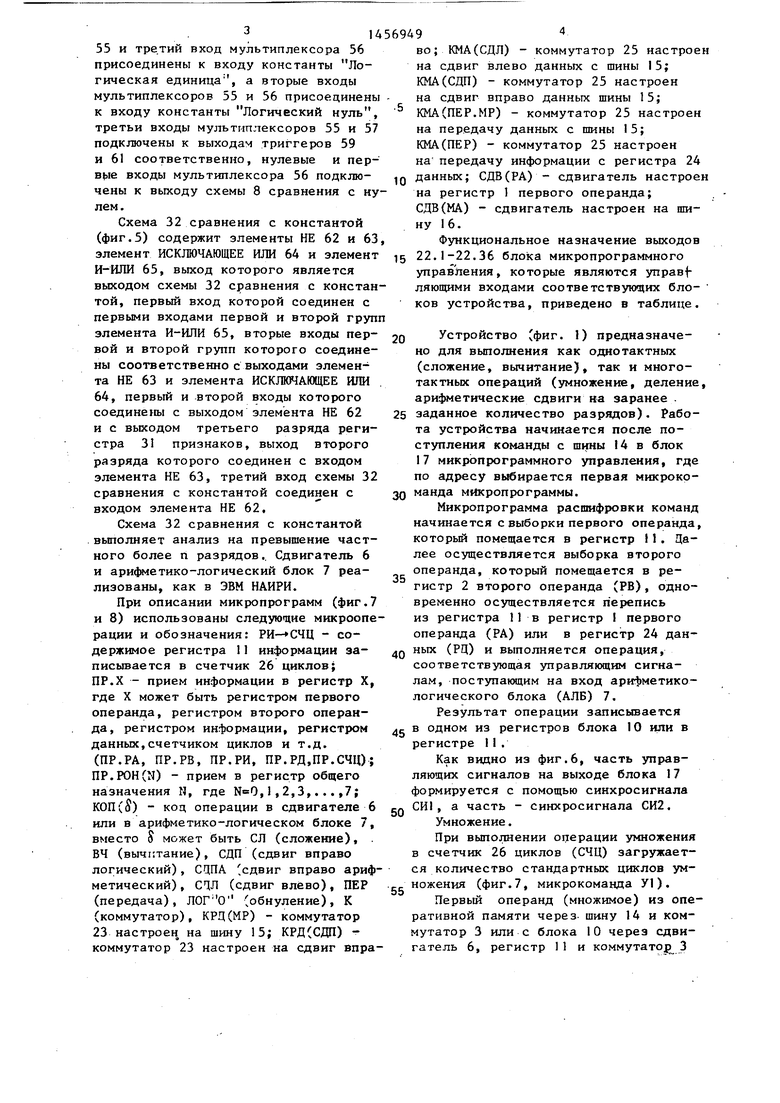

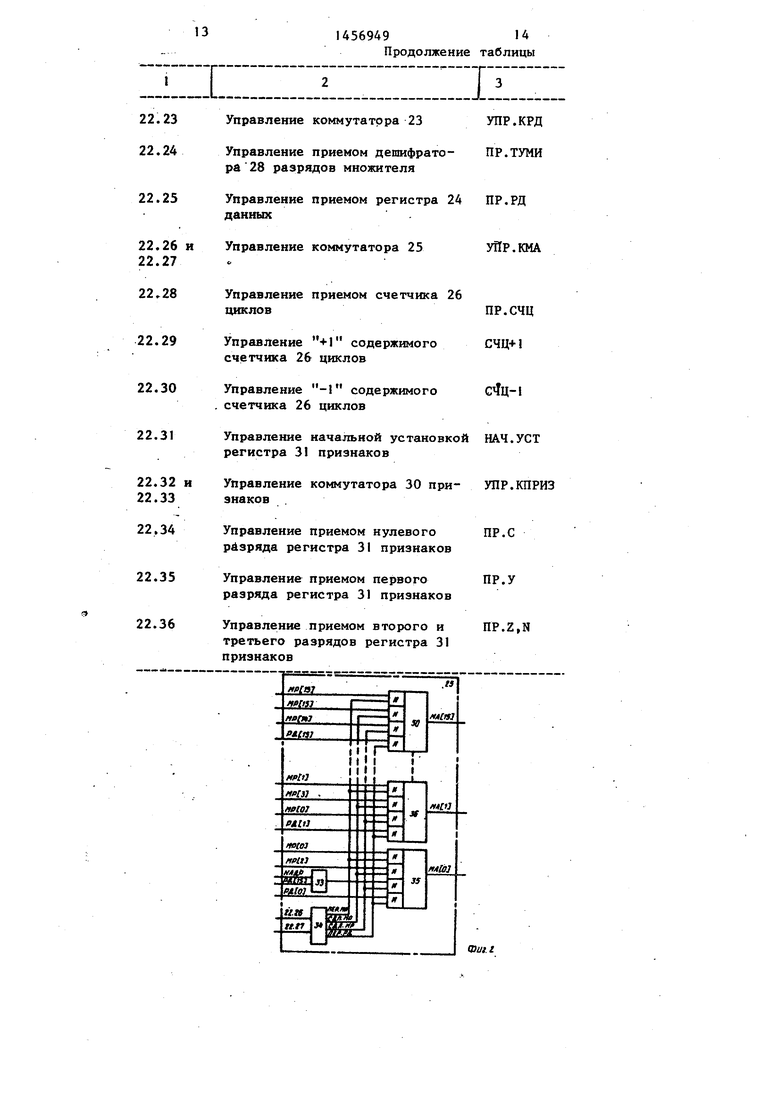

в модифицированный (1, 01), который реализуется с помощью дешифратор а 28 (ТУМН) (фиг.З) в процессе вьтолнения умножения анализом младших разрядов множителя и текущего содержимого дешифратора .28, запоминающего тип пре- дьщущего преобразования.

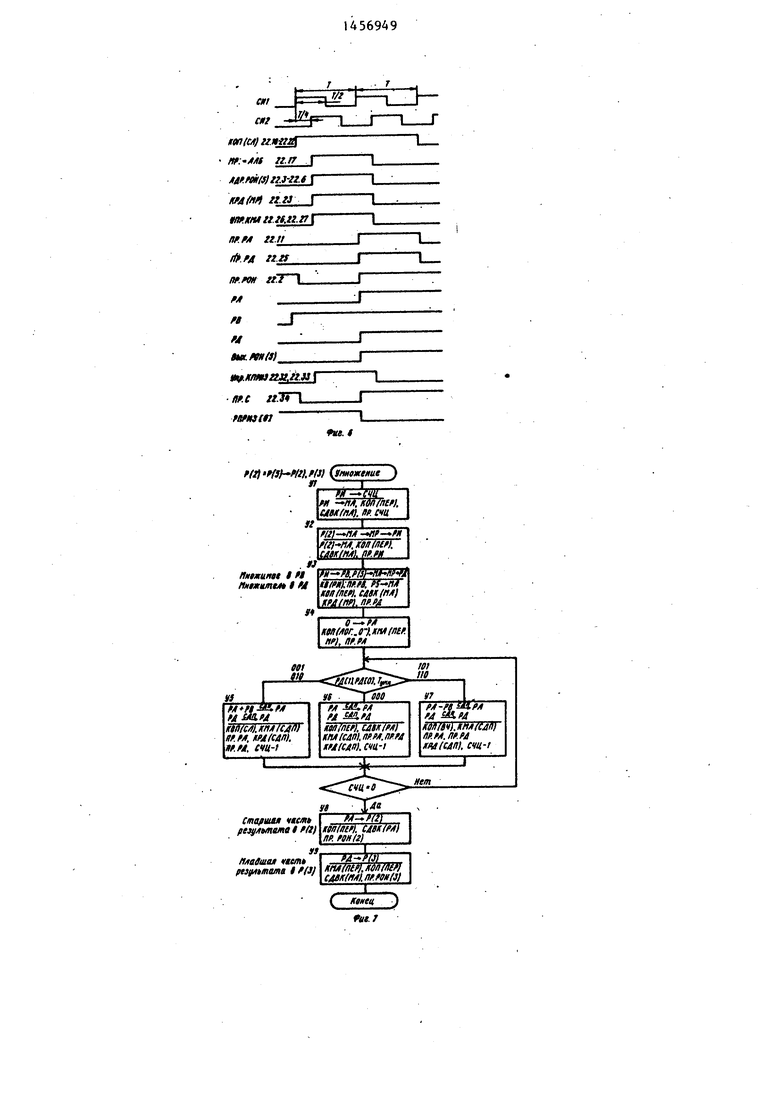

После того, как в регистр 1, хранящий сумму частичных произведений (СЧП), записывается нуль (микрокоманда У4), начинается стандартный 1ДИКЛ умножения. В каждом стандартном цикле умножения анализируются два младших разряда множителя (,

(микрокоманда У5), при этом в дешифратор. 28 записьшается нуль.

В конце каждой микрокоманды (У5, У6, У7) содержимое счетчика 26 умень- 20 шается на единицу и осуществляется анализ содержимого на нуль. Выход из стандартного цикла умножения происходит по равенству нулю содержимого счетчика, после чего осуществляется 25 запись результата микрокомандами У8 (старшая часть) и У 9 (младшая часть).

Деление.

„ J.При выполнении операции деления

РД 1J ) и текущее содержимое дешифра- ЗО 2п-разрядное делимое, записанное тора 28. При этом различают следующие в дополнительном коде в п-разрядных

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Операционное устройство | 1985 |

|

SU1367012A1 |

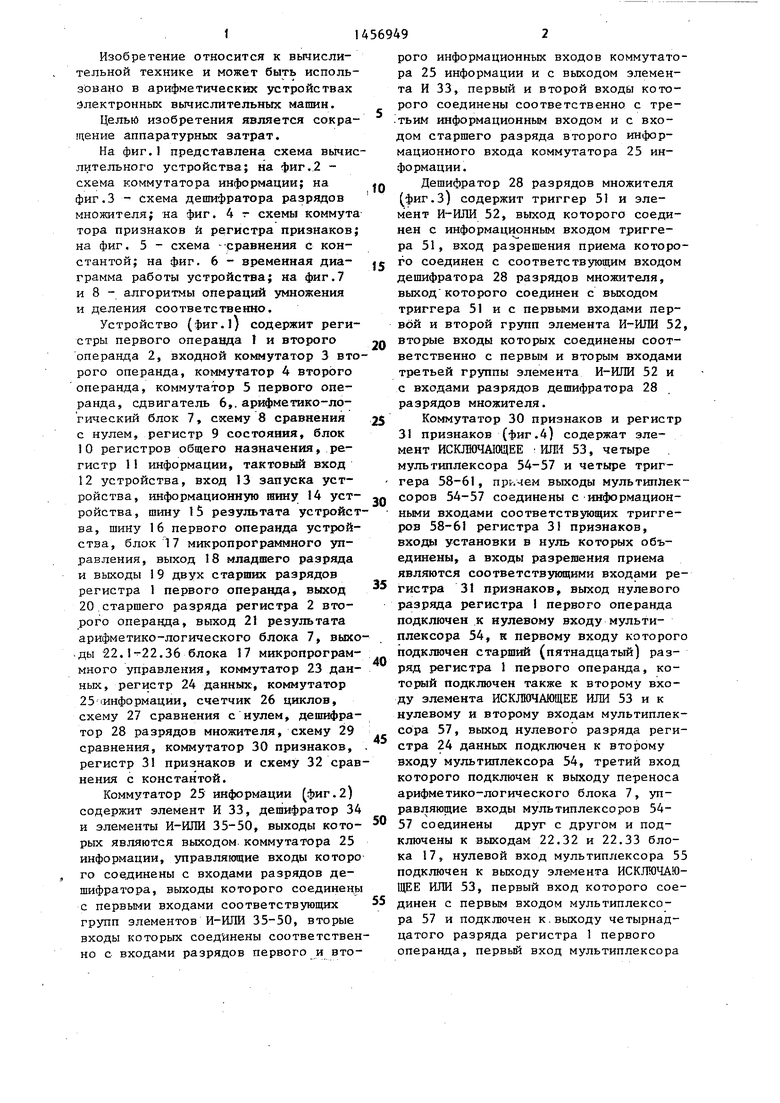

Изобретение относится к вьмис- лительной технике и может быть использовано в арифметических устройствах электронных вычислительных машин. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем. что вычислительное устройство, содержащее регистры 1,2 первого и второго операндов, входной коммутатор 3 второго операнда, коммутатор 4 второго операнда, коммутатор 5 первого операнда, сдеигатель 6, арифметико- логический блок 7, схемы 8,27 сравнения с нулем, регистр 9 состояния, блок 10 регистров общего назначения, регистр 11 информации, блок 17 микропрограммного управления, коммутатор 23 данных, регистр 24 данных, коммутатор 25 информации, счетчик 26 циклов, дешифратор 28 разрядов множителя, схему 29 сравнения, содержит коммутатор 30 признаков, регистр 31 признаков и схему 32 сравнения с константой с соответствующими связями. 8 ил., 1 табл. ш (Л

случаи.

РД О ;0 РД о 0 ТУМН- о или

РД 1 1 РД 0 0 .

Содержимое регистра 1 (СЧП) и регистра 24 (множитель) сдвигается вправо на один разряд,, при этом содержимое младшего разряда регистра сдвигается в старйшй разряд регистра 24, в дешифратор 28 записывается нуль микрокоманда У6). РД 1 0 РД 01 1 или РД 1 Г РД О 1 .

Этот слзгчай выполняется аналогично предыдущему с той разницей, что при этом в дешифратор 28 записьюается единица (микрокоманда У6).. РЦ СО 1 РД или РД С} 1 РД 0 .

Из содержимого регистра 1 вычита- 50 равен нулю, то определяется

ется содержимое регистра 2 (множимое), затем полученный результат и множитель сдвигаются на один разряд вправо и записываются соответственно в регистре 1 и регистре 24. Освобождающийся разряд слева регистра 24 заполняется младшим разрядом от суммы частичного произведения при сдвиге его вправо на один разряд (микровозможность размещения частного в п-разрядном регистре (микрокоманда ДЗ) схемой 32 (фиг.З). Для этого делимое сдвигается влево на один раз- gg ряд. Содержимое регистра 1 передается через сдвигатель 6 в коммутатор 25, где сдвигается на один разряд влево и записьгоается в регистр 1, а содержимое регистра 24 сдвигается

35

регистрах 1 и 2, делится на п разрядный делитель, записанный в п-разряд- ном регистре 2, при этом получаются п-разрядное частное и п-разрядный остаток.

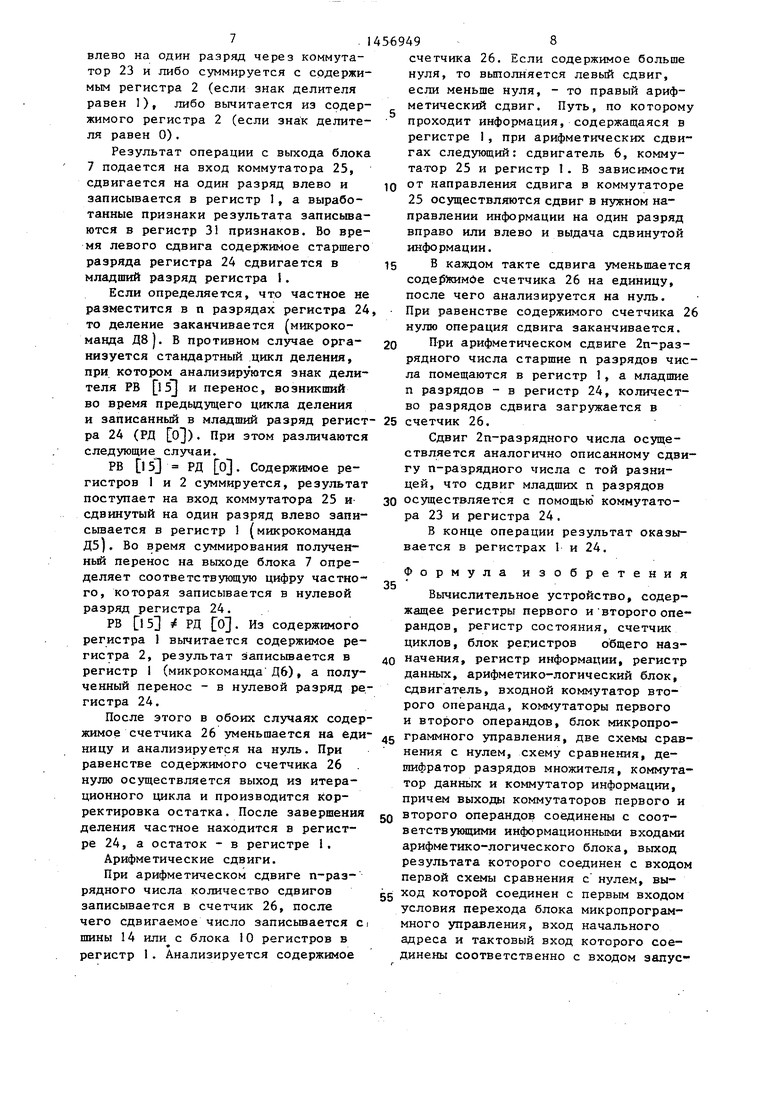

Делимое с шины 14 или с блока 10 принимается в регистры 1 и 24, а делитель принимается в регистр 2, па40 раллельно с этим загружается количество циклов деления в счетчике .26.

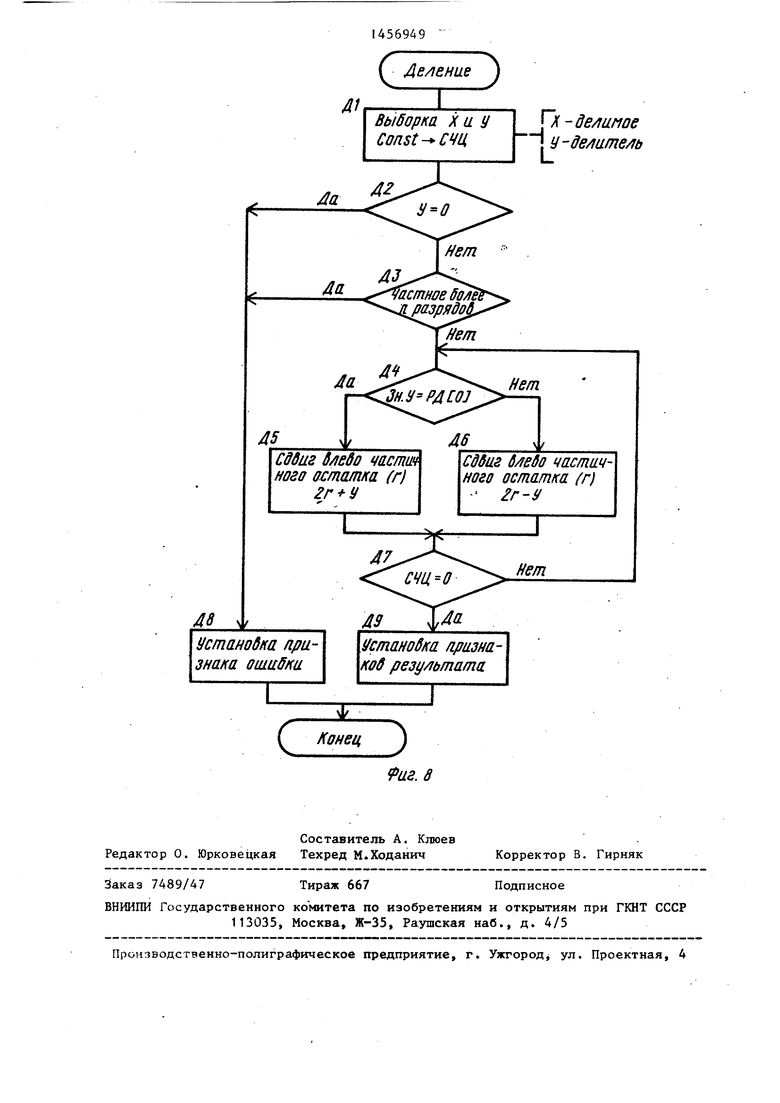

Как видно из алгоритма (фиг.8), после выборки операндов (микрокоманда Д1) осуществляется анализ делите45 ля на нуль (микрокоманда Д2). Если делитель равен нулю, то происходит переход к микрокоманде Ц8, устанавливаются признаки деления на н.уль, и деление заканчивается. Если дели-

возможность размещения частного в п-разрядном регистре (микрокоманда ДЗ) схемой 32 (фиг.З). Для этого делимое сдвигается влево на один раз- gg ряд. Содержимое регистра 1 передается через сдвигатель 6 в коммутатор 25, где сдвигается на один разряд влево и записьгоается в регистр 1, а содержимое регистра 24 сдвигается

влево на один разряд через коммутатор 23 и либо суммируется с содержимым регистра 2 (если знак делителя равен 1), либо вычитается из содержимого регистра 2 (если знак делителя равен 0).

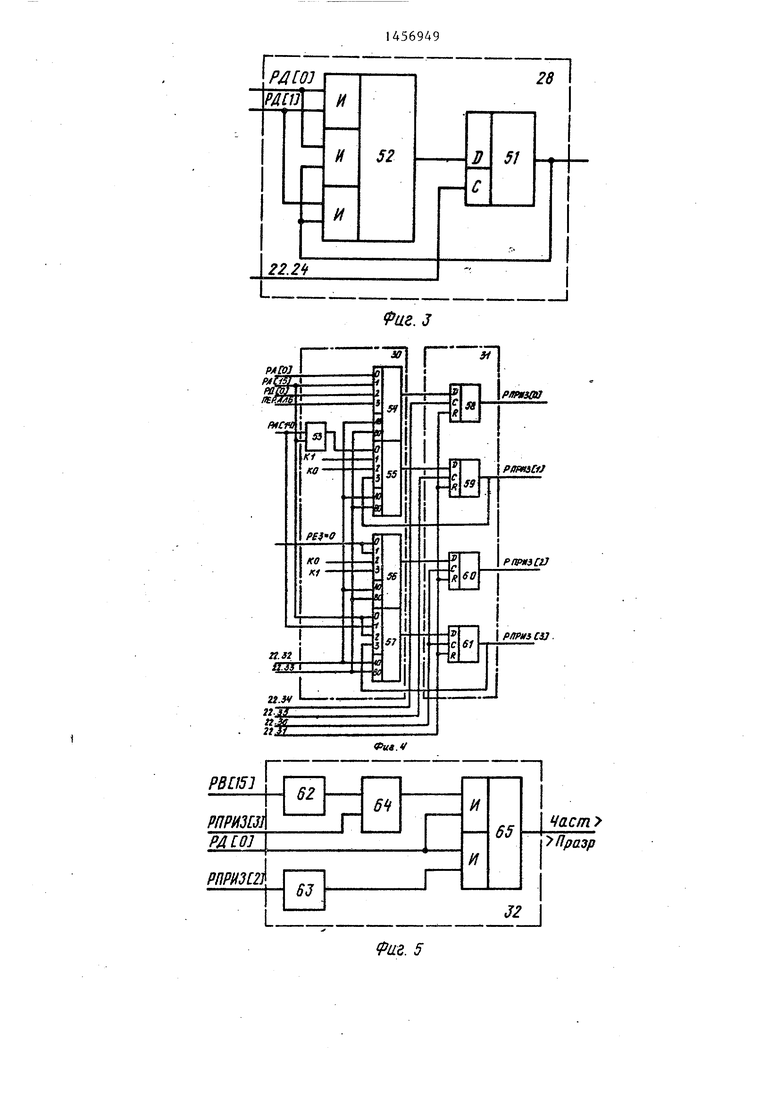

Результат операции с выхода блока 7 подается на вход коммутатора 25, сдвигается на один разряд влево и записывается в регистр 1, а выработанные признаки результата записьюа- ются в регистр 31 признаков. Во время левого сдвига содержимое старшего разряда регистра 24 сдвигается в младший разряд регистра 1.

Если определяется, что частное не разместится в п разрядах регистра 24 то деление заканчивается (микрокоманда Д8). В противном случае организуется стандартный цикл деления, при котором анализируются знак делителя РБ is и перенос, возникший во время предьиущего цикла деления и записанньй в младший разряд регистра 24 (РД о). При этом различаются следующие случаи,

РВ 153 РД о Содержимое регистров 1 и 2 суммируется, результат поступает на вход коммутатора 25 и сдвинутый на один разряд влево запи- сьшается в регистр 1 (микрокоманда Д5). Во время суммирования получен- ньй перенос на выходе блока 7 определяет соответствующую цифру частно- го, которая записывается в нулевой разряд регистра 24.

РВ 15 4 РД о. Из содержимого регистра 1 вычитается содержимое регистра 2, результат записьшается в регистр 1 (микрокоманда Д6), а полученный перенос - в нулевой разряд регистра 24.

После этого в обоих случаях содержимое счетчика 26 уменьшается на единицу и анализируется на нуль. При равенстве содержимого счетчика 26 . нулю осуществляется выход из итерационного цикла и производится корректировка остатка. После завершения деления частное находится в регистре 24, а остаток - в регистре 1. Арифметические сдвиги. При арифметическом сдвиге п-раз- рядного числа количество сдвигов записывается в счетчик 26, после чего сдвигаемое число записьшается Ci шины 14 или с блока 10 регистров в регистр 1. Анализируется содержимое

569498

счетчика 26. Если содержимое больше нуля, то выполняется левый сдвиг, если меньше нуля, - то правый арифметический сдвиг. Путь, по которому проходит информация, содержащаяся в регистре 1, при арифметических сдвигах следующий: сдвигатель 6, коммутатор 25 и регистр 1. В зависимости

10 от направления сдвига в коммутаторе 25 осуществляются сдвиг в нужном направлении информации на один разряд вправо или влево и выдача сдвинутой информации.

15 В каждом такте сдвига уменьшается соде15)кимйе счетчика 26 на единицу, после чего анализируется на нуль. При равенстве содержимого счетчика 26 нулю операция сдвига заканчивается.

20 При арифметическом сдвиге 2п-раз- рядного числа старшие п разрядов числа помещаются в регистр 1, а младшие п разрядов - в регистр 24, количество разрядов сдвига загружается в 25 счетчик 26.

Сдвиг 2п-разрядного числа осзще- ствляется аналогично описанному сдвигу п-разрядного числа с той разницей, что сдвиг младших п разрядов

30 осуществляется с помощью коммутатора 23 и регистра 24.

В конце операции результат оказывается в регистрах 1 и 24.

35

Формула изобретения

Вычислительное устройство, содержащее регистры первого и второго операндов, регистр состояния, счетчик циклов, блок регистров общего наз40 начения, регистр информации, регистр данньпс, арифметико-логический блок, сдвигатель, входной коммутатор второго операнда, коммутаторы первого и второго операндов, блок микропро45 граммного управления, две схемы сравнения с нулем, схему сравнения, дешифратор разрядов множителя, коммутатор данных и коммутатор информации, причем выходы коммутаторов первого и

5Q второго операндов со единены с соответствующими информационными входами арифметико-логического блока, выход результата которого соединен с входом первой схемы сравнения с нулем, вы55 ход которой соединен с первым входом условия перехода блока микропрограммного управления, вход начального адреса и тактовый вход которого соединены соответственно с входом запус91456949 ,10

ка и тактовым входом.устройства, ин-дом разрешения приема регистра дан- формационная шина которого соединенаных, с первым и вторым управляющими с первым информационным входом вход-входами коммутатора информации, с ного коммутатора второго операнда и .входом разрешения приема, суммирую- с выходом регистра информации, выхо-щим и вычитающим входами счетчика ды регистра состояния и регистра пер-циклов, отличающееся тем, вого операнда соединены соответствен что, с целью сокращения аппаратур- но с первым и вторым информационныминых затрат, оно содержит коммутатор входами сдвигателя, выход входного Qпризнаков, регистр признаковой схему коммутатора второго операнда соеди-сравнения с константой, причем выхо- нен с информационным входом регистрады блока регистров общего назначения, второго операнда, выход которого сое-регистра информации и коммутатора ин- динен с информационным входом комму- формации объединены и соединены с ин- татора второго операнда, выход реги- ig формационным входом регистра первого стра первого операнда соединен с ин-операнда, с третьим информационным формационш,1м входом коммутатора пер-входом сдвигателя, выход регистра ин- вого операнда, выходы двз младших .формации соединен с вторым информа- разрядов регистра данных соединеныционным входом входного коммутатора соответственно с входами разрядов де- 2о второго операнда, информационная ши- шифратора разрядов множителя, выходна устройства соединена с первым ин- счетчика циклов соединен .с входомформационным входом регистра инфор- второй схемы сравнения с нулем, вы-мации, выход сдвигателя и выход ре- ход которой соединен с входом условиязультата арифметико-логического бло- перехода блока микропрограммного уп- 25 ка объединены и соединены с информа- равления, третий вход условия перехо-ционными входами регистра состояния, да которого соединен с выходом схемыблока регистров общего назначения и сравнения, первый вход которой соеди-счетчика циклов, с вторым информаци- нен с четвертым входом условия пере-онным входом регистра информации, с хода блока микропрограммного управ- зо первыми информационными входами ком- ления и с выходом старшего разрядамутатора данных и коммутатора ин- регистра второго операцца, выход ком-формации, выход регистра данных сое- мутатора данных соединен с информаци-динен с вторыми информационными вхо- онньш входом регистра данных, выходыдами коммутатора данных и коммутато- с первого по тридцатый блока микро-ра информации, третий информационный программного управления соединены со-вход которого соединен с выходом пар- ответственно с входом разрешения при--вой схемы сравнения с нулем, выходы ,ема регистра состояния, с входом раз-дешифратора разрядов множителя и схе- решения приема, адресными входами смы сравнения с константой соединены первого по четвертый и с входом разре- соответственно с пятым и шестым вхо- шения чтения блока регистров общегодами условия перехода блока микро- назначения, с входами разрешения при-программного управления, седьмой вход ема и чтения регистра информации, сусловия перехода которого соединен с управляющим входом входного коммута-вторым входом схемы сравнения, с пер- тора второго операнда, с входом раз- .вым входом схемы сравнения с конс- решения приема регистра первого операн- -тантой, с первым информационным входом да,с входом разрешения приема регистракоммутатора признаков и с выходом ; второго операнда, с управляющим вхо- :младшего разряда регистра данньк, вы- дом коммутатора первого операнда, сход первой схемы сравнения с нулем управляющим входом коммутатора второ-соединен с вторым информационным вхо- го операнда, с первым и вторым входа-дом коммутатора признаков, выход коми управления функциями сдвигателя,торого соединен с информационным вхо- с входами разрешения чтения сдвигате-дом регистра признаков, выход которо- ля и арифметико-логического блока, сго соединен с восьмым входом условия входами с первого по пятый вида one-перехода блока микропрограммного уп- рации арифметико-логического блока,равления, выходы второго и третьего с управляющим входом коммутатора дан-разрядов регистра признаков соедине- ных, с входом разрешения приема де-ны с вторым входом схемы сравнения шифратора разрядов множителя, с вхо-с константой, третий вход которой со 145694912

единен с выходом старшего разряда ре-ра первого операнда, выходы с тридгистра второго операнда, выход пере-цать первого по тридцать шестой блоноса арифметико-логического блока со-ка микропрограммного управления соеединен с третьим информационным вхо,-динены соответственно с входом надом коммутатора данных и с третьимчаль«ой установки регистра признаков,

информационным входом коммутаторас первым и вторым управляющими входапризнаков, четвертый, пятый и шестойми коммутатора признаков, с входами

информационные входы которого соеди-разрешения приема нулевого, первого,

иены соответственно с выходами млад- Qвторого и третьего разрядов регистра

шего и .двух старших разрядов регист-признаков.

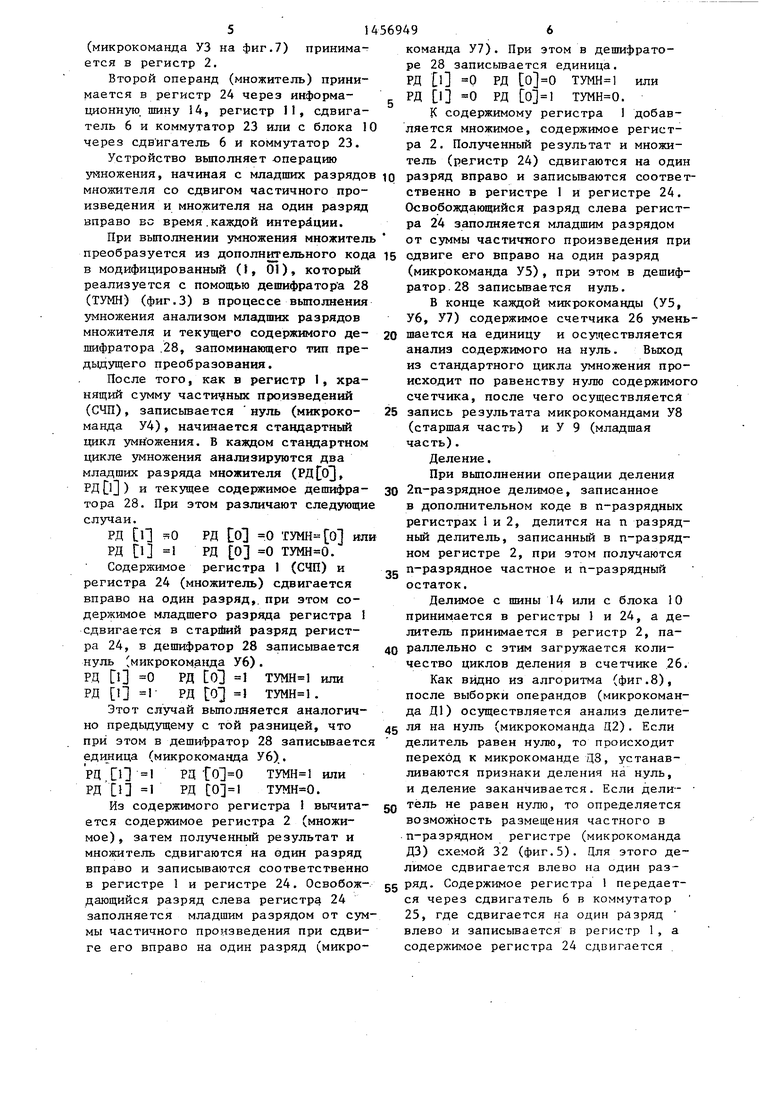

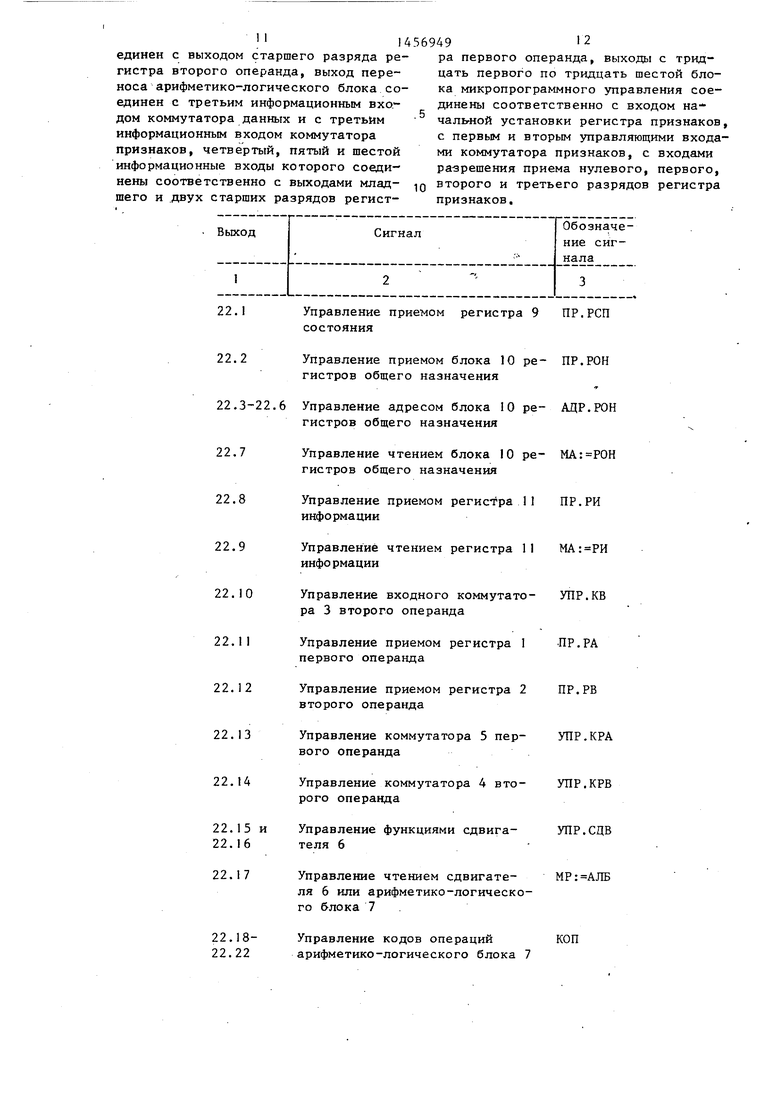

Управление приемом регистра 9 ПР.РСП состояния

Управление приемом блока 10 ре- ПР.РОН гистров общего назначения

.6 Управление адресом блока 10 ре- АДР.ГОН гистров общего назначения

Управление чтением блока 10 ре- гистров общего назначения

Управление приемом регистра 11 ПР.РИ информации

Управление чтением регистра 11 инфо рмации

Управление входного коммутато- УПР.KB pa 3 второго операнда

Управление приемом регистра 1 ПР.РА первого операнда

Управление приемом регистра 2 ПР.РВ второго операнда

Управление коммутатора 5 пер- УПР.КРА вого операнда

Управление коммутатора 4 вто- УПР.КРВ рого операнда

Управление функциями сдвига-УПР.СДВ

теля 6

Управление чтением сдвигате- ля 6 или арифметико-логического блока 7 .

Управление кодов операций КОП арифметико-логического блока 7

Управление приемом счетчика 26

цикловПР.СЧЦ

Управление содержимогоСЧЦ- - счетчика 26 циклов

Управление -1 содержимогоC lu-l . счетчика 26 циклов

Управление начальной установкой НАЧ.УСТ регистра 31 признаков

Управление коммутатора 30 при- УПР.КПРИЗ

знаков

Управление приемом нулевогоПР.С разряда регистра 31 признаков

Управление приемом первогоПР.У разряда регистра 31 признаков

Управление приемом второго иnP.Z,N третьего разрядов регистра 31 признаков

РДШ

РЛШ

и

и

28

52

51

.J

Риг. 5

Сдвиг 8/1Ебо час тин- ног в остатка (г) 2Г + У

48

Установка признака ошибка

С

Конец

Состгшитель А. Клюев Редактор 0. Юрковецкая Техред М.Ходанич

Заказ 7489/47

Тираж 667

ВНИИПИ Государственного ко митета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Г 4е/}ение j

J(-de/iuiioe У-де/fame/fif

47

Нет

43

Истанодка / азна- ков резу/ibmama.

f aa.d

Корректор В. Гирняк

Подписное

Авторы

Даты

1989-02-07—Публикация

1987-04-07—Подача