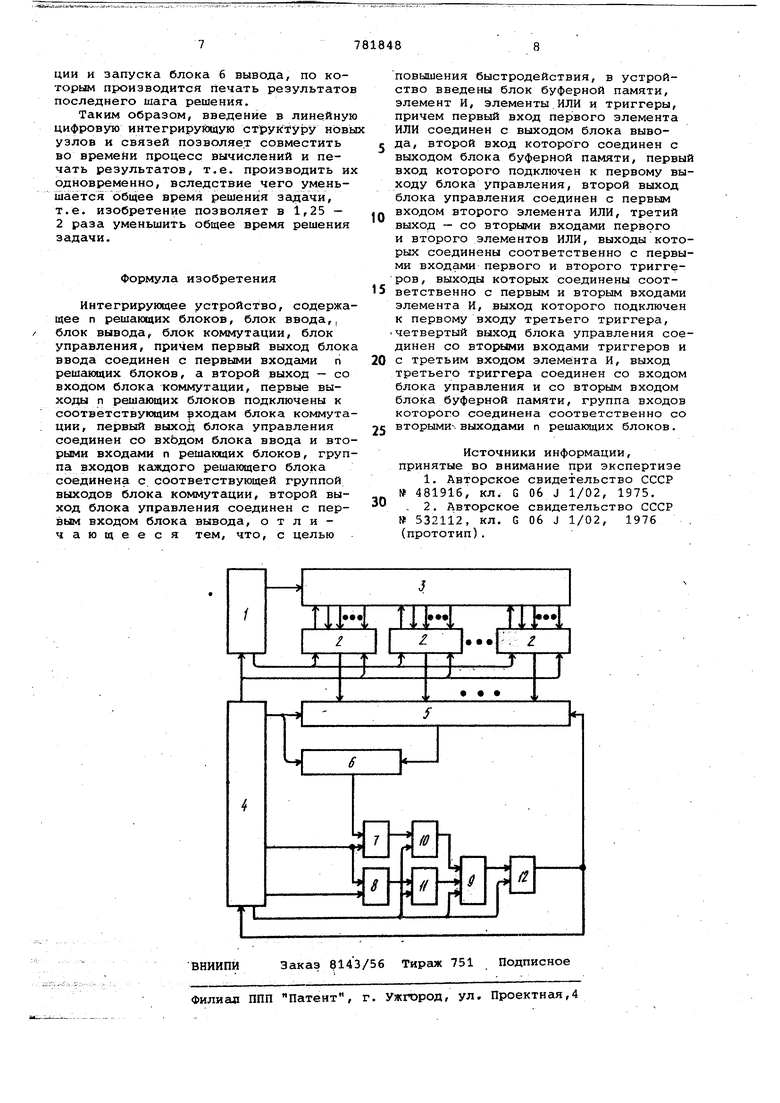

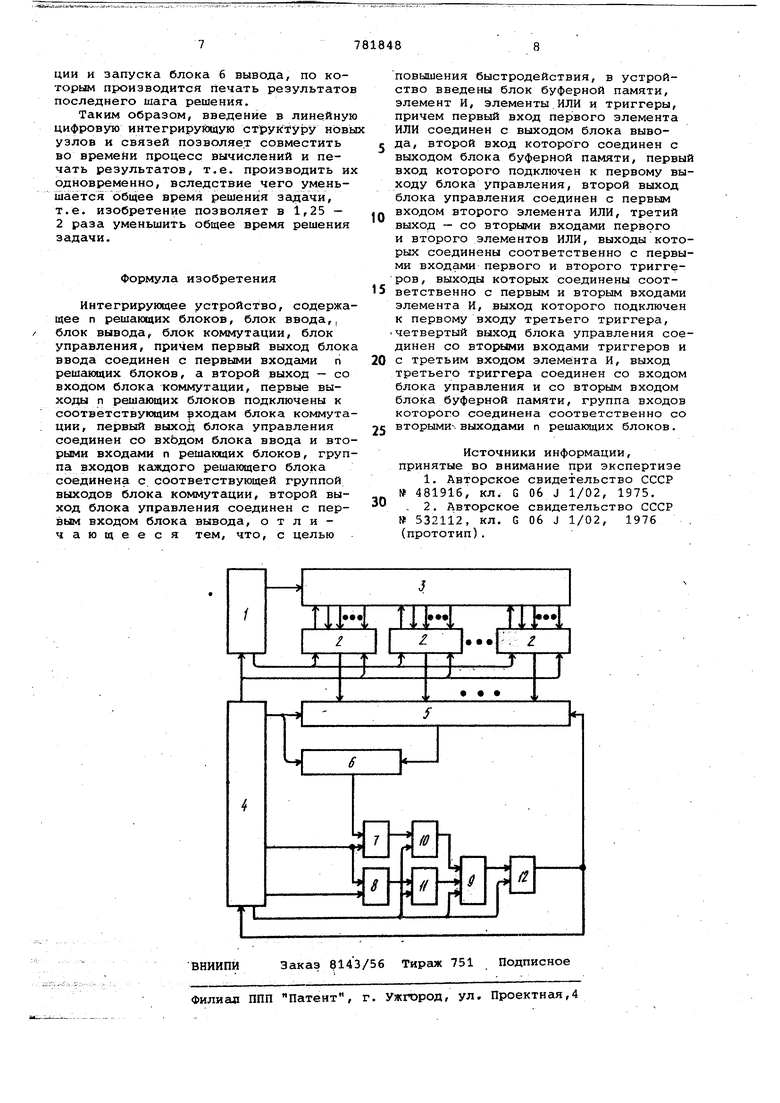

щих блоков, блок ввода, блок вывода, блок коммутации, блок управления, причем первый выход блока ввода соединен с первыми входами h решающих .блоков, а второй выход - со-входом блока коммутации, первые выходы п решающих блоков подключены к соответ ствующим входам блока коммутации, первый выход блока управления соединен со входом блока ввода и вторыми входами п решающих блоков, группа вх дов каждого решающего блока соедине,на с соответствующей группой выходов блока коммутации, второй выход блока управления соединен с первым входом блока вывода, введены блок буферной памяти, элемент И, элементы ИЛИ и три геры, причем первый вход первого эле мента ИЛИ соединен свыходом блока вывода, второй вход которого соедине с выходом блока буферной памяти, пер вый вход которого подключен к первом выходу блока управления, второй выхо блока управления соединен с первым входом второго элемента ИЛИ, третий выход - со вторыми входами первого и второго элементов ИЛИ, выходы кото рых соединены соответственно с первы ми входами первого и второго триггеров, выходы которых соединены соотве ственно с первым и вторым входами эл мента Ир выход которого подключен к первому входу третьего триггераj чет вертый выход блока управления соединен со вторыми входами триггеров и с третзьим входом элемента И, выход тре его триггера соединен со входом блок управления и со вторым входом блока буферной памяти, группа входов которого соединена соответственно со вто рыми выходами п решающих блоков.На чертеже представлена блок-схем устройства. . Устройство содержит блок 1 ввода, решающие блоки 2, блок 3 коммутации, блок 4 управления, блок 5 буферной памяти, блок 6 вывода, элементы ИЛИ и 8,-элемент И 9, триггеры 10-12. Решение задач осуществляется приближенными методами численного интегрирования. Результаты решения получгиотся в виде числовых значений иско мых величин через равные интервалы времени, определяемые заранее выбран ным шагом решения. Решаемая задача представляется в виде симметричной формы уравнений Шеннона.N-- 1 - А, -- . - % Э-А dZn Ypj: dz . dx;v Yfnt. (XQ) Ypitu; k - 2..3,. . . ..N,

781848 где и Ayvj (j I ,2,3, . . . ,N) являются постоянными коэффициентами, принимающими значения О или 1 в зависимостй От решаемой задачи . Прямоугольные матрицы, составленные из коэффициентов и .-, вместе с вектором начальныхусловий Yp. (k t ,2 , . . . ,N) полностью задают программу решения задачи. На входы решающих блоков информация подается в виде приращений подынтегральной функции и переменной интегрирования. Решающий блок оперирует с одноразрядными : приращениями и выполняет следующие операции - цифровое интегрирование, суммирование приращений, функцию знака, ограничение, слежение. Перед надтЬойкой структуры нарешение задачи и выполнением процесса решения производится установка в нулевое положение блока 1 ввода, решающих блоков 2 и блока 3 коммутации, блока 5 буферной памяти, блока 6 вывода и трех триггеров 10-12 подачей соответствующих сигналов с блока 4 управления . Настройка структуры на решение задачи производится как вручную с помощью блока 4 управления, так и ав;томатйческй с помощью блока 1 ввода. При настройке структуры вручную с помощью блрка 4 управления выполняется следующая последовательность операций. В блоке 4 управления вырабатывается сигнал адреса решающего блока, который поступает на второй вход настраиваемого решающего блока 2. Одновременно с сигналом адреса решающего блока поступает код операции и начальные данные. Код операции включает в себя операции цифрового интегрирования, суммирования приращений, функцию знака, ограничение, слежение и признак печати, который необходим для вывода информации из решающего блока на печать. Адрес решакицего блока поступает также в блок 1 ввода и с выхода последнего по первой группе входов поступает на соответствующие .входы коммутирующих 3ijriej eHTpB блока 3 коммутации. Далее в блоке 4 управления вырабатывается сигнал адреса столбца коммутирующего элемента блока коммутации, который поступает в блок 1 ввода и с выхода последнего по первой группе входов поступает на соответствукяцие входы коммутирующих элементов блока 3 коммутации. Затем в блоке 4 управления вырабатывается сигнал гщреса строки крммутирукице го элемента, который поступает на блок 1 ввода и с выхода последнего по первой группе входов поступает на соответствующие входы коммутирукхДй й: ;эл ементов блока 3 коммутации. При совпадений сигналов адреса решающего блока, адреса столбца и адрбса строки, определенный коммутирующий элемент блока 3 коммутации настраивается на пропускание выходных прираще ний, поступающих на него с первого выхода соответствующего,решающего блок на один из входов тгервой группы входо соответствующего решающего блока 2. После настройки данного решающего блока 2 блок 1 ввода устанавливается в исходное состояние сигналом, посту пающим из блока 4 управления. Затем производится настройка последующих решающих блоков 2 и коммутирующих элементов блока 3 коммутации. При настройке устройства на решени задачи в Автоматическом режиме из блока 4 управления в блок 1 ввода по ступает сигнал начала настройки. Из блока 1 в соответствующие решающие блоки 2 и коммутирующие элементы бло ка 3 коммутаций поступают сигналы настройки в той же последовательности, что и при ручном режиме. .. Решение задачи осуществляется сле дующим образом. в блоке 4 управления задается необходимое количество итераций, в течение которых вычисляется точка решения, т.е. задается шаг решения, и необходимое число точек решения. Затем блок.4 управления вырабатывает команду пуска, которая с третьего выхода блока 4 через элементы ИЛИ 7 и ИЛИ 8 поступает на единичные входы триггеров 10 .и 11. Триггеры 10 и 11 устанавливаются в единичное состояние и обеспечивают прохождение с пятого выхода блока 4 через элемент И 9 временного импульса, соответствующего началу итерации, в результате чего триггер 12 устанавливается в единичное состояние и начинает вырабатыват сигнал записи информации, который поступает на второй вход блока 5 буферно памяти и на вход блока 4 управления. По этому сигналу информация из тех решающих блоков 2, в код операции которых при настройке занесен признак печати, записывается в блок 5 буферной памяти. Временным импульсом соответствующим концу итерации и поступающим на нулевой вход триггера 12 этот триггер устанавливается в нулевое состояние и выработка длительностью одной итерации сигнала записи информации прекращается. По окойчания этого сигнала блок 4 управления вырабатывает одновременно следующие сигналы - сигнал,разрешсиощий решение задачи, который поступает в решающие блоки 2, сигнал считывания информации который поступает на вход блока 5 буферной памяти, команда запуска блока вывода, которая поступает на вход бло ка 6 вывода и импульс сброса, которыК поступает на нулевые входы триггеров 10 и 11 и устанавливает их в нулевое состояние. По сигналу считывания информации из блока 5 буферной памяти поступает на второй вход блока 6 вывода и произ.водится печать начальных данных. Одновременно в решающих блоках 2 производится вычисление первой точки решения, при , этом обмен вспомогательной информацией между решающими блоками 2 в процессе вычислений производится через блок 3 коммутации. После отработки заданного количества итераций, т.е. заданного шага решения, блок 4 управления вырабатывает сигнал останова, который останавливает процесс решения,и, поступая с четвертого выхода блока 4 через элемент ИЛИ 8 на единичный вход триггера 11, устанавливает его в единичное состояние. Блок 6 вывода после окончания печати начальных данных вырабатывает сигнал окончания печати, который поступает через элемент ИЛИ 7 на единичный вход триггера 10 и устанавливает его в единичное состояние, а после установки триггеров 10 и 11 в единичное состояние триггер 12 с приходом временного импульса, соответствующего началу итерации, начинает выработку сигнсша записи информации. При этом, если время выполнен я одного шага решения оказывается больше времени печати результатов, то сигнал окончания печати приходит раньше сигнала останова и лишь только после прихода сигнала останова оба триггера 10 и 11 оказываются в единичном состоянии и триггер 12 начинает вырабатывать сигнал записи информации, а далее выработка всех остальньрс управляющих сигналов, а также одновременно решение задачи и печать результатов предыдущей точки решения повторяются. Если же время выполнения одного шага решения оказывается меньше времени печати результатов, то сигнал останова приходит раньше сигнала окончания печати. В этом случае лишь только после прихода сигнала окончания печати оба триггера 10 и 11 оказываются в единичном состоянии и триггер 12 начинает вырабатывать сигнал записи информации, и далее выработка всех остальных управляющих сигналов и одновременное решение задачи и печать результатов, вычисленных в предьщущем шаге, повторяются. После отработки необходимого количества точек решения блок 4 управления вырабатывает сигнал окончания решения, который с четвертого выхода блока 4 поступает на единичный вход триггера 11. По приходу сигнала окончания печати из блока 6 вывода на , единичный вход триггера 10 вырабатывается сигнал записи информации, по коtopoMy результаты последнего шага ре(юния записываются из решающих блоков 2 в блок 5 буферной памяти.,По окончании этого сигнала блок 4 вырабатывает сигналы считывания информации и запуска блока 6 вывода, по которым производится печать результато последнего шага решения. Таким образом, введение в линейну цифровую интегрирующую структуру нов узлов и связей позволяет совместить во времейи процесс вычислений и печать результатов, т.е. производить и одновременно, вследствие чего уменьшается общее время решения задачи, т.е. изобретение позволяет в 1,25 - 2 раза уменьшить общее время решения задачи. Формула изобретения Интегрирующее устройство, содержа щее п решающих блоков, блок ввода,, блок вывода, блок коммутации, блок управления, причем первый выход блок ввода соединен с первыми входами п решающих блоков, а второй выход - со входом блока коммутации, первые выходы п решающих блоков подключены к соответствующим уходам блока коммута ции, первый выход блока управления соединен со вхЬдом блока ввода и вто рыми входами п решающих блоков, груп па входов Кс1ждого решающего блока соединена с соответствующей группой выходов блока коммутации, второй выход блока управления соединен с первым входом блока вывода, отличающееся тем, что, с целью повышения быстродействия, в устройство введены блок буферной памяти, элемент И, элементы ИЛИ и триггеры, причем первый вход первого элемента ИЛИ соединен с выходом блока вывода, второй вход которого соединен с выходом блока буферной памяти, первый вход которого подключен к первому выходу блока управления, второй выход блока управления соединен с первым входом второго элемента ИЛИ, третий выход - со вторыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первыми входами первого и второго триггеров , выходы которых соединены соответственно с первым и BTopfcJM входами элемента И, выход которого подключен к первому входу третьего триггера, четвертый выход блока управления соединен со вторыми входами триггеров и с третьим входом элемента И, выход третьего триггера соединен со входом блока управления и со вторым входом блока буферной памяти, группа входов которого соединена соответственно со вторыми-, выходами п решающих блоков. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 481916, кл. G Об J 1/02, 1975. . 2. Авторское свидетельство СССР 532112, кл. G Об J 1/02, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Устройство управления цифровойиНТЕгРиРующЕй СТРуКТуРы | 1979 |

|

SU813429A1 |

| Цифровая интегрирующая структура | 1978 |

|

SU680001A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Линейная цифровая интегрирующая структура | 1974 |

|

SU532112A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Электронная клавишная вычислительная машина | 1982 |

|

SU1068945A1 |

| Устройство управления цифровой интегрирующей структуры | 1978 |

|

SU789993A1 |

| Устройство для сопряжения однородной вычислительной системы | 1980 |

|

SU951287A2 |

Авторы

Даты

1980-11-23—Публикация

1978-04-10—Подача