Изобретение относится к области вычислителиной техники и прадназначено для решения |СИ:стем лиией.ных и нелинейных дифференциальных и алгебраических уравнений, задач уцравлелия объекта.ми, (Вычисления сложных функций я интегралов, моделирования динамических систем и Т|раектор1ных расчетов..

Известны цифровые спецнализировавные устройства 1 для решеиия систем дифференциальных уравнений, выполненные на основе цифровых MHTerparoipOB.

OiCHOBHbiM :кедостат1ком известных устроЙ1Ств является то, что они или a-ie могут быть автоматически настроены на решение, или процесс подготовки их к решению занимает значительное время.

Наиболее близким техническим решением к данному изобретению является цифровая интегрирующая машина 2, содержаш;ая решающие блоки, блок В1вода, блок вывода, блок набора, блок управления, .причем 1выход блока набора соединен с груплой входов каждого решающего блока, а вход блока набора соединен с первым выходо.м 1каждого решаюшего блока, нервый выход блока ввода соединен с персым входом каждого решающего блока, первый выход блока управления соеди1нс:н со зходо.м блока ввода и вторым входом каждого решаюшего блока, а вход блока

упра1влен ш соединен со вторым выходом каждого решаюш,его блока и с пер;вым входом ;блока вывода, зторой вход которого соединен со вторым 1выходом блока управления.

Основным недостатком известной цифровой интегрирующей машины является то, что прежде чем начать решение необходимо на блоке набора вручную набрать структурн.ую схему задачи, что занимает очень много времени но сравнению со временем решения.

Целью изобретения является 1нозышей;ие быстродействия и расширение фЗШчниональных возможностей линейной цифровой лнтегрнруюшей структуры.

Это достигается тем, что в линейную цифровую интегртфующую структуру введен л.ополнитель:-10 блок ком1мутацни, первая груьна входов которого coe.iHiiena ео вторым выходом блока .ввода, каждый вход второй гр лпы входов блока коммутацпн соединен с п-овым выходом соответствующего решаюпг О блока, первая группа входов каждого pei юш,его блока соединена с соответ.:т:зую11 грунпои выходов блока коммутацнн.

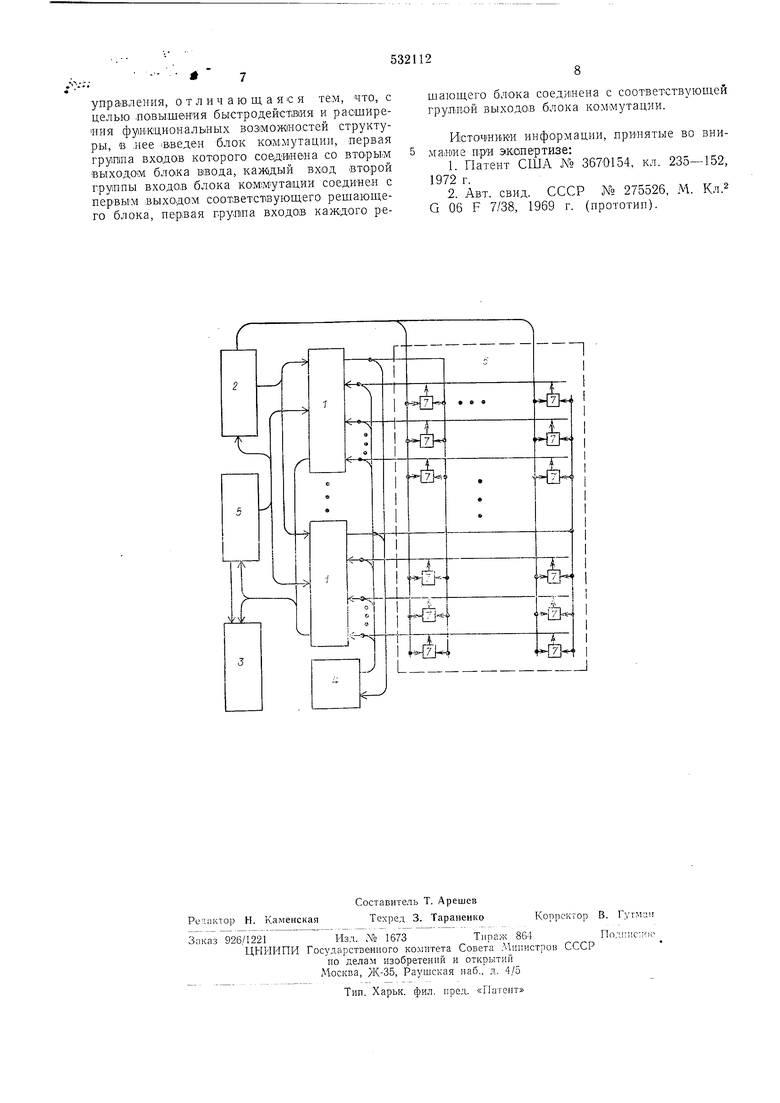

На чертеже представлена функг.. Ная схе.ма нред.тагаомой линейной цифре1ИП тегр11руюш,ей структуры.

Линейная цнфрсзая интегрирующая стПКтура содержит решающие блоки /, блок 2 ввода, блок 3 вывод;;, блок 4 набора, блок 5 уП:ра.К.ЛС:Н: Я, блО.К 6 КОММуТЗЦНИ, СОСТОЯЩИЙ из liiafiopa КО.ммутирующих эле.ментс-.з 7. РешвКие задач -на 1стру.ктуре осуществляется приближанными методал1и численного И1нтстри1р01ва1ння. Результаты решения получаются в виде числовых значений IIICKOMHX величин, через равные интервалы, определяемые 1ма.ш.июной .независимой иеременной. Решаемая задача представляется в виде симметричной формы уравиений Шенлона.

dY,,, S A,,jdZi,

; 1 ;V

Mi,

dr.. gki

dZ; - Y,,dY,,,, dZ, - d-c,

Y.,;4X,:) Y,,o, .3 /V,

где л,.,; и A,,:(..., N, ,2...,N) Являются постоянными коэффициента ми, принимающими значения О или 1 в зав1исимости от |решаемой задачи. Пря.моугольные матрицы, со став лепные из козф,фицлс1ггсв Ai,:,i и А:7й;, вместе с вектором «ачалыиых условий Кр,,о (/(1,2 Л), полиостью задают программу решения задачи. На входы рещающих блоков информация подается в виде прпращспий подьштегральпой функции и переменной интегрирования. :В ослюву псстроепия решающего блока линейной однородной цифровой интегрирующей структуры положена разностно-квантованная система уравнений решающего блока, оперирующего с одноразрядными приращениями a-i выполняющего операции: -цифрового интегриро;ва1ння; -суммирования приращений; -функцию знака; -ограничение. V pO+i) S Лр/ уУу(/+1) Д 7Z// , ,3,..., n лк„ P( + I) Ypi +F/,(), Yp(x,) - Ypn, У i v7 V i/ -Г V i, VZ(/.i,i) Ypi: Я ii d

i 1 - r n 1Л v i ГТ n f V 1

„.,.,„, ) т 1 . если O.gll J iU : ,

(, если Sign 7;.-.,, o iV{vi)l j S., ,-1 i Zf/ir, I Oz;| AZ ( Z RJ 2 :tAl SiffnVl2-„ у - s -- -i-- л 7 i::. l A,Z Z(;4-i).)gj,r..,, 1 ,, 7 . V - /(-r)i //1 ч ign V,(,,.,, -, если У/;(/м)0 ---„- -KBaHTOBaiHHoe злачение приращс..йй интеграла; - KiBaiHTOiBaiHHoe значетще .приращений независиЛЮЙ -переменной; 7/.(/+ij -.к,в2 :1- 0занксе зна:е--1ие подылтегральиой функции;S:,:: + n остаток итгеграл; / - сс1но-зан есистемы счисления; - фу1;;,к.ция .рясчлслс;:; ; Sign И I - функция злаха; Я„ - коэффицкеит передачи обратной сзяз.и; - функция огра«1чсч::я; , „Р, „S, „L -условные Сбоз гаче: ; Я работы решающего блока структуры, сэот1зетст1ВенгЮ, в реж.;;л;ах |цифр01вого иятегрирования, суммирования, функции знака и функции ограничения. Перед «астройкой структуры на решение ачи и выполнением ироцесса решения проодится устаяоака в нулевое положение реющих блокО|В 1 и блока 6 коммутации, бло2 ввода, блока 3 вывода нодачей соответющих сигналов с блока 5 упразления. Настройка 1стру1ктуры на решение задачи ет ироизводиться как вруч.ную с .помощью ка 5 управления, так и автоматически с ощью блока 2 ввода. ри настройке структуры с помощью бло5 уиравления выиол1няется следую:ц ;л подовательность операций.

В блоке 5 уп.равлония вырабатывается сипнал адреса решающего бло.ка, который поступает .на третий вход л-1а:странваемого -решающего блока. ОдноВ ремешю с сипналом выбора ад.реса .решающего блОКа поступает код о псращи.и и начальные да1нныо. Код операции включает в себя операции цифроаого ийтегриро.чания, сум:миравания приращсяий, фук-кцию зг;а,ка, ограяичения .и ириэнак печати, который необходим для вывода информации из решающего блока на течать.

Адрес рещающето блока поступает также в блок 2 азода и с выхода последнего по первой грушпе входов поступает на соответствующие входы коммутирующих элементов 7 блока 6 коМ.мутации.

Далее з блоке 5 у::ра1вле«ия вырабатывается Сигггал адреса столбца колт мутирующего элемента 7, который .поступает на блок 2 ввода и с выхода последнего по первой грунте входов поступает на соответствующие входы коммути.рующих элементов 7 блока 6 коммутации.

Затем в блоке 5 управления вырабатывается сигнал адреса стро.кн .коммутирующего элемента 7, который поступает на блок 2 ввода и с выхода последнего по первой группе входов поступает на соответствующие входы ,мутирующих эле;ментов 7 блока 6 коммутации.

Прн совнаде.1гии сигналов адреса решающего блока, адреса столбла и адреса строки, о-пределе.нный коммутирующий элемент 7 блока 6 коммутаиии настраивается «а пропуска«и.:: выходных пр11:раще} ий, :постунаюц их На него с iHOpiBoro выхода соответствующего решаю-щего блока / на один из входов п.ервой грунны соответствующего решающего блока.

После настройки данного рещаюж1;его блока /, блок 2 ввода устанавливается в исходнос состоя.ние сигналом, поступающим из блока 5 ун-равлення.

Затем .производится настройка лоследующнх решающих блоков / и ком.мутирующнх элементов 7 блока 6 ком.мутации.

При настройке структуры на решение задачи в автоматическом режн.ме из блока 5 управления в блок 2 ввода поступает сигнал начала настройки. Из блоха 2 ,в соответствующие рещающие блоки / и коммутирующие элементы 7 блока 6 ком мутации поступают сигналы настройки в той же последовательности, что и цри ручном .режиме.

Решение задачи осуществляетх;я также в двух режимах: ручном н автО:матическом.

iB ручном режиме останов решения производится оператором.

При это.м в блоке 5 управления вырабатывается сигнал сста:1С-:;а, который поступает )В блок 3 вывода, подготавливая его к работе, и 1П.Э Т50ТЬ:,М входу в каждый сешающий блок 1.

При налгчкп призттака печати в коде операилги, который за;;;ооится в решающий блок 1 при настройке, информация из решающего

блока / по второму выходу поступает в блок 5 .вывода и происходит печать результата реш .зн.и я.

iB автоматическом режиме в блоке 5 управления задается с-геобходи.мое .количество итераций, в течение которых вычисляется точка .решения, а также необходимое число точек решения. После отработки заданного количества итераций, бло-к 5 управления вырабатывает сигнал останова, который поступает в блок 3 , подготавливая его к работе и по третьему входу - в каждый решаюший блок.

При признака печати в коде операции :.;:: форма1Л1я из решающего бло.ка 1 по BTOpONy выходу .поступает в блок 3 вывода и происходит печать точки рещения, носле чего решение продолжается. После отработки необходимого количества точек решения, устройство 5 управления вырабатывает сигнал око.нчания решения.

Пслользо1вание в цифровой интегрирующей структуре блока 1-;оммутации и НОВых связей приводит к тому, что в структ фе етановится возможна полная автоматизация процесса настройки и ввода исходных да.нных и кода операции, во много раз уме.н.ьшается время настройки и повышается коэффициент 11; пользоза1:ия цифровой интегрирующей структуры.

Кроме того, цифровая интегрирующая структура с блоко коммутации обладает снособностью к перестройке програл-шы. рещения задачи в процессе работы, возможностью .полной автоматз зацни процесса подготовки задачи к решению .и настройки за счет создания пюридного .вычислительного комплекса цифровая вычислительная машина - цнфровая интегрирующая структура, новышенной надежноетью и возможностью продолжать работу при выходе нз строя ка-к некоторого количества решаюнхих блоков, так и отдельных .коммутируюшнх элементов б,тока коммутацни.

Все это нрнводит к расшгрению фугкциональных возможностей н повышению быстродействия цифровой интегрирующей структуры.

Формула изобретения

Линейная цифровая ннтегр1 рующая структура, содержащая решающне блоки, блок ввода, блок .вы1вода, блок набора, блок управления, причем выход блока набора соединен с груп.ной вхо.дов каждого решающего блока, а вход блока 1 аборп соединен с первым выходО|М каждого решаюи.сго блока, первый выход блока в.да соед-глс с первым входом каждого ре цаюн;сго блска. 1;.:рвый выход блока . сост,:::; СЛ входом блока лвода и вторым входом решающего блока, а зхот, бюка . еоедннен со вторым выходом кяжл о i L;;;aioHj,ero блока и с первым вхэдсм блс1-:а вывода, второй вход которого соединен со зтопь : выходом блока

управления, отличающаяся тем, что, с целью ловышедаия быстродействия и расширения функциональных возможностей структуры, в лее |В|веден блок коммутации, первая группа входов которого соединена со вто.рЫ|М выходом блока ввода, каждый вход группы входов блока коммутации соедияен с перВЫМ выходом соответствующего решающего блока, первая груопа входов каждого решающего блока соединена с соответсгвуюшей группой выходов блока коммутации.

Источники информации, принятые во внимаипе при экопертизе:

1.Патент США 3670154, кл. 235-152, 1972 г.

2.Авт. свид. СССР Яд 275526, М. Кл. G 06 F 7/38, 1969 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая интегрирующая структура | 1978 |

|

SU680001A1 |

| Устройство для ввода информации | 1973 |

|

SU485442A1 |

| Интегрирующее устройство | 1978 |

|

SU781848A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Вычислительная система для решения дифференциальных уравнений | 1975 |

|

SU620980A1 |

| Цифровая интегрирующая машина | 1974 |

|

SU578644A1 |

| Устройство для выфода данных цифровой интегрирующей структуры | 1974 |

|

SU506849A1 |

| Цифровая интегрирующая структура | 1973 |

|

SU481916A1 |

| Устройство сопряжения интегрирующей машины с цифровой вычислительной машиной | 1974 |

|

SU599273A1 |

Авторы

Даты

1976-10-15—Публикация

1974-05-12—Подача