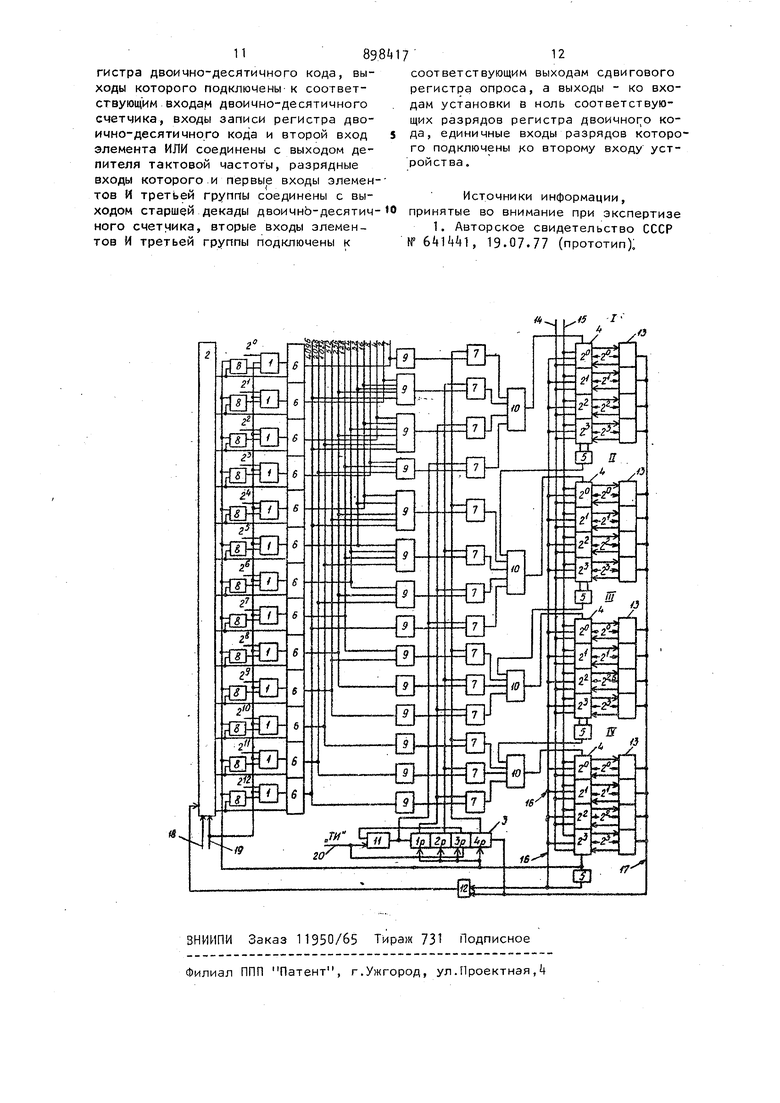

Изобретение относится к вычислительной технике и может быть использовано в различных системах автоматики, цифровых вычислительных устройствах. По основному авт. св. № известно устройство для преобразования двоичного кода в двоично-десятичный, содержащее регистр двоичного кода, сдвиговый регистр опроса, делитель тактовой частоты, двоично-десятичный СЧИТЧИК, элементы задержки, первые и втйрые группы элементов И и ИЛИ, элемент И 13, Однако известное устройство не позволяет осуществить преобразование двоично-десятичного кода в двоичный. Цель изобретения - расширение клас са решаемых задач за счет осуществления обратного преобразования. Указанная цель достигается тем, что в устройство введены третья группы элементов И, регистр двоично-десятичного кода и элемент ИЛИ, один вход которого подключен к разрядным входам записи двоично-десятичного счетчика и через элемент задержки к выходу его старшей декады, разрядные вхо ды сложения и вычитания которого подключены соответственно ко входам прямого и обратного преобразования устройства а разрядные выходы соединены с соответствующими входами регист ра двоично-десятичного кода, выходы которого подключены к соответствующим входам двоично-десятичного счетчика, входы записи регистра двоичнодесятичного кода и второй вход элемента ИЛИ соединены с выходом делителя тактовой частоты, разрядные вхо ды которого и первые входы элементов И третьей группы соединены с выходом старшей декады двоично-десятичного счетчика, вторые входы элементов И третьей группы подключены .к соответствующим выходам сдвигового регистра опроса, а выходы - ко входам устанбвки в ноль соответствующих разрядов 3 регистра двоичного кода, единичные входы разрядов которого подключены ко второму входу устройства. На чертеже представлена схема уст ройства для преобразования двоичного кода в двоично-десятичный. Схема содержит регистр 1 двоичного кода, сдвиговый регистр 2 опроса, делитель 3 тактовой частоты, двоично-десятичный счетчик 4, Элементы 5 задержки, первая, вторая и третья группы 6, 7 и 8 элементов И, первая и вторая 9 и 10 группы элементов ИЛИ элемент И 11, элемент ИЛИ 12, регистр 13 двоично-десятичного кода, входы 14 и 15 прямого и обратного пр образования устройства, разрядные вх ды 16 записи двоично-десятичного сче чика, входы 17. записи регистра двоично-десятичного кода, первый и второй входы 18 и 19 устройства, вход 20 fактовых импульсов делителя частоты. Для Преобразования двоичного кода в двоично-десятичный преобразуемый код введен в регистр 1 двоичного кода. На вход 14 подан сигнал Преоб разование двоичного кода в двоичнодесятичный. По сигналу Пуск-1, пришедшему на вход 18 преобразователя в крайний разряд регистра 2 опроса записывается единица, которая по сигналам Сдвиг, идущим с выхода делителя 3 частоты на вход регистра опроса через элемент ИЛИ 12, последовательно проходит разряды регистра 2 опроса и тем самым, начиная со старшего разряда, разрешает опрос каждого разряда регистра 1 двоичного кода через элементы И первой группы 6. Каждый разряд регистра 1 двоичного кода через элементы И первой группы б в соответствии со своим весом разведен по входам элементов ИЛИ первой группы 9. Элементы ИЛИ первой группы 9 преобразуют весовое значение опрашиваемого разряда регистра 1 двоичного кода в эквивалентный ему двоичнодесятичный код. Элементы ИЛИ первой группы 9 где вес каждой схемы равен весу соответствующего разряда двоично-десятичного кода 8-4-2-1, составляют тетрады, где вес каждой из которых равен весу, соответствующему десятич ному разряду, и количество которых равно числу эквивалентных десятичных 74 разрядов, содержащихся в опрашиваемом разряде двоичного кода. Далее двоично-десятичный код, эквивалентный опрашиваемому разряду регистра 1 -двоичного кода, полученный на выходах элементов ИЛИ первой группы Э, поступает на первые входы элементов И второй группы 7 на вторые входы которых поступают соответствующие серии импульсов 8-4-2-1 полученные соответственно с выхода элемента И 11 и выходов 1-ого, 2-ого и 4-ого разрядов делителя частоты 3. На выходах элементов И второй группы 7 появляется параллельный унитарный код, эквивалентный двоичнодесятичному коду, поданному на входы элементов 7 с выходов элементов ИЛИ первой группы 9. Элементы ИЛИ второй группы 10 преобразуют параллельный унитарный код соответствующих тетрад совместно с сигналами переносов, поступающих с элементов задержек 5. в полный последовательный унитарный код этих тетрад. Полные последовательные унитарные коды тетрад с выходов элементов ИЛИ второй группы 10 поступают параллельно на входы декад двоично-десятичного счетчика 4 соответственно единиц 1, десятков II, сотен I И , тысяч {V. Счетчик 4 в соответствии с сигналом, поданным на вход 14 Преобразование двоичного кода в двоично-десятичный осуществляет прямой счет, т.е. суммирование поступающих на их вход импульсов унитарного кода; Таким образом, при последовательном опросе разрядов регистра 1 двоичного кода происходит параллельное накопление его эквивалентов в двоичнодесятичном коде на декадных счетчиках 14. Преобразование заканчивается опросом всех разрядов регистра 1 двоичного кода. Для преобразования двоично-десятичного кода в двоичный преобразуемое число в двоично-десятичном коде введено в счетчик 4 и регистр 13 двоично-десятичного кода. На вход 15 преобразователя должен быть подан сигнал Преобразование двоично-деся тичного кода в двоичный, а сигнал со входа 14 снят. Далее на вход 19 одан сигнал Пуск-2, который осуествляет запись 1 в крайний раз589ряд сдригового регистра 2, а также установку в единичное состояние все разрядов регистра 1 двоичного кода. На аход сдвигового регистра 2 сЗпроса через элемент ИЛИ 12 поступают или сигнал. Сдвига с выхода делителя 3 частоты в случае, если очередной ре-. зультат шага преобразования двоично-десятичного кода в двоичный положительный (остаток 0), или сигнал переноса с выхода элемента 5 задержки старшей декады счетчика k {тысяч iV) в случае, если очередной результат шага преобразования двоично-десятичного кода в двоичный отрицательный (остаток О, см. таблицу). Единица, записанная в сдвиговый регистр 2 опроса, при поступлении описанных сигналов на вход регистра 2 опроса, проходя последовательно каж дый разряд регистра 2, разрешает, начиная со старшего разряда, опрос каждого разряда регистра t двоичного кода через элементы И первой группы 6. Опрашиваемый разряд регистра 1 дво ичного кода аналогично, как и при пре образовании двоичного кода в двоичнодесятичный, через элементы И первой группы 6, элементы ИЛИ первой группы 3 элементы И второй группы 7, зле менты ИЛИ второй группы 10, преобг . разуется в экаиаалентный унитарный код, который параллельно с выходов эл ментов ИЛИ второй группы 10 поступает соответственно на входы декады единиц I, десятков It, сотен И, тысяч tV счетчика . При этом производится параллельное вычитание унитарного кода из содержимого соответствующих декад счетчика k. Вычитание в счетчике происходит вследствии того, что сигнал, поданный на вход 15, Преобразование двоично-десятичного кода в двоичный позволяет осуществить обратный счет декат счетчика Ц, При обратном смете счетчика 4, как известно, возникает сигнал переноса Заем (отрицательный перенос) , который через второй вход элемента 5 задержки, элемент ИЛИ второй группы 10 поступает с более младшей декады счетчика k на более старшую. Сигнал Заем поступает по гем же цепям - выход элемента 5 задержки, элемент ИЛИ 2, вход счетчика Ц, что и сигнал переноса при преобразовании двоичного кода в двоично-десятичный. Результат вычитания опрашиваемого, разряда регистра двоичного кода 1 из двоично-десятичного кода, содержащегося в счетчике 4, может быть как положительный (остаток О), так и отрицательный (остаток 0., см, таблицу) . В случае положительного результата делитель 3 частоты выполняет полный цикл деления и со своего выхода выдает сигнал как на вход 17 записи регистра 13 двоично-десятичного кода, при этом в разряды регистра 13 с декад счетчика А переписывается очередной положительный остаток в двоичнодесятичном коде, так и через элемент ИЛИ 12 на вход регистра 2 опроса. Регистр 2 опроса переходит к опросу следующего разряда регистра двоичного кода 1 - очередной шаг преобразования, причем в предыдущем разряде регистра 1 двоичного кода сохраняется едини- . ца. . В случае отрицательного результата появляется сигнал переноса заем на выходе старшей декады счетчика Ц (тысяч IV j который поступает на делитель 3 частоты, первые входы элементов И группы 8, линию 5 задержки, По этому сигналу Окончание цикла работы делителя частоты 3, происходит установка в О всех разрядов делителя частоты 3 Сигнал переноса, поступивший на первые входы элементов И группы 8, совпадает с сигналом опроса, идущим с выхода соответствующего разряда регистра 2 опроса и далее, проходя элемент И группы 8, устанавливает опрашиваемый разряд регистра 1 двоичного кода в состояние О. С выхода элемента 5 задержки сигнал переноса Заем старшей декады счетчика k (тысяч IV ) поступает на разрядные входы 16 записи декад счетчика Ц, при этом происходит восстановление предыдущего остатка - перезапись двоично-десятичного кода с ре- гистра 13 двоично-десятичного кода в . соответствукхчие разряды декад счетчика , а также поступает через элемент ИЛИ 12 на вход сдвигового регистра 2 опроса. Сигнал опроса переходит к опросу следующего разряда регистра 1 двоичного, кода - очередной шаг преобразовйиия двоично-десятичного кода в двоичный. Таким образом, последовательно опрашивая разряды регистра 1 двоичного , кода и оставляя их в состоянии 1,

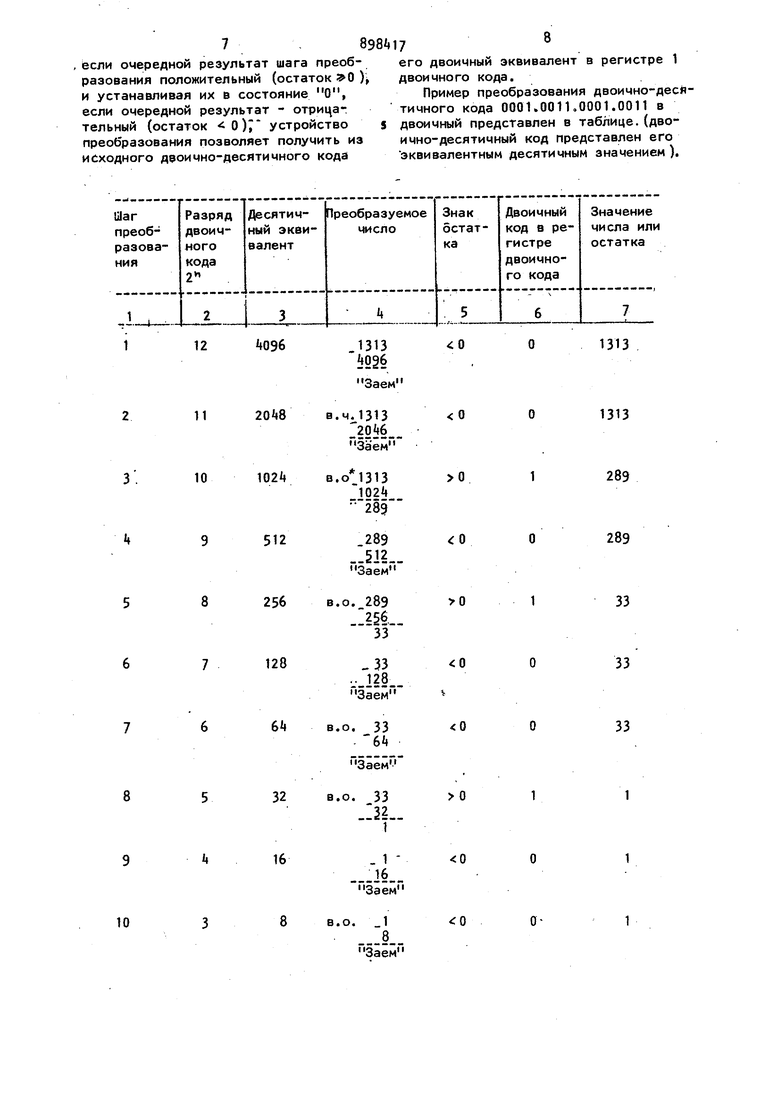

1всли очередной результат шага преобразования положительный (остаток 90 ) и устанавливая их в состояние О, если очередной результат - отрицательный (остаток iO) устройство преобразования позволяет получить из исходного двоично-десятичного кода

его двоичный эквивалент в регистре 1 двоичного кода.

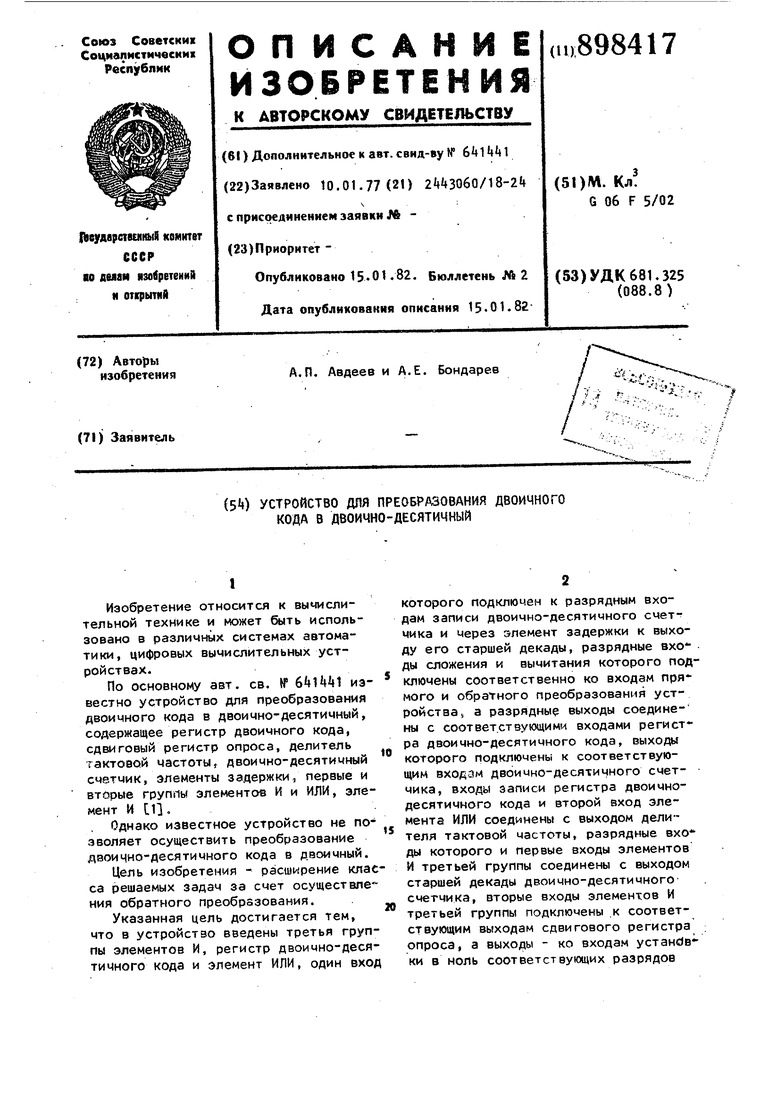

Пример преобразования двоично-десятичного кода 0001.0011,0001.0011 в двоичный представлен в таблице.(двоично-десятичный код представлен его эквивалентным десятичным значением).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1130858A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1976 |

|

SU646327A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

2QkB

в.ч.1313

в.

102Й

.

10

512

256

в.о. 289

128

6tt

в.о. 33 в.о. 33

10

в.о. 1 8

Заем

0

1313

289

0 l02i 289

289

0

-.512.. Заем

0

33

.:2§б,„

-33

0

33

.. 128

0

33 6k

Заем

0

.:22„

. 1 16

:0 Заем

чв,о. .1

2в.о, 1

1ВоО.1

в,о. - восстановление остатка

Преобразователь оканчивается после опроса всех разрядов регистра двоичного кода 1 - в его разрядах содержится эквивалентный исходному двоим- :но-десятичному коду 0001.0011,0001,0011 двоичный код 0010100100001.

Так .как цикл работы делителя 3 частоты прерывателя сигналами переноса Заём, если результат шага преобразования отрицательный, то, очевидно, обратное преобразование двоичнодесятичного кода в двоичный происходит быстрее, нежели прямое преобразование двоичного кода в двоично-десятичный, и тем быстрее, чем больше нулей в комбинации двоичного кода, эквивалентного исходному двоично-десятичному коду преобразуемого числа.

Цикл делителя 3 тактовой частоты определяется максимальным числом унитарного кода, эквивалентного двоичнодесятичному коду тетрады. А так как тет|эады составлены из элементов ИЛИ первой группы 9с соответствующими весами , то, следовательно, максимальный унитарный код тетрады равен девяти, и поэтому цикл работы делителя 3 частоты определяется в 10 импульсов тактовой частоты ТИ, поступающей на вход 20 устройства. Десятый импульс ТИ идет на выход длителя 3 частоты для проведения очередного сдвига на сдвиговом регистре опроса 2.

Элементы 5 задержки имеют два входа, один для сигнала переноса при прямом счете декадного счетмика 4 и другой для сигналов переноса при обратном счете. Для старшей декады счеПродолжение таблицы

0

Ц Siin

0

2 Заём

0

чика k (тысяч IV) используется выход только для сигнала переноса при обратном счете 6

Элементы 5 задержки предотвращают совпадение унитарного кода с сигнашами переносов.

Использование вновь введенных элементов позволяет расширить класс решаемых задач устройства, т.е. осуществлять не только преобразование двоичного кода в двоично-десятичный, но и осуществлять преобразование двоично-десятичного кода в двоичный, что позволяет увеличить возможности применения таких устройств в различных системах автоматики, цифровой технике.

Формула изобретения

Устройство для преобразования двоичного кода в двоично-десятичный по авт, св. № , отличающееся тем, что, с целью расширения класса решаемых задам за счет осуществления обратного, преобразования, 8 устройстао введены третья группа элементов И, регистр двоично-десятичного кода и элемент/ИЛИ, один вход которого подключен к разрядным входам записи двоично-десятичного счетчика и через элемент задержки к выходу его старшей декады, разрядные, входц сложения и вычитания которого подключены соответственно ко входам прямого и обратного преобразования устройства, а разрядные выходы соединены с соответствующими входами ре11898)1

гистра двоично-десятичного кода, выходы которого подключены к соответствующим входам двоично-десятичного счетчика, входы записи регистра двоично-десятичного кода и второй вход 5 элемента ИЛИ соединены с выходом делителя тактовой частоты, разрядные входы которого и первые входы элемен-тов И третьей группы соединены с выходом старшей декады двоичнЬ-десятич-О ного счетчика, вторые входы элементов И третьей группы подключены к

Г12

соответствующим выходам сдвигового регистра опроса, а выходы - ко входам установки в ноль соответствующих разрядов регистра двоимног;о кода, единичные входы разрядов которого подключены ко второму входу устройства .

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-01-15—Публикация

1977-01-10—Подача