1

Изобретение относится к автоматике и вычислительной технике и может применяться для прецезионного задания в широком диапазоне частоты следования импульсов в цифровых информационно-измерительных и управляющих системах.Известен цифровой задатчик частотно-импульсного сигнала, содержащий генератор эталонной частоты/ блок установки задания и управляемые дели тели частоты, работа которых основана на принципе выбора требуемого числа импульсов из каждой пачки импульсов , поступившей от генератора импульсов l .

Однако, этому устройству свойственна неравномерность выходных импульсов, приводящая к флуктуациям мгновенного значения выходной частоты относительно среднего значения.

Наиболее близким по технической сущности является устройство, содержащее генератор эталонной частоты, управляемые делители частоты, суммирующий счетчик, блоки переноса кода, блоки управления и блок установки задания, выход которого через первый блок переноса кода подключен к цифро вому входу первого управляемого дели

теля частоты, выход которого соединен со счетным входом суммирующего счетчика и с первым входом первого блока управления, второй вход которого

5 соединен с зажимом пуск устройства, первый выход - с управляющим входом первого блока переноса кода, а второй и третий выходы соответственно - со входами установки и обнуления первого управляемого делителя частоты, выход суммирукхдего счетчика через второй блок переноса кода подключен к цифровому входу второго управляемого делителя частоты, входы

15 установки и обнуления которого соединены соответственно с первым и вторЕлм выходами второго блока управления, третий выход которого соединен с управлякндим входом второго блока

переноса кода, четвертый выход - со входом обнуления суммирующего счетчика, а первый вход - с выходом второго управляемого делителя частоты, сигнальный вход которого соединен с

25 сигнальным входом первого управляемого делителя частоты 2J .

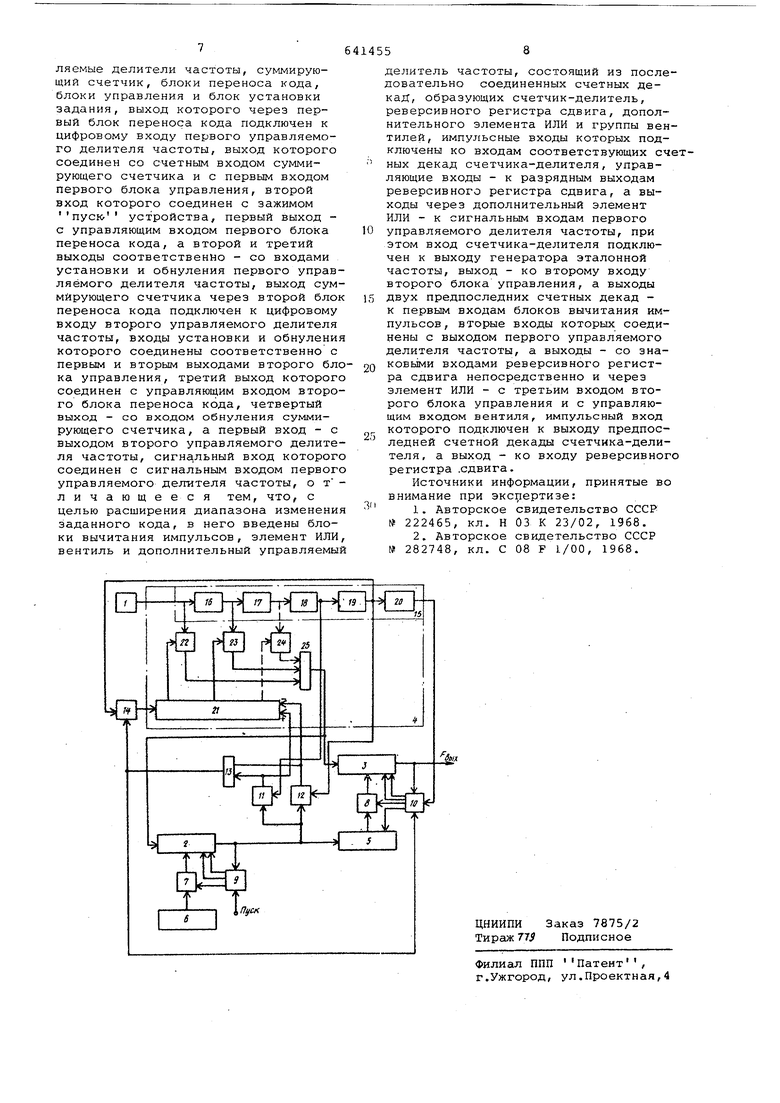

Это устройство позволяет получать на выходе последовательность импудьсов, частота следования которых пропорциональна входному цифровому коду,, без флуктуации мгновенного значения вь;ходной частоты. Однако, расширение диапазона изме нения заданного кода требует пропорционального увеличения объема счетчика и обоих управляемых делителей, каждый из которых включает счетчик, регистр памяти и блок переноса кода что существенно увеличивает объем оборудования устройства и недоисполь зование его ,в разных участках диапазона. Цель, предлагаемого изобретения расширение диапазона изменения зада ного кода. Для этого в устройство .цифрового зада1ния частоты следования импульсов, содержащее генератор эталонной частоты, управляемые делители частоты, суммирующий счетчик, блоки переноса кода, блоки управления и блок установки задания, введены блоки вычитания импульсов, элемент ИЛИ, вентиль и дополнительный управляемый делитель частоты, состоящий из последовательно соединенных счетных декад, образующих счетчик-делитель, реверсивного регистра сдвига, дополнительного элемента ИЛИ и группы вен тилей, импульсные входы которых подключены ко входам соответствующих счетных декад счетчика-делителя, управляющие входы - к разрядньлм выходам реверсивного регистра сдвига, а выходы через дополнительный элемент ИЛИ - к сигнальныгл входам первого управляемого делителя частоты, при этом вход счетчика-делителя подключен к выходу генератора эталонной частоты, выход - ко второму входу второго блока управления, а выходы двух предпоследних счетных декад к первым входам блоков вычитания им пульсов, вторые входы которых соединены с выходом первого управляемого делителя частоты, а выходы - со знаковыми входами реверсивного регистра сдвига непосредственно и через элемент ИЛИ - с третьим входом второго блока управления и с управляющим входом вентиля, импульсный вход которого подключен к выходу предпоследней счетной декады счетчика-делителя, а выход - ко входу реверсивного регистра сдвига. На чертеже представлена структур ная электрическая схема предлагаемого устройства цифрового задания част ты следования импульсов. Оно содержит генератор 1 эталонной частоты, управляемые делители 2 и 3 частоты и дополнительный упра ляемый делитель 4 частоты, суммирующий счетчик 5, блок Ь устройства задания, блоки 7 и 8 переноса кода, блоки 9 и 10 управления, блоки 11 и 12 вычитания импульсов, элемент ИЛИ 13, вентиль 14. Дополнительный управляемый делитель 4 частоты соетоит из счетчика-делителя 15, включающего последовательно соединенные счетные декады 16-20, реверсивного регистра 21 сдвига, вентилей 22-24, дополнительного элемента ИЛИ 25. Устройство работает следующим образом. Выходная последовательность импульсов генератора 1 с высокой частотой следования f поступает на сигнальный вход дополнительного управляемого делителя 4 частоты, где она делится на коэффициент деления, кратный 10 и задаваемый положением реверсивного регистра 21 сдвига. Если имеется сигнал на разрядном выходе реверсивного регистра 21 сдвига, то через открытый этим сигналом вентиль 22 частота с выхода генератора 1 через дополнительный элемент ИЛИ 25 поступает на выход дополнительного управляемого делителя 4 частоты. При этом коэффициент деления делителя 4 частоты равен . При поступлении сдвигающих импульсов с выхода вентиля 14 измеряется положение регистра 21 в зависимости от знака вправо или влево. При изменении состояния регистра 21 вправо коэффициент деления делителя увеличивается в 10-раз на каждый шаг. Так при появлении сигнала на следующем разг рядном выходе регистра 21 открывается вентиль 23 и на выходе 2 частоты появляется частота с выхода счетной декады 16, равная , При поступлении П импульсов на вход регистра 21 коэффициент деления станет равным , а на выходе делителяг 4 частоты сформируется частота Рд с ,п-ой счетной декады счетчика-делителя 15. При изменении знака сдвига регистра 21 положение его будет сдвигаться влево, уменьшая коэффициент деления. Импульсы с выхода делителя 2 частоты поступают на сигнальные входы делителей 2 и 3 частоты, каждый из которых содержит вычитающий счетчик, регистр памяти и блок переноса кода. Коэффициент деления этих делителей определяется кодами, хранимыми в регистрах памяти и обнуляемых по сигналам управления, поступающим от блоков 9 и 10. Коэффициент деления делителя 2 частоты формируется в блоке 6. По сигналу пуск в блоке 9 формируются сигналы управления, переписывающие через блок 7 код задания Njaa предварительно обнуленный регистр памяти делителя 2 частоты. Запись этого кода из регистра памяти в счетчик делителя 2 частоты осуществляется через открытый сигналом блок переноса .(на чертеже не показаны) каждым импульсом на выходе счетчика, возникающим после списания числа из счетчика, осуществляется новая запись из регистра в счетчик и проце деления повторяется. Н выходе делителя 2 частоты образуется последовательность импульсов с частотой ,FOf д Vd °Saa Импульсы ЭТОЙ частоты поступают на счетный вход суммирующего счетчика 5, в котором они суммируются на временных интервалах, задаваемых импульрами частоты с выхода счетчика-делителя 15. Если выбрать эту частоту, равную |-а- -«гч, интервалы времени будут равны t Каждым импульсом частоты f , поступающей на вход блока Ю, сначала обнуляется регистр памяти в делителе 3 частоты, затем из суммирующего счетчика 5 через блок 8 переписывается новое значение коэффициента деления, и, наконец, обнуляется суммирующий счетчик 5. Если импульсы на входе блока 10 совпадают во времени, то процесс записи нового кода задерживается во избежание лож записи в делитель нулевого кода. Меж двумя обнулениями, в суммирующем счет чике 5 образуется код ., . 4 .+ |.. Ni-i --ioi На этот код в делителе 3 частоты делится частота о , поступающая на е счетный вход. На выходе делителя обр зуются выходные импульсы с частотой ifliolliaau- Jiifli-, .f которая при -t численно равна зада нию Благодаря тому, что частота FQ является промежуточной, ее изменение не влияет.на выходную частоту устройства. Структура устройства позволяет при широком диапазоне изменения задания соответствующимобразом менят промежуточную частоту FQ Таким образом, чтобы изменение выходной час тоты f делителя 2 частоты и соответ венно кода -N в суммирующем счетчи ке 5 менялись незначительно. Это по воляет не увеличивать объем счетных ячеек суммирующего счетчика 5 и дел теля 3 частоты при широком изменени задания. Работа устройства в таком режиме обеспечивает с помощью следующей си темы поддержания частоты f делителя 2 частоты в заданных границах. Следящая система образована из двух бл ков 11 и 12 вычитания импульсов, эл мента ИЛИ 13, вентиля 14 и делителя 4 частоты. Блоки 11 и 12 являются, по существу, элементами сравнения. На .блоках 11 и 12 сравнивается выходная частота f делителя 2 част ты с двумя постоянными граничными частотами f|.j и i , получаемых соответственно с выходов счетных декад 19 и 18. Значение f выбирается из соображений получения требуемого минимального кода М в суммирующем счетчике 5, обеспечивающего заданную дискретность при максимальном значении задания. При уменьшении задания частота f делителя 2 частоты увеличивается и код N в суммирующем счетчике 5 растет. Благодаря использованию следящей системы поддерживается неравенствотах imin Если частота i . становится больше тах выходе блока 11 появляется сигнал, поступающий на суммирующий вход реверсивного регистра 21 сдвига и через элемент ИЛИ 13 открывающий вентиль 14, через который на вход регистра 21 поступают импульсы с одной из счетных декад счетчикаделителя 15. Коэффициент деления М делителя 4 частоты, а вместе с ним и его выходная частота FQ начинают изменяться до тех пор, пока выходная частота f делителя 2 частоты не станет снова- меньше f |пач после чего вентиль 14 Закрывается. На время поиска нового значения промежуточной частоты FO при изменении задания сигналом с выхода элемента ИЛИ 13 на вход блока 10 прекращается передача кода из суммирующего счетчика 5 в делитель 3 частоты. После окончания процесса поиска, когда пропадает сигнал на выходе элемента ИЛИ 13, восстанавливается нормальный режим работы устройства. Если же задание изменяется в сторону увеличения, то частота уменьшается и при f f if, срабатывает блок 12, выходным сигналом которого регистр 21 устанавливается на вычитание и поступающие затем через вентиль 14 импульсы сдвига уменьшают коэфф1 циент деления М делителя 4 частоты, увеличивая соответственно частоты FO и f Д° пор, пока частота f не станет больше f friin Аналогично работает устройство при каждом изменении задания, осуществляя поиск нового значения промежуточной частоты путем изменения коэффициента деления делителя 4 частоты до тех пор, пока не будет выполняться неравенствоmax .1 miti Формула изобретения Устройство цифрового задания частоты следования импульсов, содержащее генератор эталонной частоты, управляемые делители частоты, суммирующий счетчик, блоки переноса кода, блоки управления и блок установки задания, выход которого через первый блок переноса кода подключен к цифровому входу Первого управляемого делителя частоты, выход которого соединен со счетным входом суммирующего счетчика и с первым входом первого блока управления, второй вход которого соединен с зажимом пуск. устройства, первый выход с управляющим входом первого блока переноса кода, а второй и третий выходы соответственно - со входами установки и обнуления первого управляемого делителя частоты, выход суммирующего счетчика через второй блок переноса кода подключен к цифровому входу второго управляемого делителя частоты, входы установки и обнуления которого соединены соответственно с первым и вторым выходами второго блока управления, третий выход которого соединен с управляющим входом второго блока переноса кода, четвертый выход - со входом обнуления суммирующего счетчика, а первый вход - с выходом второго управляемого делителя частоты, сигнальный вход которого соединен с сигнальным входом первого управляемого делителя частоты, о т личающееся тем, что, с целью расширения диапазона изменения заданного кода, в него введены блоки вычитания импульсов, элемент ИЛИ, вентиль и дополнительный управляемый

делитель частоты, состоящий из последовательно соединенных счетных декад, образующих счетчик-делитель, реверсивного регистра сдвига, дополнительного элемента ИЛИ и группы вентилей, импульсные входы которых подключены ко входам соответствующих счных декад счетчика-делителя, управляющие входы - к разрядным выходам реверсивного регистра сдвига, а выходы через дополнительный элемент ИЛИ - к сигнальным входам первого управляемого делителя частоты, при этом вход счетчика-делителя подключен к выходу генератора эталонной частоты, выход - ко второму входу второго блока управления, а выходы двух предпоследних счетных декад к первым входам блоков вычитания импульсов, вторые входы которых соединены с выходом перэого управляемого делителя частоты, а выходы - со знаковн1ми входами реверсивного регистра сдвига непосредственно и через элемент ИЛИ - с третьим входом второго блока управления и с управляющим входом вентиля, импульсный вход которого подключен к выходу предпоследней счетной декады счетчика-делителя, а выход - ко входу реверсивног регистра .сдвига.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 222465, кл. Н 03 К 23/02, 1968.

2.Авторское свидетельство СССР № 282748, кл. С 08 F 1/00, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Устройство для преобразования частоты в код | 1977 |

|

SU696604A1 |

| Устройство для преобразования суммы частотно-импульсных сигналов в код | 1976 |

|

SU657441A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Делитель частоты с переменным дробным коэффициентом деления | 1989 |

|

SU1746530A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

Авторы

Даты

1979-01-05—Публикация

1976-08-18—Подача