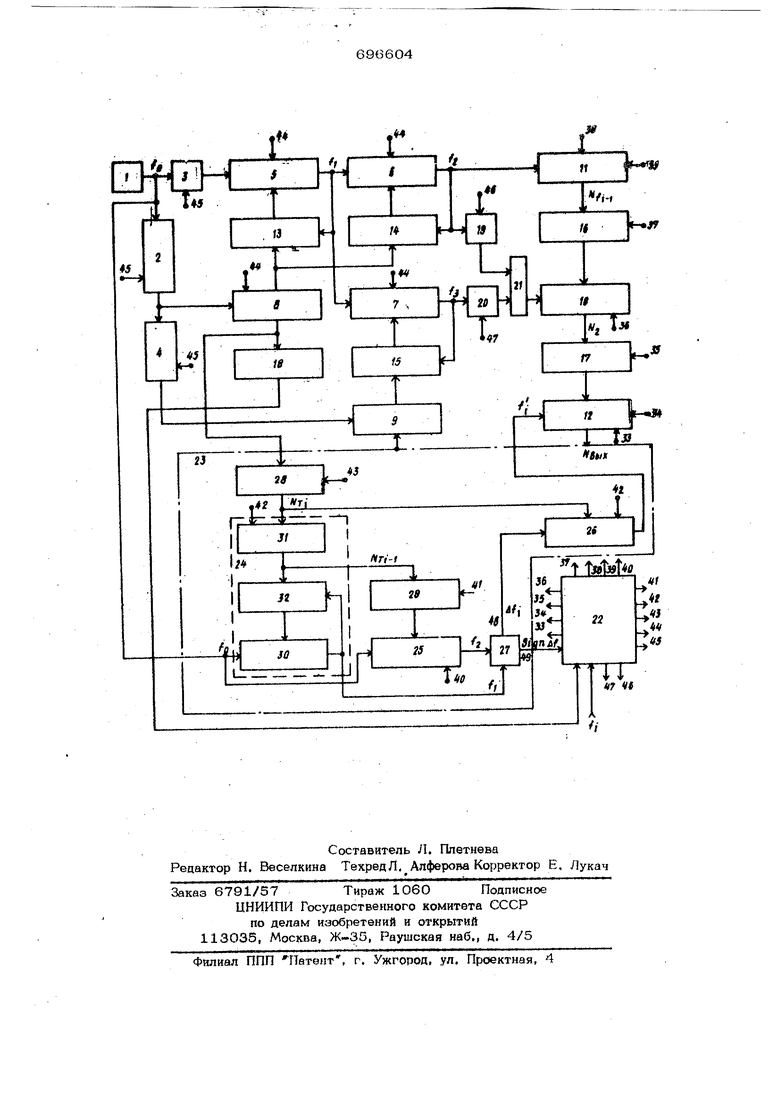

Изобретение относится к измеритель ной технике, автоматике и вычислительной технике и может найти применение в быстродействующих преобразователях частоты в код, используемых в динамических информационно-измер ггельных и управляющих системах. Известны быстродействующие преобразователи частоты в код, основанные н вычитании в течение периода измеряемо частоты из кода, пропорционального мак симальной измеряемой частоте импульсов, частота следования которых изменяется обратно пропорционально квадрату текущего времени, и содержащие генератор опорной частоты, вентиль, вычи ющий счетчик и функциональный генератор переменной частоты fll. Однако известные устройства обладают динамической ошибкой, увеличивающейся с увеличением скорости изменени измеряемой частоты. Наиболее близким по техническому решению к предлагаемому является из- вестный преобразователь частоты в код, содержащий генератор опорной частоты, подключенный выходом через неуправляемый делитель частоты к счетному входу управляющего счетчика, выходы разрядов Kofoporo подключены через две схемы переноса кода к входам разрядов двух последовательно соединенных счетчиков-делителей, выходы которых подключены к управляющим входам соответствующих схем переноса кода, вычитающий счетчик результата, счетный вход которого подключен к выходу второго счетчика-целителя через вентиль и блок управления, подключенный входом к входной клемме устройства, а выходами - к установочным входам вычитающего счетчика, счетчйков-аелителей и управляющего счетчика, к входу обнуления неуправляемого делителя частоты и к управляющему входу вентиля 2. Известное устройство обладает высоким быстродействием и в конце каждого 3 очередного периода измеряемой частоты формирует код, пропорциональный мгновенному значению измеряемой частоты в закончившемся периоде. Однако на протяжении следующего периода этот код остается постоянным и меняется на новое значение лишь в конце следующего периода, хотя текущая частота может меняться за это время. То есть код на выходе устройства меняется ступенька- ми, тем большей величины, чем больше скорость изменения входной частоты. Эт приводит к увеличению динамических ошибок измерения, возрастающих с увеличением скорости изменения измеряемо частоты. Кроме того, известное устройство имеет методическую ошибку, поскол ку полученный код относят в нем к мгно венной частоте в конце закончившегося периода, тогда, как он соответствует мгновенной частоте в середине измеренного периода. Целью изобретения является повышен ТОЧНОСТИ, которое достигается путем уменьшения динамической ошибки и методической погрешности. Поставленная цель достигается тем, что в устройство для преобразования час тоты в код, содержащее, генератор опорной частоты, основной вентиль, последовательно соединенные дбе пересчетные схемы и реверсивный счетчик, неуправля емый делитель частоты, выход которого соединен со счетным входом основного управляющего счетчика, выход которого через первый и второй блоки переноса кода подключены к кодовым входам соот ветственно первой и второй пересчетных схем, управляющие входы которых соеди нены с выходами соответствующих пересчетньпс схем, дополнительно введены де литель частоты на два, делитель частоты на три, дешифратор, вентиль, элемент ИЛИ, вычитающий счетчик, реверсивный счетчик результата, блок управления, блок дифференцирования, управляющий счетчик, пересчетная схема и три блока переноса кода, причем выход генератора опорной частоты подключен через делитель частоты на два к счетному входу первой пересчетной схемы и непосредственно ко входу неуправляемого делителя частоты и первому входу блока дифферен цировання, первый и второй выходы кото рого соединены соответственмо с первым входом блока управления и бчетным вхо дом реверсивного счетчика результата. - ВЫХОД первой пересчетной схемы подключен к управляющему входу дополнительной пересчетной схемы, выход которой подключен непосредственно к управляющему входу первого дополнительного блока переноса кода и через дополнительный вентиль к первому входу элемента ИЛИ, второй вход которого через основной вентиль подключен к выходу второй пересчетной схемы, выход элемента ИЛИ соединен с управляющим входом вычитающего счетчика, выход основного управляющего счетчика соединен непосредственна со вторым входом блока дифференцирования и через дешифратор со вторым входом блока управления, третий вход которого подключен к входной шине, выход еуправляемого делителя частоты через последовательно соединенные делитель частоты на три, дополнительный управляющий счетчик и первый дополнительный блок переноса кода подключен к кодовым входам дополнительной пересчетной схемы, выход реверсивного счетчика через последовательно соединенные второй дополнительный блок переноса кода, вычита ющий счетчик и третий дополнительный блок переноса кода подключен к кодовым входам реверсивного счетчика результата, блок дифференцирования содержит блок вычитания, три управляемых делителя частоты и два блока переноса кода, причем первая входная шина блока дифференцирования подключена к управляющим входам первого и второго управляемых делителей частоты, вторая входная щина блока дифференцирования через первый блок переноса кода подключена к кодовым входам первого и третьего управляемых делителей частот., первый выход первого управляемого делителя частоты через второй блок переноса кода подключен к кодовым входам второго управляемого делители частоты, выход которого соединен с первым входом блока вычитания, ко второму входу которого подключен второй выход первого управляемого делителя частоты, выходная шина блока дифференцирования соединена с первым выходом блока вычитания, второй выход которого через третий управляемый делитель частоты подключена ко второй выходной шине блока дифференцирования, и, кроме того, управляемый де литель частоты содержит последовательно соединенные регистр памяти, блок переноса кода и пересчетную схему, выход которой соединен с управляющим входом блока переноса кода и второй выходной шиной управляемого делителя частоты, управляющим и кодовыми входами у1фавляемого делителя частоты являются соот ветственно счетный вход пересчетной схе мы и кодовые входы регистра памяти, первым выходом управляемого делителя частоты является выход регистра памяти. На чертеже изображена блок-схема устройства. Устройство содержит генератор опорной частоты 1, неуправляемый делитель частоты 2, делитель частоты 3 на два, делитель частоты 4 на три, пересчетные схемы 5-7, управл5иощие счетчики 8 и 9, вычитающий счетчик 10, реверсивный счетчик 11, реверсивный счетчик результата 12, блоки переноса кода 13 - 17, дешифратор 18, вентили 19 к 20, элемоит ИЛИ 21, блок управления 22 и блок дифференцирования 23. Еэлок дифференцирования 23 содержит управляемые яелитэли чартоты 24 - 26, блок вычитания 27 и блоки переноса кода 28, 29, Каждый из управляемых делителей частоты включает в себя пере- счетную схему 30 и регистр памяти 31 соедтхенных разрядами через блок переноса кода 32, управляющий вход которого подключен к выходу пересчетной схемы 30. Первый вход блока управления 22 подгэтючен к входной шине устройства f . Выходы блбка управления 22 подключены следующим образом: выходы 33 и 34 к входу обнуления и знаковому входу реверсивного счетчика результата 12, выход 35 - к управляющему входу блока переноса кода 17, выход 36 - к входу обнуления вычитающего счетчика, выход 37 - к управляющему входу блока переноса кода 16, выходы 38 и 39 - к установочному к знаковому входам реверсивного счетчика 11, выход 4О - к входу обнуления регистра памяти в управляемом делителе частоты 25, выход 41 - управляющему входу блока переноса кода 29, выход 42 - к входам обнуления регистров памяти в управляемых делителях частоты 24 и 26, выход 43 к управляющему входу блока переноска ко да 28, выход 44 - к установочным входам пересчетных схем 5 - 7 и управляю щих счетчиков 8 и 9, выход 45 - к вхо дам обнуления делителей частоты 2-4, выход 46 и 47 - к управляющим входам вентилей 19 и 20. Сигнальный выход 48 блока вычитания 27 подключен к сигналь ному входу управляемого делителя час тоты 2.6, а знаковый выход 49 блока 27 подключен ко второму входу блока управления 22, третий вход которого подключен к выходу дешифратора 18, подключенного к выходам разрядов основного управляющего счетчика 8, которые также подключены через блоки переноса кода 13, 14 и 28 к входам разрядов соответственно пересчетных схем 5 и 6 и регистров памяти 31 в управляемых делителя частоты 24 и 26, Выход генератора I подключен к сигнальным вхоцам управляемых делителей частоты 24 и 25, через делитель частоты 3 на два к счетному входу пересчетной схемы 5 и через неуправляемый делитель 2 - к. счетному входу ССновного упрйвляттлего счетчика 8, Выход делителя 2 через делитель частоты 4 на три подключен к счетному входу дополнительного управляющего счетчика 9, выходы разряда которого подключены к пересчетной схеме 7 через блок переноса кода 15, управляющий вход которого подключен к выходу пересчетной схемы 7, которая также подключена через вентиль 2О ко входу элемента ИЛИ 21. Выход пересчетной cxeNfM 5 подключен к управляющему входу блока переноса кода 13 и к счетным входам пересчет- ной схемы 6 и 7, Выхед пересчетной схемы 6 подключен к у1фавл5гющему входу блока переноса кода 14, к счетному входу реверсивного счетчпка 11 н через вентиль 19 к входу элемента ИЛИ 21, выход которого подключен к счвткому входу вычитающего счетчика 1О. Выходы разрядов реверсивного счетчика 11 подключены через блок переноса кода 16 к входам разрядов вычитающего счетчика 10, выходы разрядов которого подключены через блок переноса кода 17 к входам разрядов реверсивного счетчика результата 12, счетный вход которого подключен к выходу управляемого делителя 4 частоты 26 в блоке 23. Выходы разрядов регистра памяти 31 в управляемом дел1стеле 24 подключен через блок переноса кода 29 к установочному входу управляемого делителя частоты 25. Выходы управляемых делителей частоты 24 и 25 подк:1ючены к входам блока вычитания 27. Изобретение реализует следующий алгоритм: ч .U) SbU гдо , It) - текущее значение выход ного кода; - мгновенное значение входной частоты, соответствующее периоду приращение входной частоты за период ; первая производная по времени входной частоты соответствующая перио 1ДнГмоменты окончания соот и Т ветственно периодов входной частоты. Этот алгоритм известен по способу, основанному на обратно пропорциональном преобразовании в код временного интервала между импульсами измеряемой частоты и добавления после преобразования половины приращения измеряемой час тоты на преобразованном временном интервале и приращения, полученного интегрированием на текущем временном ин тервале измерения производной входной частоты, полученной на преобразованном интервале. Благодаря добавлению к полученному в известном устройстве. коду по ловины приращения частоты за измеряемый период устраняется методическая ошибка измерения, а добавление интеграла от производной измеряемой частоты позволяет ввести коррекцию по скорости измерения. измеряемой частоты, что в ко нечном- счете увеличивает динамическую точность устройства. В зависимости от знака приращения измеряемой частоты предлагаемое устройство реализует два следующих алгоритма:,-., ,H , -X . (3) Работает устройство следующим обр зом. С выхода генератора 1 импульсы вь сокой опорной частоты f поступают на входы делителей частоты 2 и 3 с коэффициентами деления соответственно К и 2. На выходе делителя 2 частота равна FP - -j , а на выходе делителя 3 частота равна FO,- Импульсы с частотой следования о,-{ поступают ja вход делителя 4 с коэффициентом делення, равным трем. На выходе делителя 4 частота равна РОЗ 3k Импульсы с частотой FO поступают на счетный вход управляющего счетчика 8, где они суммируются на временном интервале, равном текущему периоду измеряемой частоты. Код в счетчике 8 меняется линейно во времени. N,t). (4) Аналогично код в счетчике 9 будет меняться по выражению: V --Jfo.jdt ЗК (5) Обратный код N-( (t) счетчика 8 каждым импульсом переполнения пересчетных схем 5 и 6 записывается в них через блоки переноса кода 13 и 14. Обратный код ) каждым импульсом переполнения пересчетной схемы 7 записывается в него через блок переноса кода 15. После поступления каждого импульса входной частоты f в блоке управления 22 вырабатываются сигналы управления, по которым делители 2, 3 и 4 обнуляются, в счетчики 8 и 9 записывается единица, а в пересчетные схемы 5, 6 и 7 ее обратный код 2 - 1. Пересчетные схемы 5 и 6 работают как делители частоты с переменным коэффициентом деления, равным текущему коду N-, (-fc) в управляющем счетчике 8, а пересчетная схема 7 работает как делитель частоты с коэффициентом деления N2(t) , равным текущему коду в управляющем счетчике 9. На выходе пересчетной схемы 5 формируется сигнал с частотой Г„, |„-К k fl( l) обратно пропорциональной текущему времени. f (-t) поступает на счетные Частота входы пересчетных схем 6 и 7, где она делится соответственно на коэффициенты МгС-Ь) и ) . На выходе пересчетной схемы 6 формируется сигнал с частотой f (t) к-к к2 2i-fit 969 обратно пропорциональной кнодрату текущего времени. На выходе пересчетной схемы 7 формируется сигнал с частотой f (..iiiil.., ... J (t) OfJ.2(о) После поступления каждого импульса входной частоты f в блоке управления 22 в зависимости от знака приращения Д -J , вырабатываются сигналы управления, устанавливающие реверсивные сче чики 11 и 12 в одно из положений и от крывающие один из вентилей 19 или 2О. Если знак приращения положительный (входная частота растет), то реверсивные счетчики 11 и 12 устанавливаются сигналами на выходах 39 и 34 на сложение, и открывается вентиль 2О. При отрицательном знаке приращения (входная частота уменьщается) счетчики 11 к 12 устанавливаются на вычитание и открывается вентиль 19. Интенгрирование входных импульсов в счетчиках 10 к 11 производится на интервале времени, равном разности меж ду текущим периодом иПпериодом Т,ц, соответствующим максимальной измеряемой частоте i qj -Формирование этого интервала производится следующим образом. По ле поступления очередного импульса вход ной частоты (начало очередного периода) в управляющем счетчике 8 начинают сум мироваться импульсы частоты FO 2После поступления ,,-,. импульсов, которое происходит через интервал времени, равный Тцдцц , срабатывает дешифратор 18, подключенный к выходам разрядов счетчика 8, Сигнал с выхода дешифратора 18 поступает на вход блока управления 22 и в нем формируются сигналы, открывающие один из вентилей 19 или 2О и записьтающие в счетчик IJ. 11 КОД N. с задержкой -NVtSKC о -fAHH ,на время i н относительно начала очередного периода. Так как интегрирование. в счетчиках 11 и 1О заканчивается при поступлении следующего импульса входной частоты, т. е. по окончании очередного i -го периода, то время интегрирования равно Д. . В счетчике 11 производится формирование в конце периода кода, пропорционального половине частоты, соответствующей предыдущему T1 периоду . ллакс т После пс :ту11Л Мия каждого импульса змеряемой частигы f в блоке 22 ормируются сигналы управления, послеовательно обнуляющие реверсивный счетик результата 12, переписывающие из ычитающего счетчика 10 его код в четчик 12 через блок переноса кода 17, бнуляющие счетчик Юн переписываюие в него через блок переноса кода 16 од из счетчика 11. После устано1.кк в четчике 11 ,. к открывания дного из вентилей 19 или 2О начинается овый такт преобразования. Так как пеед началом интегрирования в вычитаюий счетчик 10 импульсов с выхода элеента ИЛИ 21 переписывается код, соответствующий предыдущему Т периоду, о после окончания очередного Т.,- -го периода в счетчике 1О в зависимости от знака приращения будет сформирован следующий код: ,(-tldt-J 2-, fgCtldt тI ллим о мин / -1 L VJilf r jLr V о j 2 1MJ CUdt-J ма КС Т, J мин MMH i--i / t,Kir()Полученный после окончания из с тчика 10 периода код 14 с тчика 10 переписывается в реверсивный счетчик 12 результата, где производится его алгебраическое суммирование с приращением, полученным текущим интегрированием на интервале времени, равном периоду Ti,( импульсов, поступающих на вход счетчика 12 с выхода блока дифференцирования 23, и частота следования которых пропорциональна производной входной частоты Рассмотрим процесс формирования выходных импульсов в блоке дифференцирования 23. После окончания очередного -го периода входной частоты в управляющем счетчике 8 будет сформирован код . пропорциональный периоду Т . Этот Код переносится через блок 28 в предварительно обнуленные регистры памяти 31 в управляемых, делителях час тоты 24 и 26. Перед обнулением регист ра 31 в управляемом делителе 24 код предыдущего периода из него переписывается через блок переноса кода 29 в обнуленный регистр памяти управляемого делителя 25. Таким образом, в регистрах памяти управляемых делителей 24 и 26 после окончания -го периода будет записан код, пропорциональный этому периоду, а в регистре памяти управляемого делителя 25 будет записан код, пропорциональный предыдущему -му периоду. Записанные в регистpax коды являются коэффициентами деления соответствующих управляемых дели- телей частоты. В делителях 24 и 25 производится деление опорной частоты , поступающей на счетные входы пересчетной схемы 30 с выхода генератора 1, на коэффициенты деления соответственно NJ. и Н-г. . . Каждым импульсом .переполнения в счетчик ЗО через блок переноса кода 32 записывается обратный код. На выходе пересчетной схемы 3 О, являющейся выходом делителя 24, формируется сигнал с частотой: На выходе делителя частоты 26 формируется сигнал с частотой: о (14) Частоты F и Fg поступают на входы блока вычитания 27. На выходе 48 блока 27 формируется частота, равная разности входных частот ..F,.-f.,),. .„ а На выходе 49 формируется сигнал зна ка приращения входной частоты ., который поступает на вход блока управ ления 22. Частота Д F , пропорциональная приращению мгновенного значе- 6 O412 н{гя входной частоты эа период Т , поступает на сигнальный вход делителя 26, где она делится на код N-5- - , за писанный в регистре памяти целителя. На выходе делителя 26 формируется сигнал с частотой 2 ....2 (16) г -AEL K(i,-f,-0 Aia- Jilr -N.-. - ,- T, - f,. пропорпиональноР первой гфонзводной входной частоты по времени. Импульсы частоты РЗ интегрируются в реверсивном счетчике 12 на временном интерве ле, равном следующему периоду Т -Ь-. -t .На выходе реверсивного (Счетчика результата 12 в зависимости от знака приращения частоты формируется выходной код: ХР clt-( ±.i: . . о 2 1ч / .(. () v2 /г . ()о(.). ив Таким образом, устройство реализует алгоритм, позволяющий компенсировать методическую ошибку и вводящий приращение, учитывающее скорость изменения входной частоты. Благодаря этому уменьшается динамическая ошибка, устройства и результат будет меняться не ступенями, как в известном устройстве , а непрерывно, что существенно улучшает динамику замкнутых систем регулирования и измерения, в которые входит устройство. Формула изобретения 1, Устройство для преобразования частоты в код, содержащее генератор опорной частоты, основной вентиль, последователь.но соединенные две пересчетные схемы и реверсивный счетчик, неуправляемый делитель частоты, выход которого соединен со счетным входом основного управляющего счетчика, выход которого чераз первый и второй блоки переноса кода подключен к кодовым входам соответственно первой и второй пересчетнь х схем, управляющие входы которых соединены с выходами соответствующих пересчетных схем, отличающееся тем, .что, с целью повышения точности, в него дополнительно введены делитель частоты на два, делитель частоты на три, дешифратор, вентиль, элемент ИЛИ, вычитающий счетчик, реверсивный счетчик результата, блок управления, блок диффе ренцирования, управляющий счетчик, пересчетная схема и три блока переноса кода, причем выход генератора опорной частоты подключен через делитель частоты на два к счетному входу первой пересчетной схемы и непосредственно ко входу неуправляемого делителя частоты и первому входу блока дифференцирования, первый и второй выходы го соединены соответственно с первым входом блока управления и счетным входом реверсивного счетчика результата, выход первой пересчетной схемы подклю чен к управляющему входу дополнительной пересчетной схемы, выход которой подключен непосредственно к управляю- цему входу первого дололнительного блока переноса кода и через дополнительны вентиль к первому входу элемента ИЛИ, второй вход которого через основной вен тиль подключен к выходу второй пересчетной схемы, выход элемента ИЛИ соединен с управляющим входом вычитающе го счетчика, выход основного управляющего счетчика соединен непосредственно со вторым входом блока дифференцирования и через деши4ратора со вторым входом блока управления, третий вход которого подключен к входной шине, выход неуправляемого йелателя частоты через последовательно соединенные делитель частоты на три, дополнительный управля ющий счетчик и первый дополнительный блок переноса кода подключен к кодовым входам дополнительной пересчетной схемы, выход реверсивного счетчика через последовательно соединенные второй дополнительный блок переноса кода, вычитающий счетчик и третий дополнительный блок переноса кода подключен к кодовым входам реверсивного счетчика результата. 6 4 2.Устройство поп, 1, отличающееся тем, что блок дифференцирования содержит блок вычитания, три управляемых делителя частоты и два бло- ка переноса кода, причем первая входная шина блока дифференцирования подключена к управляющим входам первого и второго управляемых делителей частоты, вторая входная шина блока дифференцирования через первый блок перет-оса кода подключена к кодовым входам первого и третьего управляемых делителей частоты, первый выход первого управляемого делителя частоть через второй блок переноса кода подключен к кодовым входам управляемого делт-еля частоты, выход которого соединен с первым входом блока вычитания, ко второму входу которого подключен второй выход первого управляемого делителя частоты, выходная шина блока дифференцирования соединена с первым выходом блока вычитания, второй выход которого через третий управляемый делитель частоты подключена ко выходной шине блока дифференцирования. 3.Устройство по пп. 1, 2, отличающееся тем, что управляемый делитель частоты содержит последовательно соединенные регистр памяти, блок переноса кода и пересчетную схему, выход которой соединен с управляющим входом блока переноса кода и второй выходной шиной управляемого делителя частоты, управляющим и кодовыми входами управляемого делителя частоты являются соответственно счетный вход пересчет- ной схемы и кодовые входы регистра памяти, первым выходом управляемого делителя .частоты является выход регистра памяти. Источники информации, принятые во внимание при экспертизе 1. А. А. Мельников и др. О некоторых путях построения быстродействующих преобразователей частоты в код , Автометрия 1972, № 2. 2. Авторское свидетельство СССР N 391490, кл. Q 91 Т1 23/02, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Устройство для дифференцирования частотноимпульсных сигналов | 1974 |

|

SU495675A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1976 |

|

SU624244A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU894729A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU525235A1 |

Авторы

Даты

1979-11-05—Публикация

1977-05-25—Подача