1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании высокопроизводительных вычислительных систем.

Известна логическая схема сдвига 1, состоящая из нескольких схем логических уровней, каждый из которых содержит логические-элементы типа И, или 1.

Число t уровней , на которые разделена логическая схема сдвига, является целым числом и должно удовлетворять соотношению .2 (N+1 - разрядность нормализуемого числа).

Каждый из уровней срдержит логический блок сдвига влево, с помощью которого двоичное число сдвигается влево на определенное число разрядов.

Известно сдвигающее устройство, позволяющее выполнять сдвиг входной информации параллельно .на требуемое число разрядов за один такт и содержащее матрицу из элементов памяти долговременного типа (триггеров) и логические схемы И, ИЛИ 2,

Наиболее близким к изобретению является устройство для нормализации чисел, содержащее несколько последовательно соединенных схем логических уровней, каждая из которых содержит анализатор содержимого групп на нуль, соединенный входами с выходами вентильной схемы предыдущего уровня, а выходами - с входами -дешифратора величины сдвига, выходы которого подключены к входам шифратора и вентильной схемы данного уровня pj,

10

К-разрядное число N, определяющее количество нулей перед стариим ненулевым разрядом нормализуемого числа, разбивается на группы, содержащие количество разрядов К, К 2

К, К,,..., Kfn(K +K2+K3+K4l + ...).

Вентильная схема каждого логического уровня сдвигает число влево на величину, определяемую весовыми коэф20 фициентамии значениями разрядов соответствунхцей группы.

С увеличением разрядности нормализуемого числа растет число логических уровней, что приводит к увеличению(аппаратурных затрат и времени выполнения операции нормализации.

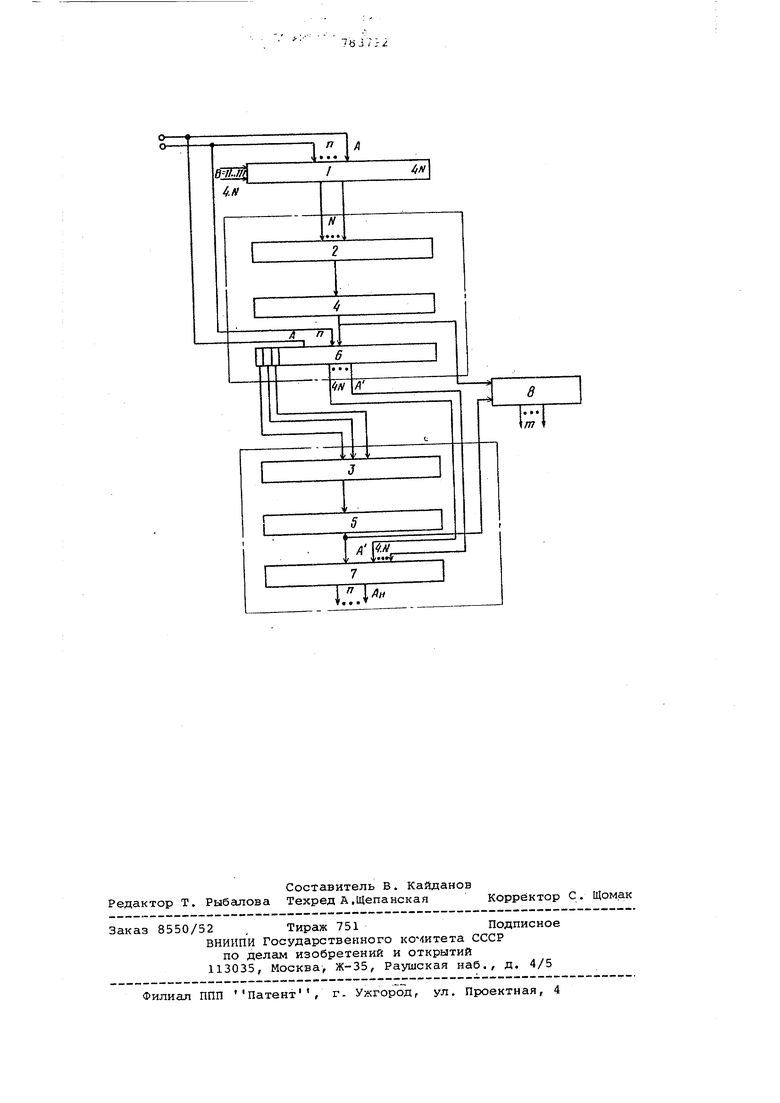

Недостатком этого устройства являются сравнительно большие аппаратные затраты и зависимость времени выполнения операции нормализации от разрядности нормализуемого числа. Цель изобретения - упрощение устройства. Достигается она тем, что устройство для нормализации двоичных чисел включающее коммутаторы и дешифраторы причем информационные входы первого коммутатора соединены с первым входом устройства, информационные входы второго коммутатора соединены с в|ыходами первого коммутатора, содержит регистр порядка, два шифратора, сумматор, первая группа входов котор|ого подключена к первому и второму врсодам устройства, выход переноса каждой тетрад сумматора ( где п - разрядность нормализуемых чисел) подсоединен к соответствующему входу первого дешифратора, выходы которого соединены с входами первого шифратора, связанного выходами с первой группой входов регистра порядка и с управляющими входами первого коммутатора, выходы трех старших разрядов которого соединены с входами второго дешифратора, связанного выходами с входами второго шифратора, выходы которого соединены с второй группой входов регистра порядка и с усправляющими входами второго коммутатора. Блок-схема устройства приведена На чертеже. Устройство содержит сумматор 1, Первый и второй дешифраторы 2 и 3, первый и второй шифраторы 4 и 5, пер вый и второй коммутаторы 6 и 7, регистр 8 порядка. Нормализуемое число А разрядностью п разбивается на N тетрад, начиная со старшего разряда. В случае наличия неполной крайней тетрады она дополняется нулями. Число А является первым слагаемым, поступающим на первую группу входов сумматора 1. Старшие разряды нормализуемого числа поступают на младшие разряды (4 N) - разрядного сумматора, а млад шие разряды нормализуемого числа на старяие разряды сумматора. Вторым слагаемым является .двоичное число, состоящее из (4N ) единиц,- поступающее на вторую группу входов сумматора 1 4N разрядов сумматора 1 также разбиты на N тетрад, начиная со старшегоразряда. Таким образом,.возникающий при с жении перенос между тетрадами сумма ра распространяется в направлении от младших тетрад сумматора к старш а по отношению к тетрадам нормализуемого числа - от старших к младшим. При поступлении на сумматор 1 п-разрядного нормализуемого числа А и (4N) - единиц второго слагаемог на выходе сумматора формируется Nразрядное число, разрядами которого являются переносы между тетрадами сумматора. Первый перенос формируется в тетраде сумматора, на которую поступает старший ненулевой разряд нормализуемого числа. При этом во всех последующих старших тетрадах сумматора формируются переносы независимо от нулей в соответствующих тетрадах нормализуемого числа. Нули в М разрядиом числе на выходе сумматора 1 соответствуют тетрадам нормализуемого числа, состоящим из одних нулей и н аходящимся перед первой значащей тетрадой нормализуемого числа. Первый дешифратор 2 в .соответствии с поступающим на его входы Nразрядным числом из сумматора 1 формирует сигнал выборки из первого ш 1- фратора, где записаны номера тетрад нормализуемого числа, начиная с нулевого номера. На выходе первого шифратора 4 в соответствии с кодом Н-разрядного числа формируется номер первой значащей тетрады нормализуемого числа. Выходы первого илфратора 4 соединены с первой группой входои регистра 8 порядка и входами управления первого коммутатора б. Номер первой значащей тетрады поступает на входы управления первого коммутатора б, обеспечивая сдвиг поступающего на информационные входы первого KOivttiyTaTopa б нормализуемого числа на 4 К разрядов влево, где К - номер первой значаще й тетрады нормализуемого числа. Одновременно К записывается в m - 2 старших разряда т-разрядного регистра 8 порядка (т-разрядное число определяет количество нулей перед старшим ненулевым разрядом нормализуемого числа А). Запись номера К в m 2 старших разряда регистра порядка 8 соответствует записи величины сдвига влево на 4 К, осу7дествлеиного в первом коммутаторе 6. Сд1зи утое на, 4 К разрядов влево нормализуемое число А поступает на входы второго комт- утатора 7. Макс -1мальное число нулей перед старшим ненулевым разрядом сдвинутого .aлизyeмoгo числа А равно трем. Старшие три разряда первого коммутатора 6 выходами соединены с входами второго дешифратора 3, выходы которого соединены с входами второго шифратора 5. Второй дешифратор 3 формирует сигналы выборки из второго шифратора 5 номера старшего ненулевого разряда сдвинутого числа А по формулам вида flL- -Ч а;ла,даз-, , Ajc а;ла2ла -,

Во втором шифраторе 5 записаны номера старших четырех разрядов числа А , начиная с нулевого. С выходов второго шифратора 5 номер старшего ненулевого разряда К (двухразрядное цвоичное число) поступает на входы управления второго коммутатора 7, обеспечивая сдвиг числа А влево на К разрядов и, следовательно окончательную нормализацию числа А, и на вторую группу входов регистра 8 порядка. Двухразрядный номер К записывается Б младшие два разряда т-разрядного регистра 8 порядка, в котором после этого будет сформирован порядок нормализованного числа А j .

При увеличении разрядности исходного нормализуемого числа А увеличивается на соответствующее число разрядов .длина всех (за исключением второго дешифратора 3) узлов устройства для нормализации двоичных чисел.

Увеличение аппаратурных затрат, связанное с ростом разрядности исходного нормализуемого числа, в предлагаемом устройстве значительно меньше , чем в прототипе. Время выполнения операции нормализации постоянно, не зависит от разрядности нормализуемо-, го числа и определяется по формуле вида.

Время нормализации .+et, где t4.- время суммирования в сумматоре.;

t«- среднее время задержки в узлах устройства.

В качестве примера рассмотрим устройство для нормализации 40-разрядного двоичного числа, используем микросхемы серии 155.

Как показали расчеты, при реализации устройства экономия в аппаратурных затратах (в количестве используемых микросхем) по сравнению с устройством, выбранным в качестве прототипа, достигает 30% ().

В случае нормализации п-разрядного числа с пocлeдs oщим использованием

В старших разрядов мантиссы нормализованного числа (E-in) экономия в аппаратурных затратах предлагаемого устройства по сравнению с прототипом СТАНОВИТСЯ более значительной (например, при и С 12, ) .

Формула изобретения Устройство для нормализации двоич0

ных чисел, содержащее коммутаторы и дешифраторы, причем информационные входы первого коммутатора соединены с первым входом устройства, информационные входы второго коммутатора

5 соединены с выходами первого коммутатора, отличающееся тем, что, с целью упрощения устройства, оно содержит регистр порядка, два шифратора, сумматор, первая группа входов

0 которого подключена к первому и второму входам устройства, выход переноса каждой из N тетрад сумматора , где п - разрядность нормализуемых чисел) подсоединен к соответствующему входу первого дешифратора, выходы которого соединены с входами первого шифратора, связанно1 о выходами с первой группой входов регистра порядка и с управляющими входами первого коммутатора, выходы трех старших разрядов которого соединены с входами второго дешифратора, связанного выходами с входами второго шифратора, выходы которого соединены с второй группой входов регистра порядка и с управляющими входами второго коммутатора.

Источники информации, принятые во внимание при экспертизе

1.Патент Японии 48-23866, 0 кл. G 06 F 7/54, 1973.

2.Патент Великобритании № 1323825, кл, G 06 F 7/00, 1973.

3.Авторское свидетельство СССР

№ 397908, кл. G 06. F 7/38,. 1972 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нормализации двоичных чисел | 1982 |

|

SU1056181A1 |

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Устройство для взаимной нормализации двоичных чисел | 1980 |

|

SU896616A1 |

| Устройство для формирования сигналов четности | 1988 |

|

SU1571591A1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ ЧИСЕЛ | 1973 |

|

SU397908A1 |

| Устройство для нормализации чисел | 1986 |

|

SU1307454A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Авторы

Даты

1980-11-30—Публикация

1979-01-22—Подача