Дешифратор 5 предназначен для фор- 10 логически сдвинутого вправо на величину, задаваемую кодом на вхоДе 13, N-разрядного кода относительно кода, установленного на входе 9. Сигнал четности 0-го байта формируется аналогично как и 1-го разряда с тем отличием, что на выход 0-го коммутатора группы 2 передается нулевой код с входа 28.

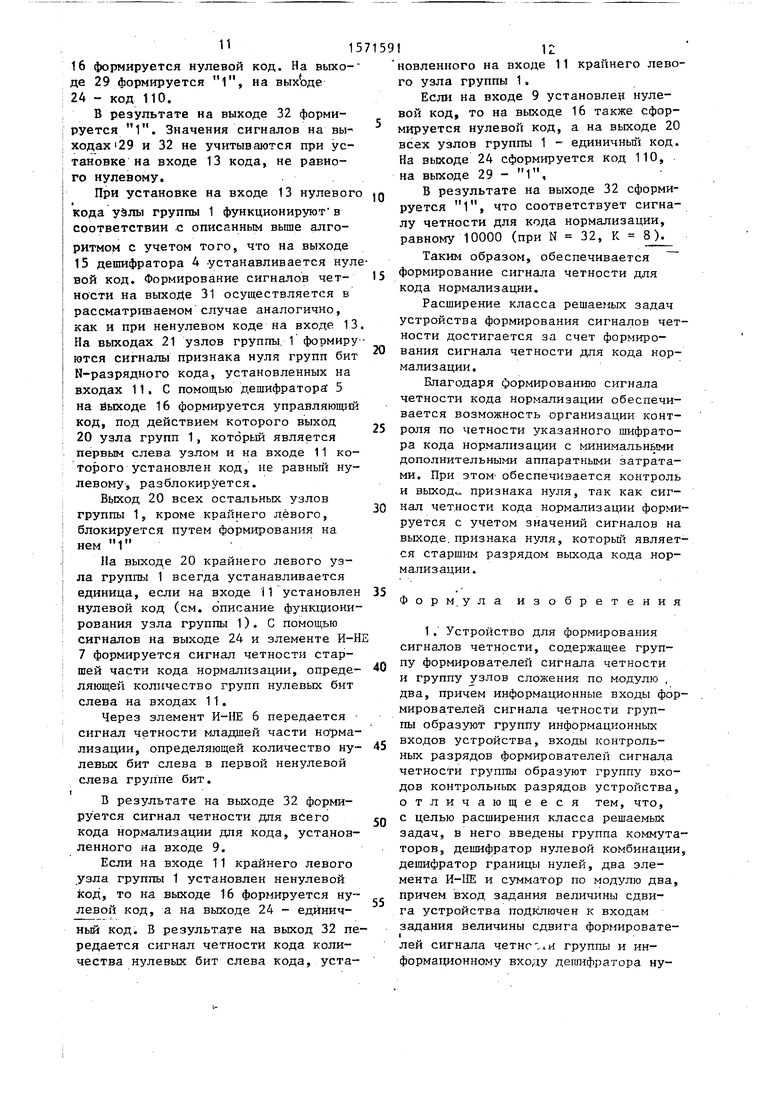

мирования управляющего кода для формирователей сигналов четности, фиксирующего границу нулей слева в коде, установленном на информационном вход

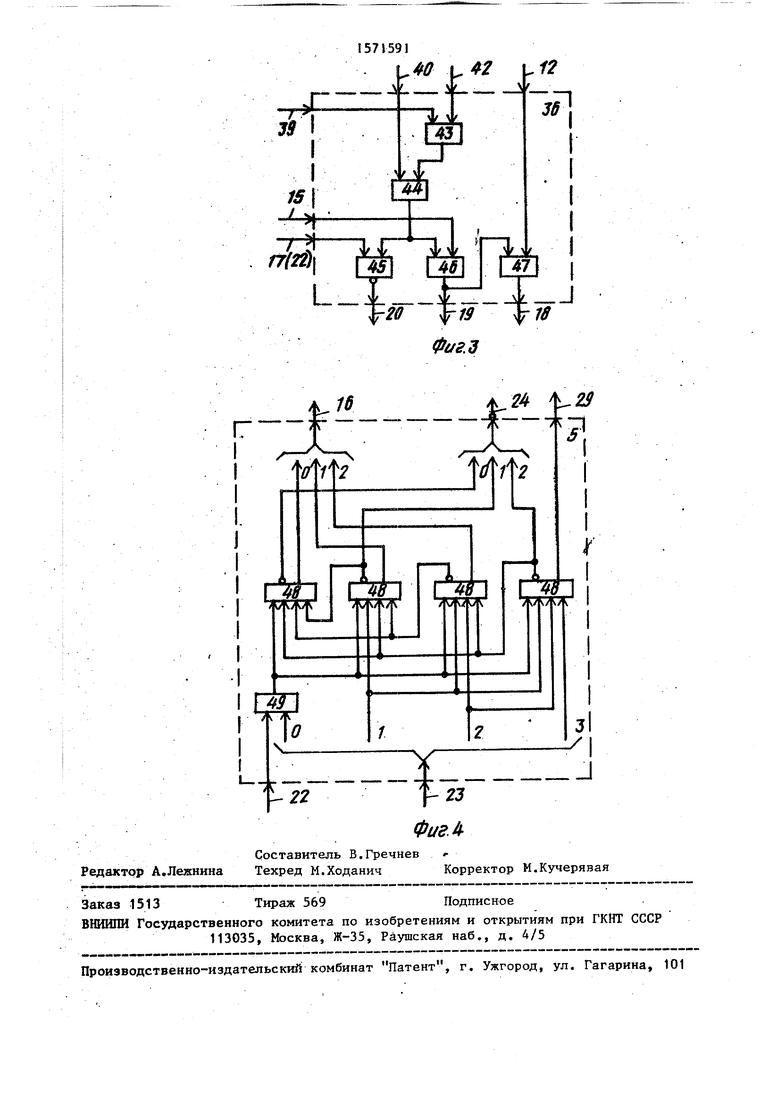

В дешифраторе 5 (фиг.4) нули кодируются 1. При установке на входе 22 О на выходе 16 формируется нулевой код, на выходе 24 - единичный, а на выходе 29 - О.

При установке на входе 22 1 дешифратор 5 функционирует в соответствии с табл.3 (при количестве разрядов информационного входа, равном четырем).

Если на i левых разрядах входа 23 установлены 1,то на (1-1)-м разряде выхода 16 формируется Т, а на остальных разрядах выхода 16 - О. На выходе 24 формируется обратный (инверсный) сформированному на выходе 16 коду код, кроме, второго разряда. На выходе 29 (2-м разряде выхода 24) формируется 1 (О) при установке на всех разрядах входа 23 и на входе 22 1. В остальных случаях на выходе 29 (2-м разряде выхода 24) формируется О (1).

В исходном состоянии устройства на входе 9 устанавливается сдвигаемый или нормализуемый двоичный код, на входе 10 - контрольный код побайтных сигналов четности, на входе

13- код величины сдвига, на входе

14- код направления сдвига. При установке на входе 14 О задается сдвиг вправо, а при установке на входе 14 1 - сдвиг влево.

На входе 22 устанавливается 1. В случае, если используются только логические сдвиги, на входах- 25 и 28 устанавливаются О.

Предположим, что на входе 13 установлен ненулевой код. .

При установке на входе 14 О на выход 1-го (i , 2, 3) коммутатора группы 2 передается код с выхода 19 (i-O-ro формирователя 1. Этот код суммируется по модулю два в i-м

0 логически сдвинутого вправо на вели15

0

5

0

5

0

5

0

5

чину, задаваемую кодом на вхоДе 13, N-разрядного кода относительно кода, установленного на входе 9. Сигнал четности 0-го байта формируется аналогично как и 1-го разряда с тем отличием, что на выход 0-го коммутатора группы 2 передается нулевой код с входа 28.

При установке на входе 14 1 (т.е. задается сдвиг влево) на выход 1-го (, 1, 2) коммутатора группы 2 передается код с выхода 19 (i+1)-ro формирователя группы 1.

Этот код суммируется по модулю два в i-м элементе группы 3 с кодом, сформированным на выходе 18 1-го формирователя группы 1. В формирователях группы 1 формируются сигналы ч четности в соответствии с приведенным выше алгоритмом функционирования узла группы 1. В результате на i-м разряде выхода 31 формируется сигнал четности i-ro байта логически сдвинутого на величину, задаваемую кодом на входе 13, N-разрядного кода относительно кода, установленного на входе 9. Сигнал четности 3-го байта формируется аналогично как и i-ro разряда с тем отличием, что на выход 3-го коммутатора группы 2 передается нулевой код с входа 25.

В обоих случаях значение (К) бита четности i-ro байта сдвинутого кода формируется в соответствии с алгоритмом К f + р, где f - значение четности выдвинутых бит байта, соседнего относительно i-ro байта сдвигаемого кода со стороны, противоположной направлению сдвига; р - значение четности оставшихся бит i-ro байта сдвигаемого кода. Сигналы со значением четности f и р формируются соответственно на выходах 19 и 18 узлов группы 1.

В рассмотренных случаях на входе 23 и выходе 15 устанавливается единичный код, на выходах 20 всех узлов группы 1 - 1, так как на выходе

16 формируется нулевой код. На выхо- де 29 формируется 1, на выходе 24 - код 110.

В результате на выходе 32 формируется 1. Значения сигналов на вы- ходах 29 и 32 не учитываются при установке на входе 13 кода, не равного нулевому.

При установке на входе 13 нулевого

кода уйлы группы 1 функционируют в соответствии с описанным выше алгоритмом с учетом того, что на выходе 15 дешифратора 4 устанавливается нулевой код. Формирование сигналов четности на выходе 31 осуществляется в рассматриваемом случае аналогично, как и при ненулевом коде на входе 13 На выходах 21 узлов группы 1 формиру ются сигналы признака нуля групп бит N-разрядного кода, установленных на входах 11. С помощью дешифратора 5 на йыходе 16 формируется управляющий код, под действием которого выход 20 узла групп 1, который является первым слева узлом и на входе 11 которого установлен код, не равный нулевому, разблокируется.

Выход 20 всех остальных узлов группы 1, кроме крайнего левого, блокируется путем формирования на нем 1

На выходе 20 крайнего левого узла группы 1 всегда устанавливается единица, если на входе И установлен нулевой код (см. описание функционирования узла группы 1). С помощью сигналов на выходе 24 и элементе И-Н 7 формируется сигнал четности старшей части кода нормализации, определяющей количество групп нулевых бит слева на входах 11.

Через элемент И-НЕ 6 передается сигнал четности младшей части нормализации, определяющей количество нулевых бит слева в первой ненулевой слева группе бит.

В результате на выходе 32 формируется сигнал четности для всего кода нормализации для кода, установленного на входе 9.

Если на входе 11 крайнего левого узла группы 1 установлен ненулевой код, то на выходе 16 формируется нулевой код, а на выходе 24 - единичный код. В результате на выход 32 передается сигнал четности кода количества нулевых бит слева кода, уста

5

5

0

5

0

5

0

5

новленного на входе 11 крайнего левого узла группы 1,

Если на входе 9 установлен нулевой код, то на выходе 16 также сформируется нулевой код, а на выходе 20 всех узлов группы 1 - единичный код. На выходе 24 сформируется код 110,

in II ч П

на выходе 29 - 1 ,

В результате на выходе 32 сформируется 1, что соответствует сигналу четности для кода нормализации, равному 10000 (при N 32, К 8).

Таким образом, обеспечивается формирование сигнала четности для кода нормализации.

Расширение класса решаемых задач устройства формирования сигналов четности достигается за счет формирования сигнала четности для кода нормализации.

Благодаря формированию сигнала четности кода нормализации обеспечивается возможность организации контроля по четности указанного шифратора кода нормализации с минимальными дополнительными аппаратными затратами. При этом обеспечивается контроль и выход признака нуля, так как сигнал четности кода нормализации формируется с учетом значений сигналов на выходе признака нуля, который является старшим разрядом выхода кода нормализации.

Формула изобретения

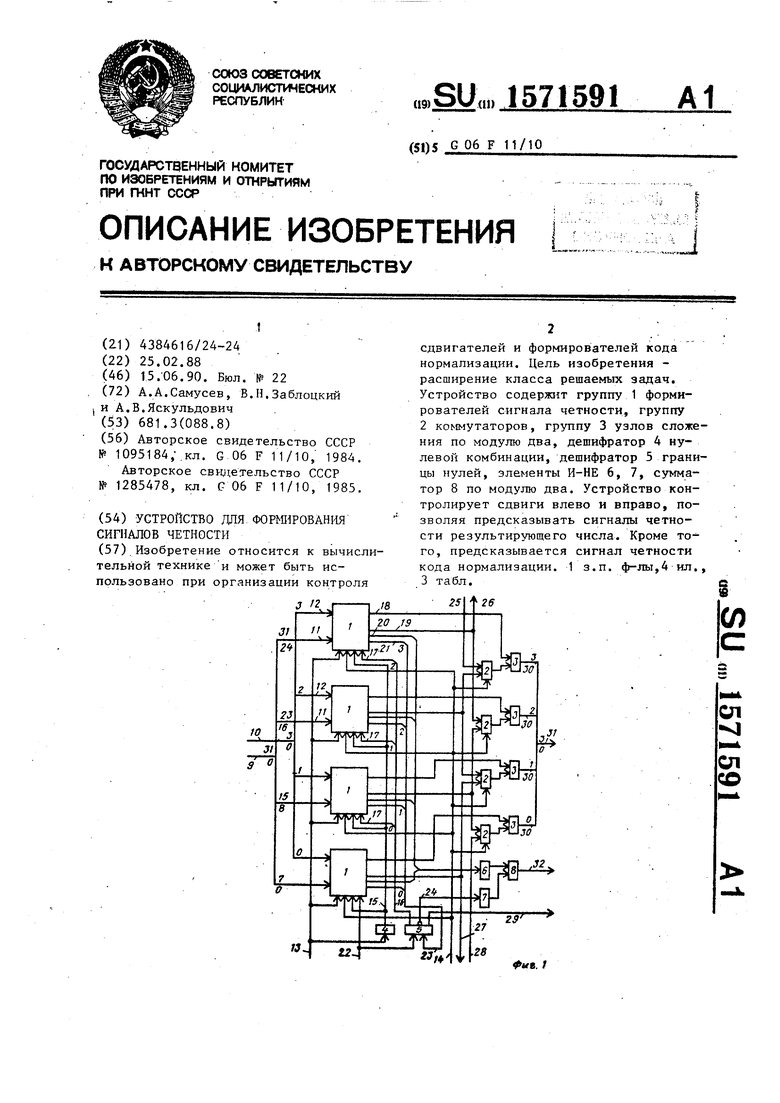

1. Устройство для формирования сигналов четности, содержащее группу формирователей сигнала четности и группу узлов сложения по модулю , два, причем информационные входы формирователей сигнала четности группы образуют группу информационных входов устройства, входы контрольных разрядов формирователей сигнала четности группы образуют группу входов контрольных разрядов устройства, отличающееся тем, что, с целью расширения класса решаемых задач, в него введены группа коммутаторов, дешифратор нулевой комбинации, дешифратор границы нулей, два элемента И-НЕ и сумматор по модулю два, причем вход задания величины сдвига устройства подключен к входам задания величины сдвига формирователей сигнала четнсг и группы и информационному входу дешифратора ну13

левой комбинации, выход которого подключен к входам считывания признаков четности выдвинутых бит формирователей сигнала четности группы, вход задания направления сдвига устройства подключен к входам задания направления сдвига формирователей сигнала четности группы и управляющим входам коммутаторов группы, выходы которых соединены с первыми входами соответствующих узлов сложения по модулю два группы, выходы которых образуют группу выходов устройства, вход считывания признака нечетности кода нормализации устройства подключен к входу считывания признака не- - четности кода нормализации первого формирователя сигнала четности группы и тактовому входу дешифратора границы нулей, 1-е прямые выходы которого соединены с входами считывания сигнала нечетности (i+1)-ro формирователя сигнала четности группы ( 1«-1,где m - число формирователей сигнала четности группы), m-й прямой выход дешифратора границы нулей является выходом признака нулевой информации устройства, выходы признака четности оставшихся бит формирователей сигнала четности группы соединены с вторыми входами соответствующих узлов сложения по модулю два группы, первый информационный вход первого коммутатора группы является первым входом расширения устройства, выход признака четности выдвинутых бит первого формирователя сигнала четности группы соединен с первым информационным входом второго коммутатора группы и является первым выходом расширения устройства, выход признака четности выдвинутых бит каждого j-ro формирователя сигнала четности группы (2 j Г п-1 ) соединен с первым информационным входом (j + + 1)-го коммутатора группы и вторым информационным входом (j-1)-го коммутатора группы, выход признака четности выдвинутых бит k-ro формирователя сигнала четности группы соедине с вторым информационным входом (k - - 1)-го коммутатора группы и являетс вторым выходом расширения устройства, второй информационный вход ra-rd коммутатора группы является вторым входом расширения устройства, выходы нечетности кода нормализации формирователей признака четности

1591

10

15

20

25

30

35

40

45

50

55

14

группы соединены с соответствующими входами первого элемента И-НЕ, инверсные выходы дешифратора границы нулей соединены с соответствующими входами второго элемента И-НЕ, выходы первого и второго элементов И-НЕ соединены с соответствующими входами сумматора по модулю два, выход которого является выходом признака четности кода нормализации устройства, выходы признака нулевой информации формирователей сигнала четности группы соединены с соответствующими разрядами информационного входа дешифратора границы нулей. I

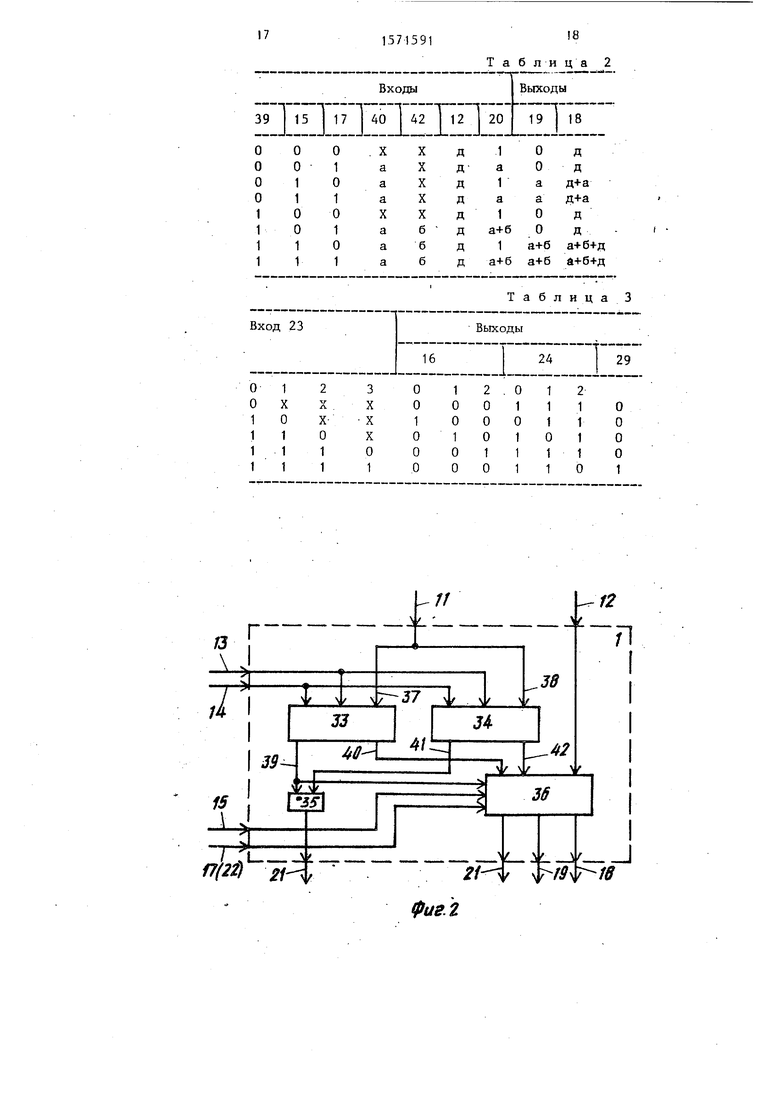

2. Устройство по п.1, о т л и - чающееся тем, что формирователь сигнала четности группы содержит три узла формирования сигнала четности и элемент И, причем выходы четности первого и второго узлов формирования сигнала четности и вход контрольного разряда формирователя подключены к информацией-, ным входам третьего узла формирования сигнала четности, выход признака нечетности кода нормализации которого является выходом признака нечетности кода нормализации формирователя, выходы признака четности оставшихся бит и выдвинутых бит третьего узла формирования сигнала четности являются соответственно выходами признаков четности оставшихся бит |И выдвинутых бит формирователя, выходы признака нулевой информации первого и второго узлов формирования сигнала четности соединены соответственно с первым и вторым входами элемента И, выход которого является выходом признака нулевой информации формирователя, входы задания направления и величины сдвига формирователя подключены соответственно к входам задания направления и величины сдвига первого и второго узлов формирования сигнала четности, младшие и старшие разряды информационного входа формирователя подключены к информационным входам первого и второго узлов формирования сигнала четности, вход считывания признака четности выдвинутых бит формирователя и вход считывания признака не- че,тности кода нормализации формирователя подключены соответственно к входу считывания признака четности

15157159116

выдвинутых бит и входу считывания третьего узла формирования сигнала признака нечетности-кода нормализаци 1 четности.

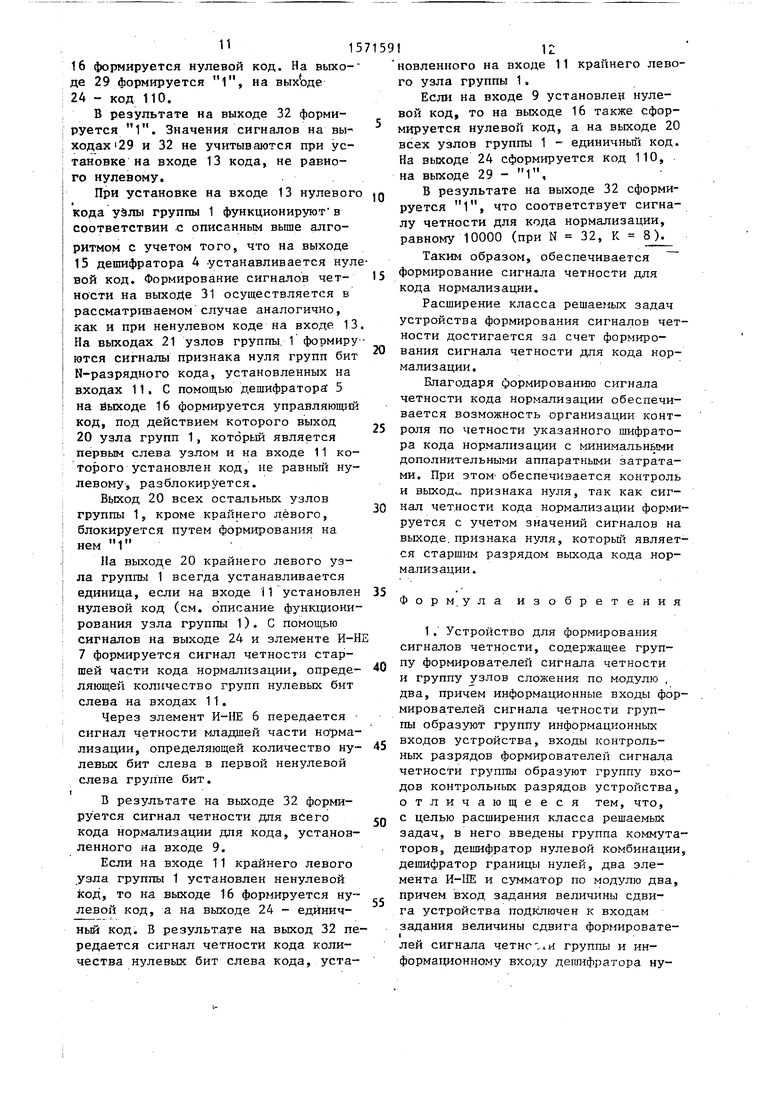

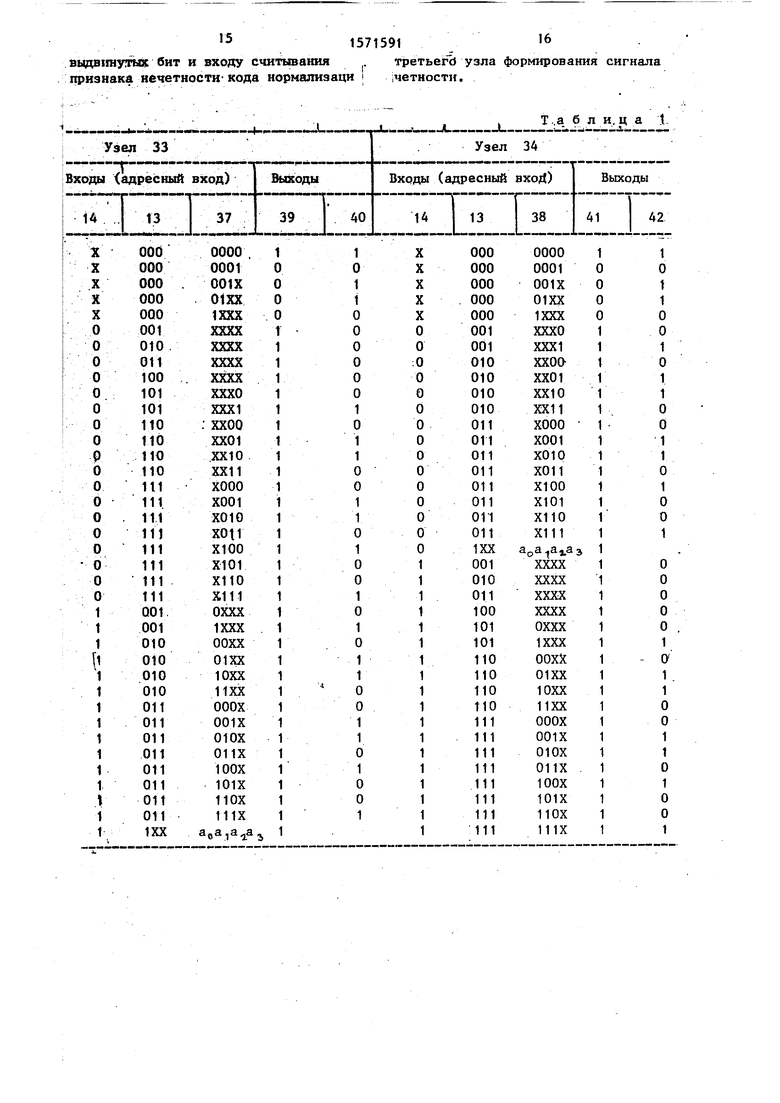

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1580368A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1658155A1 |

| Модуль для сдвига операндов | 1988 |

|

SU1617434A1 |

| Устройство для сдвига операндов | 1987 |

|

SU1481741A1 |

| Устройство для сдвига информации с контролем | 1985 |

|

SU1325481A1 |

| Устройство для формирования сигнала четности при сдвигах двоичных кодов | 1987 |

|

SU1481770A1 |

| Устройство для предсказания четности результата сдвигателя | 1989 |

|

SU1730628A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

Изобретение относится к вычислительной технике и может быть использовано при организации контроля сдвигателей и формирователей кода нормализации. Цель изобретения - расширение класса решаемых задач. Устройство содержит группу 1 формирователей сигнала четности, группу 2 коммутаторов, группу 3 узлов сложения по модулю два, дешифратор 4 нулевой комбинации, дешифратор 5 границы нулей, элементы И-НЕ 6, 7, сумматор 8 по модулю два. Устройство контролирует сдвиги влево и вправо, позволяя предсказывать сигналы четности результирующего числа. Кроме того предсказывается сигнал четности кода нормализации. 1 з.п. ф-лы, 4 ил., 4 табл.

Фиг. г

ЈL

16

22

Редактор А.Лежнина

Составитель В.Гречнев Техред М.Ходанич

.

У.У

Фив.З

24 Я

4

1-23

J

0#г4

Корректор М.Кучерявая

| Устройство для сдвига информации с контролем | 1983 |

|

SU1095184A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля блока сдвиговых регистров | 1985 |

|

SU1285478A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-02-25—Подача