сд

О5 00

Изобретение относится к вычислительной технике и может быть использовано при создании высокопроизводительных вычислительных систем.

Известно устройство для нормализации двоичных чисел, содержащее матрицу из элементов памяти, логические элементы И, ИЛИ и выполняющее сдвиг входной информации параллельно на требуемое число разрядов за один такт fTj.

Однако данное устройство для нормализации двоичных чисел содержит большое количество оборудования.

Известно устройство для нормализации чисел, содержащее последовательЕго соединенные элементы логи|ческих уровней, каждый из которых содержит анализаторы содержимого на нуль, деимфраторы величины сдвига, шифратор и элемент И 2 .

Недостатками этого устройства являются большой объем аппаратурных затрат и зависимость времени выполнения операции нормсьпизации от разрядности нормализуемого числа.

Наиболее близким по технической сущности к изобретению является устройство для нормализации двоичных чисел, содержащее узел анализа, два дешифратора,, два шифратора, два сдвигателя и регистр порядка, причем информационный вход первого сдви гателя соединен с входом узла анализа и входом устройства,выход узла анализа соединен с входом первого дешифратора, выход которого соединен с входом первого шифратора, выход которого соединен с входом регистра порядка и управляющим входом первого сдвигателя, первый выход которого соединен с информационным входом второго сдвигателя, управляющий вход которого соединен с входом регистра порядка и выходом второго шифратора, вход которого соединен с выходом первого дешифратора, вход которого соединен с вторым выходом, первого сд-вигателя, выходы второго сдвигателя и регистра порядка являются первым и вторым выходами устройства 3.

Недостатком данного устройства является невысокое быстродействие.

Цель изобретения - повышение быстродействия устройства для нормализации двоичных чисел.

Поставленная цель достигается тем, что устройство для нормализации двоичных чисел, содержащее узел анализа, сдвигатель, регистр порядка,шифратор, причем вход устройства соединен с информационным входом сдвигателя и входом узла анализа, выход шифратора сообщен с управляющим входом сдвигателя и входом регистра порядка, выходы сдвигателя и регистра порядка являются COOTветст- i венно первым и вторым выходами устройства содержит преобразователь двоичного кода тетрад в код количест ва нулевых старших разрядов в тетрадах и коммутатор, причем вход узла анализа соединен с входом преобразов.ателя двоичного кода тетрад в код количества нулевых старших разрядов в тетрадах, выход которого соединен с информационным входом коммутатора, управляющий вход которого соединен с выходом шифратора, выход коммутатора соединен с входом регистра порядка и управляющим входом сдвигателя, вход шифратора соединен с выходом узла анализа.

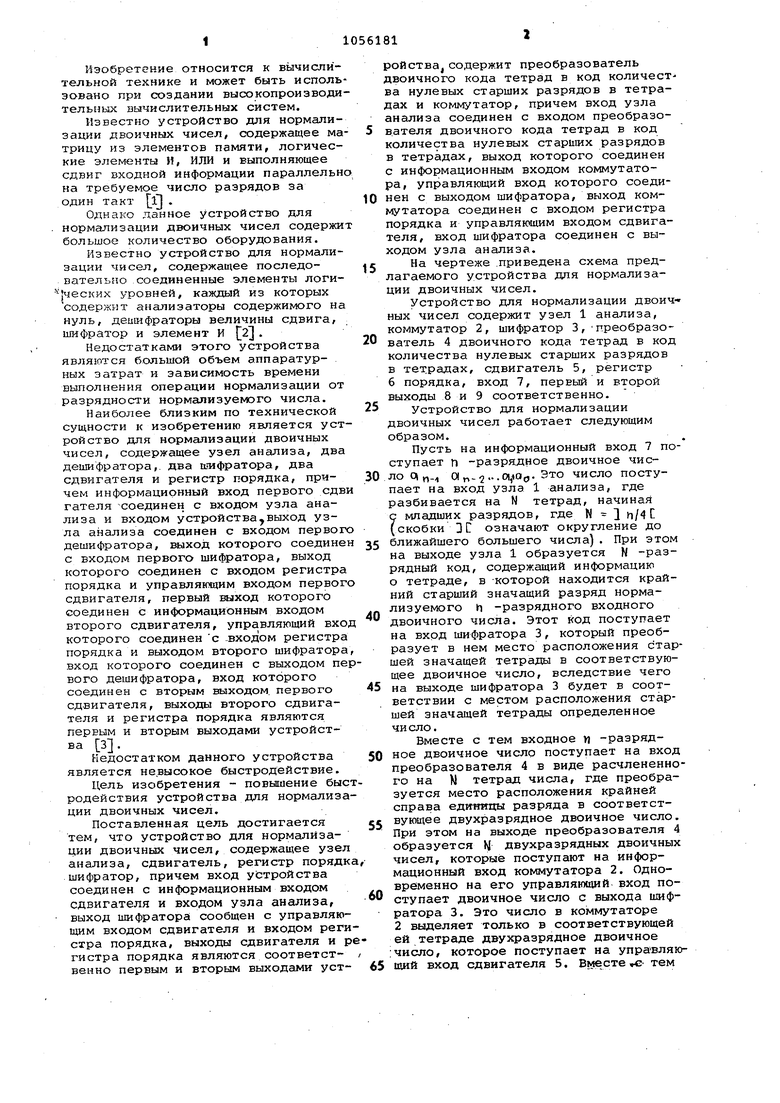

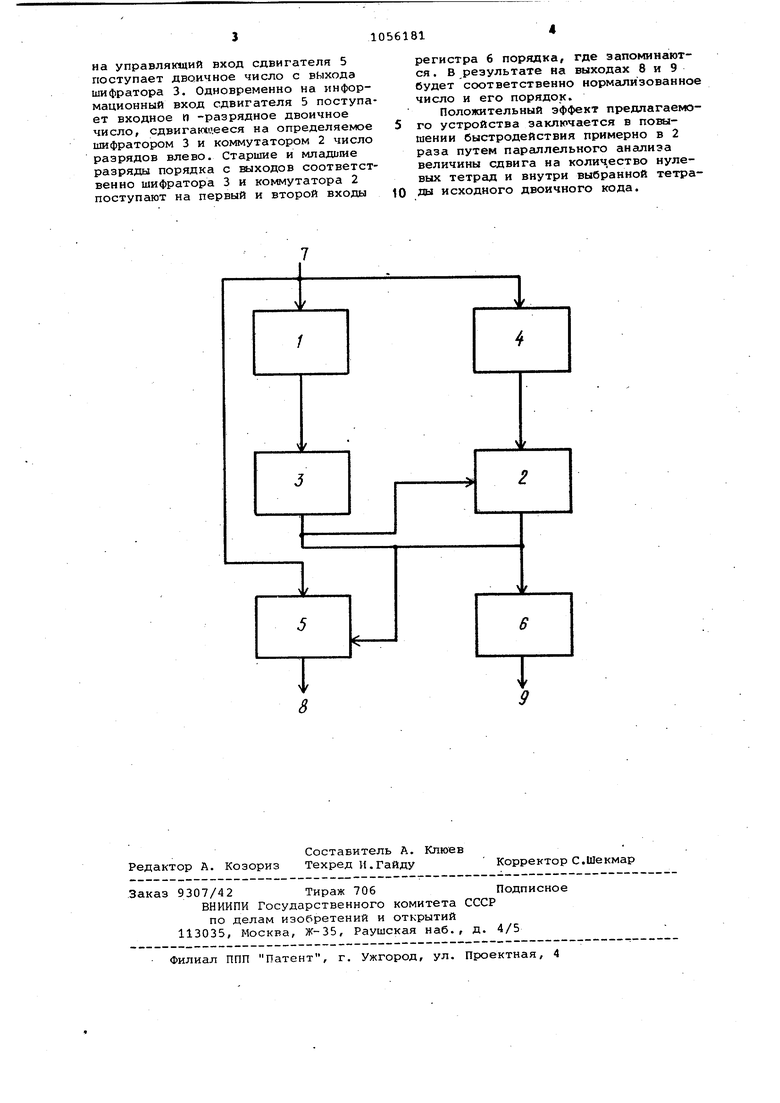

На чертеже .приведена схема предлагаемого устройства для нормализации двоичных чисел.

Устройство для нормализации двоич ных чисел содержит узел 1 анализа, коммутатор 2, шифратор 3,преобразователь 4 двоичного кода тетрад в код количества нулевых старших разрядов в тетрадах, сдвигатель 5, регистр 6 порядка, вход 7, первьай и второй выходы 8 и 9 соответственно.

Устройство для нормализации двоичных чисел работает следующим образом.

Пусть на информационный вход 7 поступает п -разрядное двоичное число Q „. olv,-.2 -oiiOo- число поступает на вход узла 1 анализа, где разбивается на N тетрад, начиная с младших разрядов, где N H/t С (скобки 3 С означают округление до ближайшего большего числа). При этом на выходе узла 1 образуется N -разрядный код, содержащий информацию о тетраде, в которой находится крайний старший значащий разряд нормализуемого и -разрядного входного двоичного числа. Этот код поступает на вход шифратора 3, который преобразует в нем место расположения старшей значащей тетрады в соответствующее двоичное число, вследствие чего на выходе шифратора 3 будет в соответствии с местом расположения старшей значащей тетрады определенное число.

Вместе с тем входное ц -разрядное двоичное число поступает на вход преобразователя 4 в виде расчлененного на N тетрад числа, где преобразуется место расположения крайней справа единицы разряда в соответствующее двухразрядное двоичное число. При этом на выходе преобразователя 4 образуется двухразрядных двоичных чисел, которые поступают на информационный вход коммутатора 2. Одновременно на его управляющий вход поступает двоичное число с выхода шифратора 3. Это число в коммутаторе 2 выделяет только в соответствующей ей тетраде двухразрядное двоичное :число, которое поступает на управляющий вход сдвигателя 5. Вместе С тем

на управляющий вход сдвигателя 5 поступает двоичное число с выхода шифратора 3. Одновременно на информационный вход сдвигателя 5 поступает входное п -разрядное двоичное число, сдвигакчдееся на определяемое шифратором 3 и коммутатором 2 число разрядов влево. Старшие и младише разряды порядка с выходов соответственно шифратора 3 и коммутатора 2 поступают на первый и второй входы

регистра 6 порядка, где запоминаются . В результате на выходах 8 и 9 будет соответственно нормализованное число и его порядок.

Положительный эффект предлагаемого устройства заключается в повышении быстродействия примерно в 2 раза путем параллельного анализа величины сдвига на колич.ество нулевых тетрад и внутри выбранной тетрады исходного двоичного кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нормализации двоичных чисел | 1979 |

|

SU783792A1 |

| Устройство для сдвига данных | 1983 |

|

SU1140113A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| Устройство для нормализации чисел | 1986 |

|

SU1307454A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Устройство для нормализации двоичных чисел | 1985 |

|

SU1310805A1 |

УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ ДВОИЧНЫХ ЧИСЕЛ, содержащее узел анализа, сдвигатель, регистр порядка, шифратор, причем вход устройства соединен с информационным входом сдвигателя и входом узла анализа, выход шифратора соединен с управлякацим входом одвигателя и -входом регистра порядка, выходы сдвигателя и регистра порядка являются соответственно первым и вторым выходами устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит преобразователь двоичного кода тетрад в код количества нулевых старших разрядов в тетрадах и коммутатор, причем вход узла анализа соединен с входом преобразователя двоичного кода тетрад в код .количества нулевых старших разрядов в тетрадах, выход которого соединен с информацион ным входом коммутатора, управляющий S вход которого соединен с выходом сл шифратора, выход коммутатора соединен с входом регистра порядка и с управлявшим входом сдвигателя, вход шифратора соединен с выходом узла анализа.

8

Авторы

Даты

1983-11-23—Публикация

1982-06-02—Подача