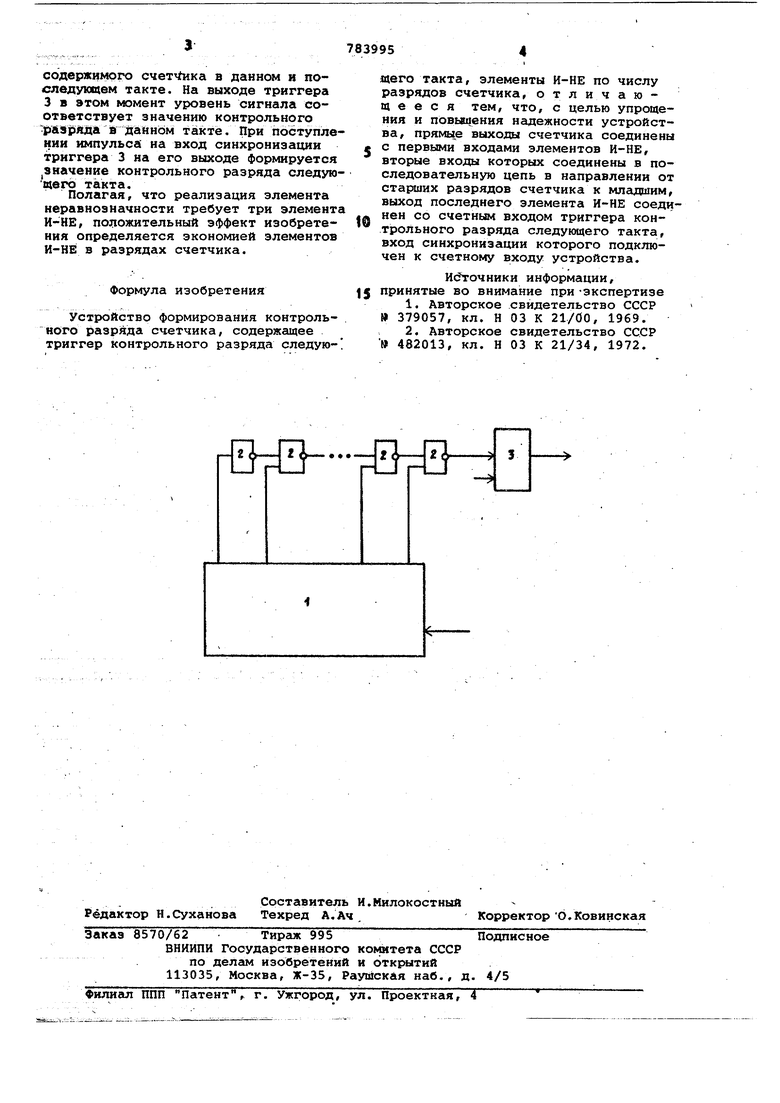

Изобретение относится к области импульсной техники и может быть использовано для построения схем контроля счетчиков. Известно устройство l, содержа щее элементы И, по числу разрядов счетчика, ИЛИ и НЕ. . Недостатком этого устройства является сложность, определяемая боль шим числом связей, и низкая степень унификации. Наиболее близким техническим решением к данному является устройство 2, содержащее п-разрядный двоичный счетчик, п+2 элемента неравно значности, первые входы И элементов неравнозначности соединены с выхода ми триггеров счетчика, по вторым вх дам соединенные в последовательную цепь в направлении от старших разрядов к младшим, входы п+1-го элемента неравнозначности соединены с выходами п-го и триггера контрольног разряда, а входы п+2-го элемента не равнозначности - с выходом п+1-го и счетного входа устройства, а его вы ход является выходом устройства 2 3 Недостатком данного устройства является его- сложность и, как следствие , низкая надежность. Целью изобретения является упрощение и повьииение надежности устройства. Поставленная цель достигается тем, что в устройстве, содержащем триггер контрольного разряда следующего такта, элементы И-НЁ по числу разрядов счетчика, выходы счетчика соединены с первь ш входами элементов И-НЕ, вторые входы которых соединены в последовательную цепь в направлении от старшего разряда к младшему, выход, последнего элемента И-НЕ соединен со счетным входом триггера контрольного разряда следующего акта, вход синхронизации которого соединен со счетным входом устройства. На чертеже представлена схема устройства . Устройство содержит контролируемый счетчик 1, элементы И-НЕ 2 и триггер 3 контрольного разряда следующего такта. Принцип работы устройства заключается в следующем. При поступлении импульса счета на вход счетчика 1 элементами И-НЕ 2 на счетном входе триггера 3 формируется логический уровнь, соответствующий сумме по mod 2 сумм единиц

содержимого в данном и последующем такте. На выходе триггера 3 в этом момент уровень сигнала соответствует значению контрольного в данном такте. При поступлеС1ии импульса на вход синхронизации триггера 3 на его выходе формируется значение контрольного разряда следующего такта.

Полагая, что реализация элемента

неравнозначности требует три элемента И-НЕ, положительный эффект изобретения определяется экономией элементов И-НЁ в разрядах счетчика.

Формула изобретения

Устройство формирования контрольного разряда счетчика, содержащее триггер контрольного разряда следую«его такта, элементы И-НЕ по числу разрядов счетчика, отличающееся тем, что, с целью упрощения и повышения надежности устройства, прямы,е выходы счетчика соединены с первыми входами элементов И-НЕ, вторые входы которых соединены в последовательную цепь в направлении от стаЕЯИих разрядов счетчика к младшим, выход последнего элемента И-НЕ соединен со счетным входом триггера контрольного разряда следующего такта, вход синхронизации которого подключен к счетному входу устройства.

Ниточники информации, принятые во внимание при -экспертизе

1.Авторское свидетельство СССР 379057, кл. Н 03 К 21/00, 1969.

2.Авторское свидетельство СССР 482013, кл. Н 03 К 21/34, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик с контролем на четность | 1981 |

|

SU1010728A1 |

| Устройство для сдвига со встро-ЕННыМ КОНТРОлЕМ | 1979 |

|

SU809386A1 |

| Устройство для спектрального анализа | 1984 |

|

SU1241256A1 |

| Счетное устройство | 1984 |

|

SU1210221A1 |

| Устройство для сравнения чисел | 1980 |

|

SU960797A1 |

| Устройство для контроля обработки двоичной информации | 1982 |

|

SU1089581A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для сравнения чисел | 1979 |

|

SU842791A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| @ -Разрядный счетчик в коде Грея | 1982 |

|

SU1070695A1 |

.лтИ7

Авторы

Даты

1980-11-30—Публикация

1979-02-07—Подача