мента ИЛИ-НЕ и ()-M входом сумматора по модулю два, (N+8)-ft и ()-ft входы которого соединены соответственно с вьосодами третьего и четвертого элементов И-НЕ, первый вход пятого элемента И-НЕ соединен с выходом триггера контрольного разряда и (N-flO)-M входом сумматора по модулю два, (N+n)-ft вход которого соединен с выходом четвертого элемента ИЛИ-НЕ и управлякщим входом дешифратора, второй вход кода задания режима работы устройства соединен с первыми входами третьего и четвертого элементов ИЛИ-НЕ и с первыми входами шестого и седьмого элементов И-ЙЕ, тактовьй вход устройства соединен с вторь ш входами третьего и четвертого элемен 10 1 тов ИЛИ-НЕ и с синхронизирующим вхо- . дом триггера контрольного разряда, третий вход кода задания режима работы устройства соединен с третьим входом третьего элемента ИЛИ-НЕ и с вторьм входом дешифратора, выход шестого элемента И-НЕ соединен с входом установки в 1 триггера контрольного разряда, вход установки в которого соединен с вторым входом шестого элемента И-НЕ и выходом седьмого элемента И-НЕ, второй вход которого является контрольным входом устройства, информационный вход триггера .контрольного разряда соединен с выходом сумматора по модулю два и является контрольным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем | 1988 |

|

SU1508287A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля на четность двоичной информации | 1981 |

|

SU1015388A1 |

| Устройство для контроля принимаемой информации | 1981 |

|

SU1023333A1 |

| Устройство для сдвига со встро-ЕННыМ КОНТРОлЕМ | 1979 |

|

SU809386A1 |

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Устройство для определения амплитудно-частотных характеристик объектов | 1989 |

|

SU1689876A1 |

| Устройство для задержки информации с контролем | 1990 |

|

SU1795442A1 |

| Устройство для контроля сумматоров | 1983 |

|

SU1242961A1 |

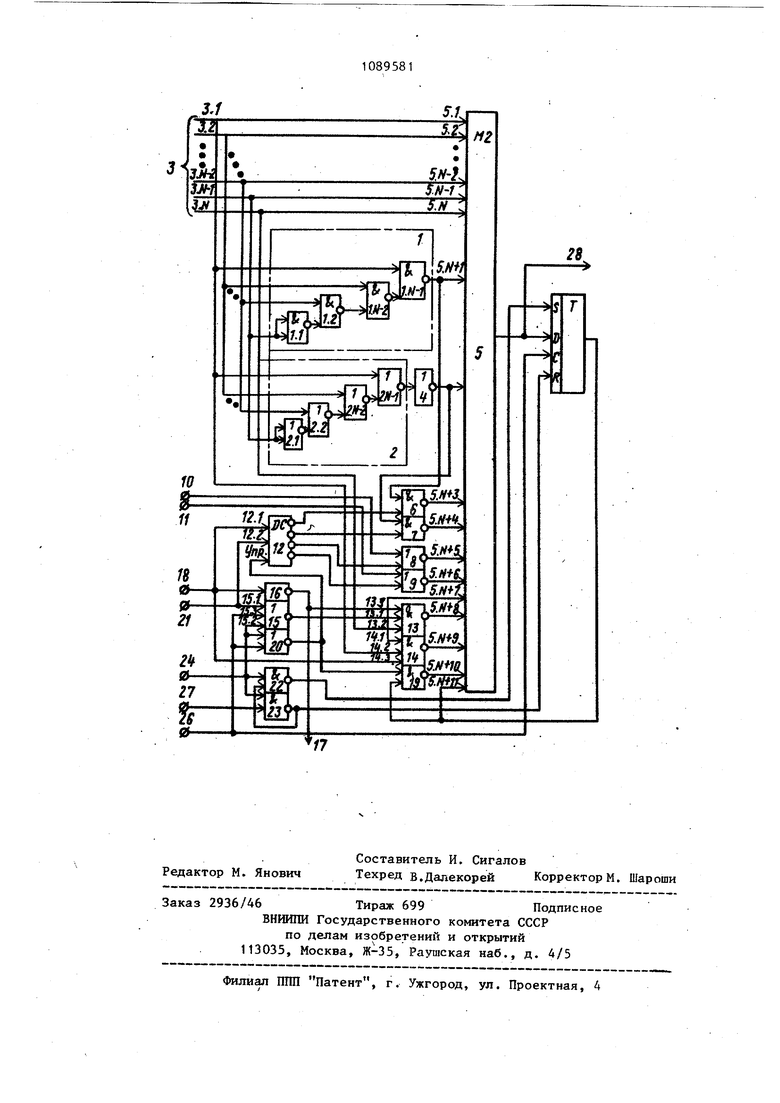

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОБРАБОТКИ ДВОИЧНОЙ ИНФОРМАЦИИ, содержащее сумматор по модулю два, триггер контрольного разреза и группу элементов И-НЕ, причем каждый i-й контролируемый вход устройства (где i- от 1 до (N-1), а N - количество разрядов обрабатываемой информации) соединен с первым входом, соответствукщего элемента И-НЕ группы и с соответствующим входом сумматора по модулю два, выход i-ro элемента И-НЕ группы соединен с вторым входом (i+1)-ro элемента И-НЕ группы, (N-l)-ft контролируемый вход устройства соединен с вторым входом первого элемента И-НЕ группы, N-й вход устройства соединен с N-M входом сумматора по модулю два, отличающееся тем, что с цепью расширения области применения за счет обеспечения контроля прямого и обратного счета, прямого и обратного сдвига, в .устройство введены группа элементов ИЛИ-НЕ, дешифратор, два элемента ИЛИ, четыре элемента ШШ-НЕ, семь элйМентов И-НЕ и два элемента НЕ, причем каждый i-й контролируемый вход устройства соединен с первым входом соответствующего элемента ИЛИ-НЕ группы, выход i-ro элемента ШШ-НЕ группы соединен с вторым .в содом (i+1)-ro элемента ИЛИ-НЕ группы, (М-1)-й контролируемый вход устройства соединен с вторым входом первого элемента ИЛИ-НЕ группы, выход (N-l)-ro элемента И-НЕ группы соединен, с (N+1)-M .входом сумма.тора по модулю два и с первым входом первого элемента И-НЕ, выход (N-l)-ro элемента ИЛИ-НЕ через первый элемент НЕ соединен с первым входом второго элемента И-НЕ и с (N+2)-M входом сумматора по модулю два, первые i входы первог о и второго элементов ИЛИ-НЕ соединены соответственно с (Л входами прямого и обратного сдвига устройства, выходы первого и второго элементов И-НЕ, первого и второго элементов ИЛИ-НЕ соединены соответственно с ()-M, (N+4)-M, (N+5)-M и (N+6)-M входами сумматора по модулю два, а их вторые входы соедине00 ны соответственно с первым, вторым, со третьим и четвертым выходами дешифСП ратора, первые входы третьего и чет00 вертого элементов И-НЕ сое.гегнены соответственно с N-M и первым контролируемыми входами устройства, второй вход четвертого элемента И-НЕ соединен с первым входом кода задания режима работы устройства, первым входом дешифратора и входом второго элемента НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ и является управляющим выходом устройства, третьи входы третьего и четвертого элементов И-НЕ объединены и соединены с выходом третьего эле

Изобретение относится к вычислит,ельной технике и может быть испольfзовано при разработке многорежимных

устройств обработки двоичной информции со встроенньм контролем, например двоичных счетчиков с реверсивны счетом или регистров со сдвигом и параллельной установкой.

Известны устройства контроля счечиков или регистров, содержащее счетчик или регистр, схему предсказания четкости, триггер йля запоминания четкости, схему свёртки по модулю два Cl3Однако известные устройства не обеспечивают контроль многореятмных блоков обработки информации.

Известные устройства используют формирование свертки по модулю два для будущего такта работы и обеспе.чивают выработку сигнала коррекции свертки,запоминание и сложение его по модулю два с текущим значением свертки.

Наиболее близким по технической сущности к предлагаемому является устройство для проверки четкости двоичного регистра С -3Данное устройство не обеспечивает контроля работы счетчика в режме обратного счета, в- режиме записи

а также не позволяет контролировать работу сдвиговых реверсивных регистров и требует для контроля наличия инверсньк выходов у контролируемого устройства, что значительно сужает область применения известного устройства. .

Цель изобретения - расширение области применения устройства за счет обеспечения.возможности контроля как прямого, так и обратного сдвига.

Поставленная цель достигается тем, что в устройство для контроля обработки двоичной информации, содержащее сумматор по модулю два, контролируемого разряда и группу элементов И-НЕ, причем междый i-й контролируемый вход устройства (где i , от 1 до (N-1), а N - количество разрядов обрабатьюаемой информации) соединен с первым входом соответствующего элемента И-НЕ группы и с соответствующим входом сумматора по модулю два, выход i-ro элемента И-НЕ группы соединен с вторым входом (i+1)-ro элемента И-НЕ группы, (N-1)-й контролируемый вход устройства соединен с вторым входом первого элемента И-НЕ группы, N-й вход устройства Соединен с N-M входом сумматора по модулю два, введены группа элементов ЙЛИ-НЕ, дешифратор, четьфе элемента ИЛИ-НЕ, семь элементов И-НЕ и два элемента НЕ, причем каждый i-й контролируемый вход устройства соединен с первым входом соответствующего элемента ИЛИ-НЕ группы, выход i-ro элемента ИЛИ-НБ группы соединен с вторым входом (i-t-l)-ro элемента ИЛИ-НЕ группы, (Ы-1)-й контролируемый устройства соединен с вторьм входом первого элемента ИЛИ-НЕ группы, выход (N-l)-ro элемента И-НЕ группы соединен с (N+1)-M входом сумматора по модулю два и с первым входом первого элемента И-НЕ, выход (N-1)-го элемента ИЛИ-НЕ группы через первый элемент НЕ соединен с первым входом второго элемента И-НЕ и (N+2)-M входом сумматора по модулю два,первы входы первого и второго элементов ИЛИ-НЕ соединены соответственно с , входами первого и обратного сдвига устройства, выхрды первого, вторЬго элементов И-НЕ, первого, второго элементов ШШ-НЕ соединены соответственно с (N+3)-M, (N+4)-M,(N+5)-M (N+6)-M входами сумматора по модулю два, а их вторые входы соединены соответственно с первым, вторым, третьим и четвертым выходами дешифратора, первые входы третьего и четвертого элементов И-НЕ соединены соответственно е N-M и первьм контро лируемыми входами устройства, второй вход четвертого элемента И-НЕ соединен с первым входом кедов задания режима работы устройства, первым вхо дом дешифратора и входом второго эле мента НЕ, выход которого соединен с вторым входом третьего элемента И-НЕ и является управляющим выходом устро ства, третьи входы третьего и четвер того элементоа И-НЕ обтьединены и сое динены с выходом третьего элемента ИЛИ-НЕ и (N+7)-M входом сумматора по модулю два, (Н+8)-й и (Ы+9)-й входы которого соединены соответственно с вьпсодами третьего и четвертого элементов И-НЕ, первый вход пятого элемента И-НЕ соединен с выходом триггера контрольного разряда и (N+10)-M входой сумматора по модулю два, , (Я+Ю-й вход которого соединен с вы ходом четвертого элемента ИЛИ-НЕ и управляющим входом дешифратора, вто- рой вход задания кода режима работы устройства соединен с первыми входам третьего и четвертого элементов ИЛИ-НЕ и с первыми входами шестого . и седьмого элемейтов И-НЕ, тактовьй вход устройства соединен с вторыми входами третьего и четвертого элементов -ИЛИ-НЕ и с синхронизирующим входом триггера контрольного разряда, третий вход задания кода режима устг- ройства соединен с третьим входом третьего элемента ШШ-НЕ и с вторым входом дешифратора, выход шестого элемента И-НЕ соединен с входом установки в 1 триггера контрольного разряда, вход установки в О которого соединен с вторым входом шестого элемента И-НЕ и выходом седьмого элемента И-НЕ, второй вход которого .является контрольным входом устройства, информадионньй вход триггера контрольного разряда соединен с выходом сзгмматора по модулю два и является контрольным выходом -устройства. Сущность изобретения заключается в том, что при контроле счета йпи сдвига коррекция четности в режиме обратного счета или обратного сдвига производится аналогично коррекции в режиме прймого счета или сдвига при использовании одного и того же сумматора по модулю два как для формирования контрольного разряда еледующего состояния, так и .для вьработки контрольного сигнала, путем ком- : пенсации в каждом режиме работы счетчика или регистра.сигналов на входе блока свертки, не являющихся необХОДИМЫШ1 в данном работы для вьфаботки контрольного сигнала или контрольного разряда. На чертеже пр(бяставлена блок-схема предлагаемого устройства для контроля N-разрядного блока обработки информации (двои:чного счетчика или регистра сдвига). Устройство содержит группы 1 и 2 з (N-1) элементов соотйетственно И-НЕ и ЮШ-НЕ, первые входы которых соединены с шиной 5 контролируемых входов устройства (первый вход устройства - с входом (Я-1)-го элемента, второй вход - с входом (N-2)-ro элемента,.,.., (Н-1)-й вход - с входом первого элемента). По вторым входам элементы каждой из групп 1 и 2 соединены последовательно в направлении от первого элемента группы к (N-l)-y. Второй и первый входы первого элемента каждой из групп 1 и 2 соединены. Выход (N-l)-rio элемента группы 2 с.оединен с элементом ЙЕ 4. Контролируемые входы устройства соединены с N входами сумматоров 5 по модулю два, (Н+1)-й вход которог соединен с выходов (N-l)-ro элемента И-НЕ группы 1 и первым входом элемента И-НЕ 6. Выход элемента НЕ 4 соединен с (К+2)-м входом сумматора 5 и пЕрвьм входом элемента И-НЕ 7. Первые входы элементов ИЛИ-НЕ 8 и 9 соединены соответственно с входами 10 и 11 прямого и обратного сдвига устройства. Вторые входы элементов И-НЕ 6 и 7 и ИЛИ-НЕ 8 и 9 соединены с выходами соответственно с 1-го по 4-й дешифратора 12, а их входы с входами соответственно с (N+3)-ro по (N+6)-и сумматора 5, (К+7)-й вход которого соединен с первыми входами элементов И-НЕ 13 и 14 и выходом эле мента ИШ-НЕ 15. Вторые входы элемен тов И-НЕ 13 и 14 соединены соответственно с N-M и первым контролируемым входами, третий вход элемента И-НЕ 13 соединен с выходом элемента НЕ 16 и является управляющим выходом 17 устройства, .третий вход элемента И-НЕ 14 соединен с входом элемента НЕ 16, первым адресным входо 11 десшфратора и является входом 18 реж ма работы устройства, выходы элементов И-НЕ 13 и 14 соединены соответственно (N+8)r-M и (N+9)-M входами сумматора 5, (N+10)-и и (К-И1)-й входы которого соединены соответственно с выходом и входом элемента И-НЕ 19. Втсфой вход элемента 19 соединен с выходом элемента ШШ-НЕ 20 и управпякнщм входом дешифратора 12, второй адресный вход которого соединен с первьм входом элемента ИЛИ-НЕ 15 и входом 21 режима рабо-чы устройства. Второй вход элемента 15 соединен с первыми входами И-НЕ 20, 22 и 23 и входом 24 режима работы устройства, третий вход элемента 15 соединен с вторым входом элемента 20, тактовым входом триггера 25 конт рольного разряда и тактовым входом 26 устройства, контрольньй вход 27 которого соединен с вторым входом элемента И-НЕ 23. Выходы элементов И-НЕ 22 и 23 соединены соответственно с входами установки л О триггера 25, ин формационный вход которого соединен с выходом сумматора 5 и контрольным выходом 28 устройства выход триггера 2 соединен с (N+11)-M входом сумматбра 5. Выход элемента И-НЕ 23 соединен с вторым входом элеМента И-НЕ 22. . При контроле реверсивного счетчика его входы режима счета, разрешения параллельной записи и синхронизации соединяют соответственно с входами18, 24 и 26 устройства, а выходы счетчика - с шиной 23 контрoлиpye ыx входов. При наличии у проверяемого счетчика двух входов синхронизации (для прямого и обратного счета) разрешение прохождения них тактовых сигналов с входа 26 в зависимости от режима (прямой или обратный счет) осуществляется с помощью сигналов на входе 18 и выходе 17 При контроле Д1еверсивного регистра сдвига его входы режима сдвига разрешения .параллельной записи, син хр онизации, последовательной информации прямого сдвига, последовательной информации о,братного сдвига соеданяются соответственно с входами 18, 24, 26, 10 и 11 устройства, а выходы регистра - с ошной 3 контрояируеьаж входов. Устройство обеспечивает контроль при работе в пяти режимах, определяемых пoтeнlщaлa 0I О и t на входах кодов режима 18, 21 и 24: прямой счет (на входе 18 уровень О, на входе 21 уровень 1, на входе 24 уровень О); обратный счет (на входах 18 и 21, уровень 1, на входе 24 - уровень О); сдвиг в сторону старших разрядов, сдвиг влево, шш прямой сдвиг (на входе 18, 21, 24 уровень 0)| сдвиг в сторону мпадпмх разрядов, сдвиг вправо ипи обратный сдвиг (на входе 18 уровень 1, на входах 21 и 24 уровень О); параллельная запись (на входе 24 уровень В режиме контроля прямого счета тактовые импульсы с входа 26 поступают на входы синхронизации триггера 25 и контроп1фуемого счетчика. В отрицательный полупериод тактового сигнала уровень 1 на выходе элемента ШШ-НЕ 20 разрешает работу дешифратора 12 и прохождение сигнала с триггера 25 на вход (N+10) сумматора 5 через элемент И-НЕ 19. Уровень О на выходе 12.3 дешифратора 12 и втором входе элекгента И-НЕ 6 запре1цает прохождение сигнала ,с выхода (N-l)-ro элемента группы 1 элементов И-НЕ на (N+3)-ft вход сумматора (на (N+3)-M входе уррйень 1) Уровень 1 на остальных выходах дешифратора 12 и входах элементов И-НЕ 7 и ИЛИ-НЕ 8 и 9 разрешает прохояздение сигнала с выхода элемента НЕ 4 на вход (N+4) с матора 5 и создает уровень О на его входах (N+5) и (N+6) независимо от Уровней сигналовна входах 10 и 11. Уровень 1 на входе 21 формирует уровень О на вь1хЬде элемента ИЛИ-НЕ 15 и первых входах элементов И-НЕ 13 и 14, что обеспечивает на входах (N+8) и (N+9) сумматора уровень 1, а на входе (N+7) - уровень . Таким образом, на входы сумматора 5 поступают: на 1,...N-ft входы - код текущего состояния счетчика е пшны 3 на (М+1)-и вход - сигнал,сформированный 1-м,...,(N-I)-M элементами И-НЕ группы 1 и представляющий собой свертку До модулю два переносов счетчика при прямом свете, которые должны возникнуть при следующем тактовом ишульсе (если состояние i-ro разрада счетчика после К-го тактового импульса, то последовательность 1,К Z.K 1|К 3,,К Л к-- а-,к при Ap MOJyi счете переносы соответстовенно в 1,2,3,4,...,N разряды счетчика, возникающие после (К+1)-го так TOBOfb импульса; сумма по модулю 2 а переносов 1 з г . . ® . . .® N-l равна величине которую формирует группа 1 элементов И-НЕ); на (Н+2)-й и (N+4)-ft входы - соответ ственно сигнал с выхода элемента НЕ 4 и инверсия этого сигнала, созда щие при взаимном су1««1ровании по модуЛю два уровень на (Н+3)-й вход - уровень на (N+5)-й, (Н+6)-йи(Ы+7)-й входы - уровень О на (Ы+8)-й и (Ы+9)-й входы - уровень на (Н+11)-й и ()-й входы - соответственно сигнал с выхода триггера 25 и его инверсия, со дающие при взаимном суммировании по модулю два уровень 1. Так как суммы по модулю Два сигн лов на входах (N+2), (N+3),...,(N+1 сумматора 5 равна 1, а свертка те кущего состояния контролируемых вхр дов 3 и сигнала .с выхода группы 1 элементов И-НЕ равна по модулю два сигналов следующего состояния счетчика (в принятых обозначениях: сумма tio модулю два текущего состоя 1,к®а2,; ния А, ЧС °1,,(1 --ч по модулю два переносов ®V® 2.AK® -г,к...в -NM,K-V следовательно. I (v® .K v® м.к«н.2.к-«1,к1(«.1., (%®«1.K ®(«H.K®«PM VAK| V41®«2. -®%..см сзгмма по модулю два следзлющего состояния), то на выходе сумматора 5 формируется контрольный разряд кода след1тощего состояния контролируемых выходов, дополняющий этот код до нечетности. По положительному перепаду тактового импульса на входе 26 контрольный разряд записывается в триггер 25 одновременно с изменением состояния контролируемых входов шины 3 . В положительный полупериод тактового сигнала (на входе 26 уровень 1) на выходе элемента ШШ-НЕ 20 формируется уровень О, создающий на вьгходе элемента И-НЕ 19 и входе (N+10) сумматора 5 уровень 1, а также запрещакяций работу дешифратора 12, и, следовательно, на его выходах присутствует уровень 1, поступаюий на вторые входы элементов И-НЕ 6 и 7 и ИЛИ-НЕ 8 и 9. Таким образом, разрешается прохождение на входы (N+3), (N+4) сумматора 5 через элементы 6 и 7 сигналов с выходов групп 1 и 2, а на выходах элементов ИЛИ-НЕ 8 и 9 и соответственно входах(N+5) и (Nfr6) сумматора формируется уровень О независимо от сигналов на входах O и 11. На выходах (Nf8) и (N+9) сумматора 5 - уровень 1, а на входе (N+7)- уровень О, определяемые лементами ШШ-ВЕ 15, И-НЕ 13 и 14 уровнем 1 на юсоде 21. Таким образом, на входы суммаора 5 поступают: на входы 1,...,N сш нового состояния контролируемых входов; на входы (N+1), (N+2.) и (N+3 сигналы с вЬколов групп 1 и 2 и их инверсии компенсирующие друг друга в свертке; на входы (К-ь5),..., (N+7) уровень на входы (N+8),..., (N+10) - уровень на вход (N+11) с выхода триггера 25 контрольный раз ряд нового состояния контролируемых выходов, сформированньй в предшествующая полупёриоде. TftK как свертка (сумма) по модулю два. сигналов на входах () и (N+10 равна to сумматор 4, складывая по модулю два код нового состояния, его контрольный разряд и 1, сформирует на выходе 28 либо уровень О при соответствии контрольного разряда новому состоянию контролируемых входо (признак исправности), либо уровень 1 при несоответствии (признак неисправности) Контроль обратного счета происходит аналогично, за исключением того, что формирование суммы по модулю два переносов следующего состояния счетчика производится не группой I эле, ментов И-НЕ, а группой 2 элементов Ш1И-НЕ и элементом НЕ 4, (если гц состояние 1-разряда счетчика после Кто тактового импульса, то последовательность сигналов представляет собой переносы (заемы), из 1,2,3,,.. N-ro разрядов счетчика, возникающие после (K+1)j-ro тактового ); V©°2. .величина .и-« к-г, 2,.Щ N-2,,K l,KVrtvj V5f-- 5 к VoT. OM-I,K 2 элечто реализуется группой ментов ШШ-НЕ и элем ентом . НЕ 4 запрет прохождения сигнала с вкхода л элемента 4 через элемент И-НЁ 7 оЬес печявается уровнем О с вь{хода 12j4 дешифратора 12. В режиме контроля прямого сдвига в отрицательный полупериод тактового сигнала уровень 1 на выходе элемен та ШШ-НЕ 20 и соответственно, управ ляющем входе дешифратора 12 и втором входе элемента И-НЕ 19 разрешает раб ту дешифратора и прохождение сигнала с триггера 25 на вход (N+10) суммато ра 5 через элемент 19.. Уровень О на выходе 12,5 депифратора 12 и втор входе элемента ИЛИ-НЕ 8 разрешает прохождение сигнала с последов тельНого входа 10 (сигнала, который при следующем тактовом сигнале запишется в 1-й разряд регистра сдвига) на вход (N+5) сумматора 5. Уровень 1 на остальных выходах дешифратора 12 и вторых входах элементов И-НЕ 6 и 7 и ИПИ-НЕ 8 и 9 разрешает прохождение сигналов с выходов группы 1 и элемента НЕ 4 и запрещает прохождение сигнала с входа 11 соответственно на входы (N+3), (N+4) и (N+6) сумматора 5 (на входе (N+6) уровень 0). Наличие О на входах элемента ИЛИ-НЕ 15 обеспечивает формирование на его выходе, первых входах элементов И-НЕ 13 и 14, входе (N+7) сумматора 5 уровня 1. На третьем входе элемента И-НЕ 13 уровень 1, обеспечиваемый элементом НЕ 16, на входе элемента 14 уровень ; , поступающий с входа 18 и обесречивающий уровень 1 на входе (N+9) сумматора 5. Наличие 1 на первом и третьем входах элемента 13 обеспечивает прохождение сигнала с N-rp контролируемого входа (сигнала, который будет вытолкнут из регистра при следздощем тактовом импульсе) на вход |(N+8) с чматора 5. ; Таким образом на входы сумматоры 5 поступают: 1,...,N входы - код текущего состояния регистра; на входы (N+1), (N+2) и (N+3), (N+4) сигналы с выходов групп 1 и 2 и их инверсии, но компейсируйщне друг друга при суммировании; на Вход (N+5) г инверсия сигнала последовательного входа 10; на вход (N+6) - уровень на вход (N+7) - урбвень на вход (N+8) - инверсия сигнала N-ro контролируемого входа, дополняющая до 1 в свертке сигнал на N входе сумматора 5; на вход (N+9) - уровень на входы (N+11) и (N+10) - сигнал с выхода триггера 25 И его инверсия, компен|сирующие друг друга в свертке, т.е. на; входы 1,.. .(N-l) , (N+5) сумматора 5 пост т1ают сигналы, которые будут присутствовать на контролируемых входах шины 3 при следующем тактовом импульсе, причем на (N+5)-M входе присутствует инверсия сигнала, свертка сигналов на входах N и (N+8), (N+1), (N+2) и (N+3), (N+4), (N+10) и (N+11), (N+7), (N+6), (N+9) равна О. Поэтому сумматор 5 формирует на информационном входе триггера 25 сигнал, соответствующий контрольному разряду следующего состояния регистра и записываемый по положительному т ерепаду тактового импульса на входе 26 в триггер 25 контрольного разряда одноврем.енно с изменением со.стояния регистра. Формирование контрольного сигнала в отрицательный полупериод тактового сигнала аналогично формированию приз нака исправности (неисправности) в режиме прямого счета. Контроль обратного сдвига проходит аналогично контролю прямого сдви га, за исключением того, что прохождение сигнала с последовательного входа 11 (сигнал, который при следую щем тактовом импульсе через последовательный вход сдвига запишется в N-й разряд регистра сдвига) разрешается уровнем О на выходе 12.6 дешифратора 12 и втором входе элемента ИЛИ-НЕ 9, а прохождение сигнала с входа 10 запрещается уровнем 1 с выхода 12,5 дешифратора 12. В отрицательный полупериод тактового сигнала на входы 2,3,... ,-N, (N+6 сумматора 5 поступают сигналы, которые будут записаны в 1-м, 2-м,..., ...,(, N-M разрядах регистра при следукнцем тактовом импульсе, при чем на (N+6)-M входе присутствует инверсия сигнала. Свертка сигналов на входах 1 и (N+9), (N+1), (N-«-2) и (N+3), (N+4), (N+10) и (N+11), (N+7), (N+5), (N+8) равна 0. В режиме контроля записи информации, определяемом уровнем 1 на входе 24, контрольный разряд, соответствующий состоянию контролируемых входов, записывается в триггер 25 одновременно с изменением состояния контролируемых входов. Запись 10 . 12 в триггер 25 производится с помощью элементов И-НЕ 21 и 22 по установочным входам независимо от состояния на информационном и синхровходе триггера. Уровень 1 на входе 24 формирует О на выходе элементов ИЛИ-НЕ 20 и 15, который запрещает работу дешифратора 12, создавая на его выходах уровень 1, и обеспечивает уровень 1 на выходах элементов И-НЕ 13, 14 и 19 и входах (N+8), (N+9), (N+10) сумматора 5. На выходах эл1ементов ИЛИ ИЛИ-НЕ 8 и 9 и входах (N+5), (N+6), (N+7) уровень О. Уровень 1 на входах дешифратора 12 разрешает прохождение сигналов с выходов группы 1 и элемента НЕ 4 на входы (N+3) и (N+4) через элементы И-НЕ 6 и 7, обеспечивая тем самым компенсацию сигналов rpyim 1 л 2 в свертке. Информационный код поступает на входы 1, ....,N сумматора 5 на вход (N+11) которого поступает контрольный разряд, а свертка сигналов на остальных входах равна 1. Поэтому сумматор 5 формирует контрольный сигнал - уровень О при соответствии контрольного разряда записанному в регистре коду, шш уровень 1 при несоответствии. Эффективность изобретения заключается в расш1фен1Ш области применения Устройства путем обеспечения контроля азличных операций (функциональных локов) одним и тем же контрольным оборудованием без использования доолнительный выходов проверяемого борудования, а также за счет увеичения числа контролируемых режимов, то позволяет увеличить полноту контоля . При модульном проектировании зобретение обеспечивает построение онтрольного модуля, заменяющего неколько типов модулей.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| М., Мир, 1972, с | |||

| ПЕЧНОЙ ЖЕЛЕЗНЫЙ РУКАВ (ТРУБА) | 1920 |

|

SU199A1 |

| .: | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент CIIIA № 3567916, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-30—Публикация

1982-06-11—Подача