(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1983 |

|

SU1083181A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

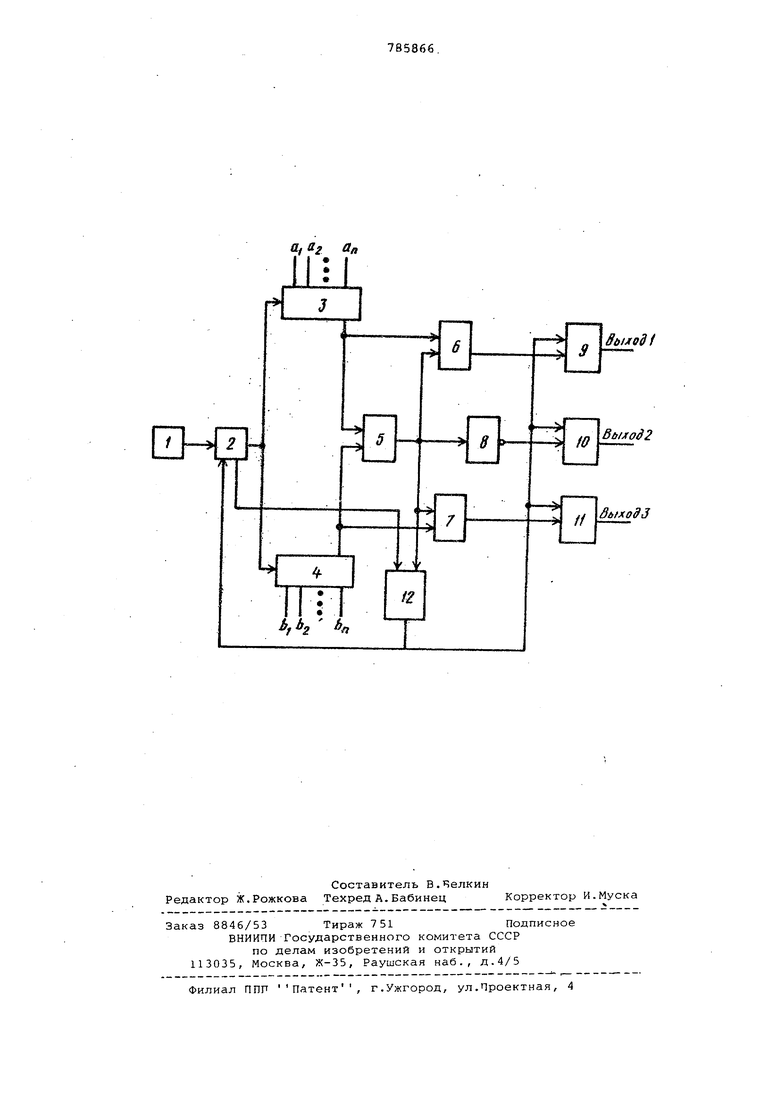

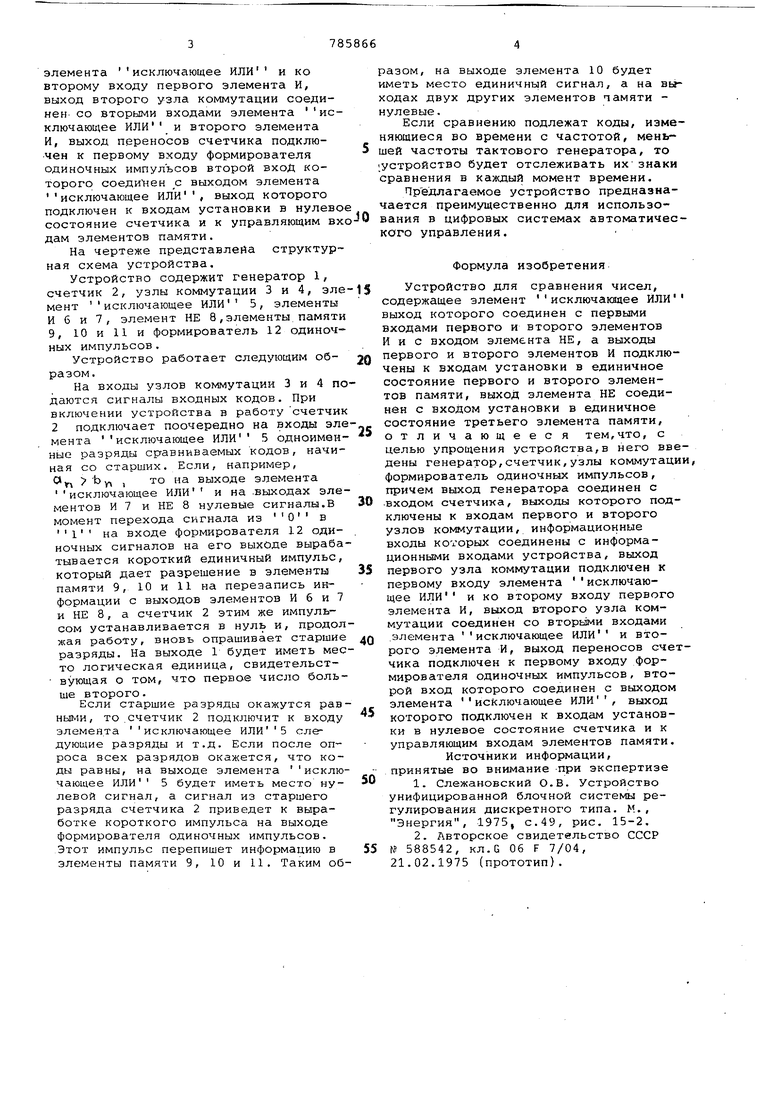

Изобретение относится к автоматике и вьмислительной технике и может быть использовано в цифровых системах автоматического управления и регулирования . Иэвестио устройство сравнения кодов, выполненное на логических элементах ИЛИ-НЕ tl. Устройство является сложным и обладает низкой помехозащищенностью. Наиболее близким к изобретению яв ляется устройство, выполненное на ячейках исключающее , собранных на элементах И-НЕ и И-ИЛИ-НЕ. На каждую пару разрядов сравниваемых кодов используется одна двухвходовая ячейка исключающее ИЛИ . На входы этнх ячеек подаются сигналы от одноименных разрядов сравниваемых кодов а выходы всех ячеек подключены к вхо дам многовходового логического элемента ИЛИ-НЕ. На выходе этого элемента появляется сигнал, соответствующий логической единице, в случае равенства кодов. Кроме того, для выделения большего из сравниваемых кодов в каждом разряде использовано по одному элементу 2И. Выходы этих элементов объединены в соответствии с минимизированным . математическим выражением многовходовыми элементами И и илиШ. Основным недостатком устройства является его сложность при использовании для сравнения многоразрядных кодов, Целью изобретения является упрощение устройства. Указанная цель достигается тем, что в устройство для сравнения чисел, содержащее элемент исключающее ИЛИ , выход которого соединен с первыми входами первого и второго элементов И и с входом элемента НЕ, а выходы первого и второго элементов И подкпючены к входам установки в единичное состояние первого и второго элементов памяти, выход элемента НЕ соединен с входом установки в единичное состояние третьего элемента памяти, введены генератор, счетчик, узлы коммутации, формирователь одиночных импульсов, причем выход генератора соединен с входом счетчика, выход которого подключен к входам первого и второго узлов коммутации, информационные входы которых соединены с информационными входами устройства, выход первого узла коммутации подключен к первому входу элемента исключающее ИЛИ и ко второму входу первого элемента И, выход второго узла коммутации соединен- со вторыми входами элемента ключающее ИЛИ и второго элемента И, выход переносов счетчика подключен к первому входу формирователя одиночных импульсов второй вход которого соединен с выходом элемента исключающее ИЛИ , выход которого подключен к входам установки в нулево состояние счетчика и к управляющим вх дам элементов памяти. На чертеже представлейа структур ная схема устройства. Устройство содержит генератор 1, счетчик 2, узлы коммутации 3 и 4, эл мент исключающее ИЛИ 5, элементы И 6 и 7, элемент НЕ 8,элементы.памят 9, 10 и 11 и формирователь 12 одиноч ных импульсов. Устройство работает следующим образом. На входы узлов коммутации 3 и 4 п даются сигналы входных кодов. При включении устройства в работу счетчи 2 подключает поочередно на входы эл мента исключающее ИЛИ 5 одноимен ные разряды сравниваемых кодов, начиная со старших. Если, например, CJ Ъ то на выходе элемента исключающее ИЛИ и на .выходах эле ментов И 7 и НЕ 8 нулевые сигналы.В момент перехода сигнала из О в 1 на входе формирователя 12 одиночных сигналов на его выходе выраба тывается короткий единичный импульс, который дает разрешение в элементы памяти 9, 10 и 11 на перезапись информации с выходов элементов И 6 и 7 и НЕ 8, а счетчик 2 этим же импульсом устанавливается в нуль и, продол жая работу, вновь опрашивает старшие разряды. На выходе 1 будет иметь мес то логическая единица, свидетельствующая о том, что первое число боль ше второго. Если старшие разряды окажутся рав ными, то .счетчик 2 подключит к входу элемента исключающее следующие разряды и т.д. Если после опроса всех разрядов окажется, что коды равны, на выходе элемента исклю чающее ИЛИ 5 будет иметь место нулевой сигнал, а сигнал из старшего разряда счетчика 2 приведет к выработке короткого импульса на выходе формирователя одиночных импульсов. Этот импульс перепишет информацию в элементы памяти 9, 10 и 11. Таким об азом, на выходе элемента 10 будет меть место единичный сигнал, а на выходах двух других элементов памяти нулевые. Если сравнению подлежат коды, изменяющиеся во времени с частотой, меньей частоты тактового генератора, то устройство будет отслеживать их- знаки сравнения в каждый момент времени. Предлагаемое устройство предназнаается преимущественно для использования в цифровых системах автоматического управления. Формула изобретения Устройство для сравнения чисел, содержащее элемент исключакнцее ИЛИ выход которого соединен с первыми входами первого и второго элементов И и с входом элемента НЕ, а выходы первого и второго элементов И подключены к входам установки в единичное состояние первого и второго элементов памяти, выход элемента НЕ соединен с входом установки в единичное состояние третьего элемента памяти/ отличающеес я т ем, что, с целью упрощения устройства,в него введены генератор,счетчик,узлы коммутации, формирователь одиночных импульсов, причем выход генератора соединен с входом счетчика, выходы которого подключены к входам первого и второго узлов коммутации, информационные входы которых соединены с информационными входами устройства, выход первого узла коммутации подключен к первому входу элемента исключающее ИЛИ и ко второму входу первого элемента И, выход второго узла коммутации соединен со вторьоми входами элемента исключающее ИЛИ и второго элемента И, выход переносов счетчика подключен к первому входу формирователя одиночных импульсов, второй вход которого соединен с выходом элемента исключающее ИЛИ , выход которого подключен к входам установки в нулевое состояние счетчика и к управляющим входам элементов памяти. Источники информации, принятые во внимание при экспертизе 1.Слежановский О.В. Устройство унифицированной блочной системы регулирования дискретного типа. М., Энергия, 1975, с.49, рис. 15-2. 2.Авторское свидетельство СССР № 588542, кл.С Об F 7/04, 21.02.1975 (прототип).

Вылод2

SufXoffJ

Авторы

Даты

1980-12-07—Публикация

1978-11-20—Подача