I

Изобретение относится к радиоте-х нике и может быть .использовано для сбора и передачи сообщений с повышенной вероятностью доведения.

Известно устройство для приема 5 дискретных сигналов, содержащее последовательно соединенные первый клапан, второй клапан, информационный регистр и первый сумматор по модулю два, выход которого подключен 10 к первому входу первого клапана и первому входу второго сумматора по модулю два, выход которого соединен с первыми входами третьего клапана и третьего сумматора по модулю два, ход которого подключен к первому входу четвертого клапана, выход которого через первый счетчик соединен с первыми входами- второго счетчика и первого триггера, выход которого под-20 ключей ко вторым входам, первого, второго и третьего клапана, выход которого соединен со входом регистра синхрониз.ации, выходы которого по-дключенЫ соответственно ко входам чет-25 зертого и пятого сумматора по модулю два, выход которого соединен со вторым входом третьего сумматора по модулю два и третьим входом третьег-о клапана, и последовательно соединенные дешифратор, пятый клапа.н и второй триггер, выход которого подключен к первым входам шестого и седьмого клапанов, при этом второй вход шестого клапана соединен со вторым выходом информационного регистра и первьом входом шестого сумматора по модулю, два-, выход которого подключен к третьему входу второго клапана, а выход седьмого клапана соединен со вторым входом второго триггера и первым входом третьего триггера, выход которого подключен ко входам третьего и четвертого клапанов .

однако известное устройство не обеспечивает возможность контролй дискретного канала связи по принимаемым сигналам.

Цель изобретения - обеспечение возможности контроля дискретного канала связи по принимаемым.сигналам.

С этой целью в устройство для при ема дискретных сигналов,содержащее последовательно соединеннь е первый клапан, второй клапан, информационный регистр и первый сумматор по модулю два, выход которого подключен к первому входу первого клапана и первому входу второго сумматора по модулю два, выход которого соединен

с первыми входами третьего клапана и третьего сумматора по модулю два, выход кот;орого подключен к первому входу четвертого клапана, выход которого через первый счетчик соединен с первыми входами второго счетчика и первого триггера, выход которого подключен ко вторым входам первого, , второго и третьего клапана, выход которого соединен со -входом регистра синхронизации, выходы которого подключены соответственно ко вводам четвертого и пятого сумматора по модулю два, выход которого соединен со вторым входом третьего сумматора по модулю два и третьим входом третьго клапана, и последовательно соединенные дешифратор, пятый клапан и второй триггер, выход которого подключен к первым входам шестого и седьмого клапанов, при этом второй вход шестого клапана соединен со втоРШ4 выходом информационного регистра и первым входом шестого сумматора по модулю два, выход которого подключен к третьему .входу второго, клапайа а выход седьмого клапана соединен со вторым входом второго триггера и первым входом третьего триггера, выход которого подключен ко вторым входам третьего и четвертого клапанов, введаны два дополнительных клапана, бло оценки канала и анализатор канала, выходы которого соединены со вторыми входами второго сумматора по модуJoo два и пятого клапана, третьим входом первого клапана и первыми входами дополнительных клапанов,выходы которых подключены соответственно ко входу блока оценки канала и второму входу седьмого клапана.Выход пятого клапана соединен со вторым входом второго счетчика, выход которого подключен к третьему входу второго сч.етчика и второму входу первого дополнительного клапана, выход

которого подключен ко вторым ВХОДс1М

первого и третьего триггера, выход которого -подключен ко второму входу второго дополнительного клапана,третий вход которого соединен с выходом третьего сумматора по модулю два,бторой вход которого соединен со вторым входом шестого сумматора по модуЛю два/ а выход четвертого сумматора по модулю два подключен ко входу дешифратора .

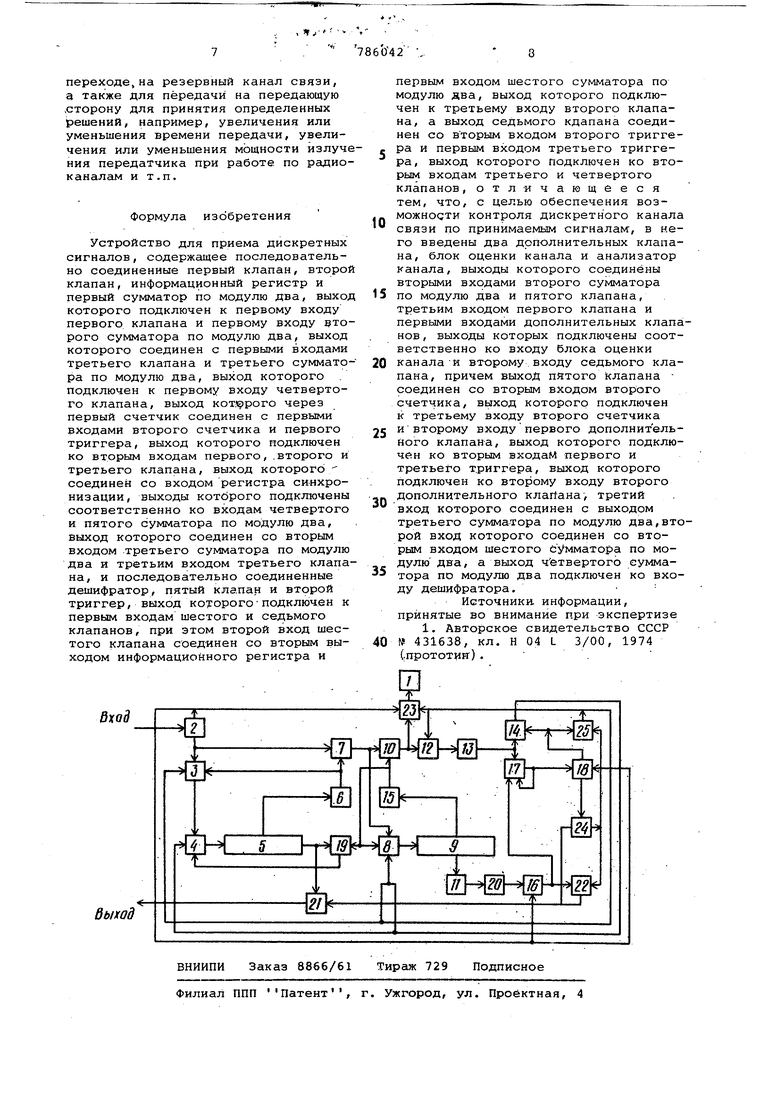

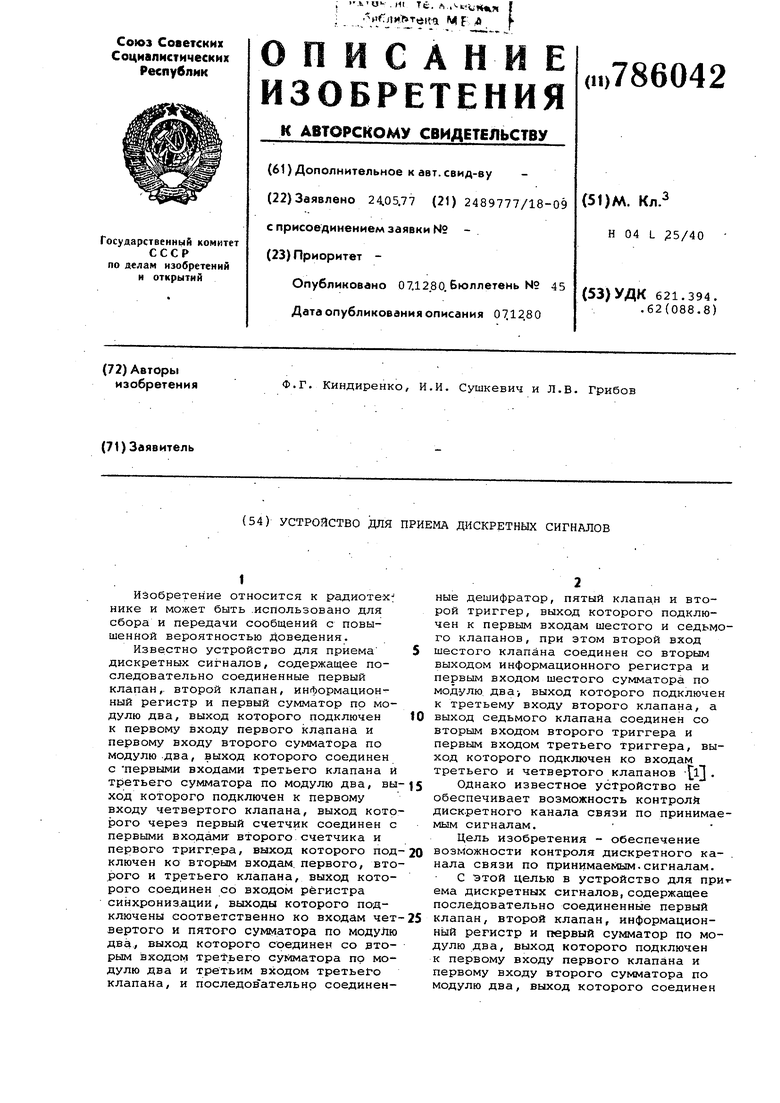

На чертеже изображена структурная эл|гктрическая схема предложенного устройства.

Устройство для приема дискретных сигналов содержит блок 1. оценки ка,нала, анализатор 2 ка нала; первый 3 и второй 4 клапаны, информационный регистр 5, первый 6 и второй 7 сумматоры по модулю два, третий клапан 8 регистр 9 синхронизации, третий 10 .и четвертый 11 сумматоры по модулю двэ/ четвертый клапан 12,- первый

счетчик 13, первый триггер 14, пятый сумматор 15 по модулю два, пятый клапан 16, второй счетчик 17, первый дополнительный клапан 18, шестой сумматор 19 по модулю два, дешифратор 20, шестой клапан 21, второй триггер 22, второй дополнительный клапан 23, седьмой клапан 24 и третий триггер 2

Устройство работает следующим образом.

На.информационный вход устройства поступает принятая по каналу связи объединенная кодовая последовательность в виде суммы по модулю два информационной и синхронизирующей последовательностей.

Эта последовательность через анализатор 2, который определяет принадлежность входной информации данному приемному объекту путем проверки структуры информации, и открытые в рассматриваемый момент клапаны 3, 4 поступает на вход регистра 5.

С регистра 5, точки съема которого аналогичньд точкам съема информационного регистра передатчика,объединенная рекуррентная последовательность поступает на сумматор 6 на выходе которого образуется рекуррентная последовательность, структура которой аналогична структуре информационной рекуррентной последовательности передатчика. Принятая из канала объединенная рекуррентная последовательность с выхода анализатора 2 и последовательность с выхода сумматора 6 поступают на соответствующие входы сумматора 7. В результате на выходе сумматора 7 образуется синхронизирующая последовательность, аналогичная переданной, но сдвинутая относительно нее по фазе. Эта синхронизирующая последовательность клапан 8 подается на регистр 9 и через точки съема поступает на сумматор 15. Результируквдая последовательность с выхода сумматора 15 складывается по модулю два в сумматоре 1Q с синхронизируквдей последовательностью, поступающей с выхода сумматора 7.

При неискаженном приеме объединенной последовательности,. а следовательно, неискаженных синфазных между собой синхронизирующих последовательностей на входах сумматора 10 на его выходе образуется нулевая последовательность, которая через кла-пан 12 подается на вход счетчика 13 К нулей подрад. Таким образом, регистр 5 и регистр 9 заполнены соответственно отрезками объединенной и сдвинутой относительно нее синхронизирующей последовательностей. После отсчета К. нулей подряд сигналом с счетчика 13 запускается триггер 14, который переключает клапаны 4 и 8. Тем самым отключается от входа регистра поступающая с выхода анализатора 2 канала объединенная последовательность, а вместо последовательности с выхода сумматора 7 на вход ргистра 9 подключается обратная связь с выхода сумматора 15. Синхронизирующая последовательность, не содержащая искаженных посылок (ошибок), вырабатываемая автономно с выхода сумматора 15, поразрядно поступает на вход сумматора 19, на второй вход которого подается поразрядно объединенная последовательность с выхода регистра 5. В результате суммирования по модулю два на выходе сумматора 19 образуется отрезок информационной последовательности, не содержащей ошибок, который через клапан 4, открытый сигналом с триггера 14, записывается в регистр 5. Запись информации с выхода сумматора 19 в регистр 5 осуществляется в течение числа тактов, равного объему накопления регистра 5. Для этого одновременно с запуском триггера 14 выходным сигналом со счетчика 13 запускается счетчик 17,отсчитывающий число тактов, равное объему накопления регистра 5. Сигнал с этого счетчика через клапан 18 запускает триггер 25 и сбрасывает триггер 14. После этого счетчик 17 устанавливается в исходное состояние по цепи местного сброса. Под действием сигналов с выходов триггеров 14 и. 25 переключ.аются клапаны 3 и 4,в реаультате чего регистр 5, заполненный к этому моменту информационной последовательностью, совместно«с сумматором 6,выход которого через открытые клапаны 3 и 4 подключается ко входу регистра 5, начинает вырабатывать автономно информационную последовательность не содержащую ошибок. Одновременно сигналом с триггера 25 закрывается клапан 12 и открывается клапан 23.

Таким образом, устанавливается синхронная и синфазная работа регистров передатчика и приемника.

С этого момента регистр 5 и регистр 9 приемника, выполняя роль эталонных датчиков, автономно вырабатывают рекуррентные информационную и.синхронизирунядую последовательности соответственно. Принимаемая по каналу связи объединенная последовательность, подвергнутая воздействию ломех и содержащая ошибки, через анализатор 2 канала подается на второй вход сумматора 7, на первый вход которого поступает информационная последовательность, вырабатываемая автономно регистром 5. В результата сложения по модулю два объединенной и информационной последовательностей на выходе сумматора 7 вваделяется последовательность, содержащая синхронизирующую рекуррентную последовательность и ошибки канала связи, которая поступает на-второй вход dyM,матора 10, на первый вход которого подается синхронизирующая последовательность, вырабатываемая автономно регистром 9 и не содержащая ошибок. В результате сложения по модулю два этих последовательностей на выходе сумматора 10 выделяются ошибки, которые через открытый клапан 23 поступают в блок 1 оценки канала. Количество ошибок,.зарегистрированных за определенное время в блоке 1, харакoтеризует текущее качество канала связи.

Измерение канала проходит до тех пор, пока поступает из канала связи объединенная последовательность. По

5 ее окончании анализатор 2 канала на .управляющем выходе вьщает сигнал об окончании приег а, который закрывает клапан 23, прекращая teM caNnjM поступление ошибок с выхода сумматора

0 10 на.блок 1, закрывает клапан 18 по первому выходу, открывая его по второму, и открывает клапан 16.

В результате синхронизирующая последовательность с регистра 9 через суь-матор 11, имеющий специально по5добранные точки съема для устранения сдвига синхронизирующей последовательности относительно информационной, поступает на дешифратор 20. Выходной сигнал дешифратора 20 через

0 открытый клапан 16 запускает триггер 22, открывающий клапаны 21, 24 и запускает счетчик 17. К этому моменту в регистре 5 в результате его автономной работы возникает исходная ин5формация, соответствующая переданному сообщению.

Через открытый клапан 21 принятое сообщение с выхода регистра 5 поступает на выход устройства. Счетчик 17,

0 отсчитав число тактов, равное объему регистра 5, вьадает сигнал, который через клапаны 18 и 24 сбрасывает триггеры 22 и 25 и останавливает себя по цепи местного сброса. В результате закрывается клапан 21, прекра5щая выдачу информационной последовательности на выход устройства, переключаются клапаны 3 и 8, подключая выход анализатора 2 канала к регистру 5, а выход сумматора 7 ко входу

0 регистра 9, включается клапан 12, а клапан 24 закрывается. Таким образом, устройство переходит в исходное состояние и готово к приему нового сообщения.

5

Техническая эффективность изобретения заключается в расширении функциональных возможностей устройства . за счет возможности осуществления о ценки текущего состояния канала связи.

0

в каждом цикле наряду с приемом сообщения производится оценка текущего состояния канала связи, которая может быть использована для подстройки канала, для принятия решения о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретных сообщений | 1977 |

|

SU649161A1 |

| Устройство для передачи и приема самосинхронизирующихся кодограмм | 1986 |

|

SU1403379A1 |

| Устройство фазирования циклов многоканальной системы передачи дискретной информации | 1980 |

|

SU896782A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Устройство для выделения сигнала фазового пуска | 1989 |

|

SU1644397A2 |

| Анализатор рекуррентного сигнала фазового пуска | 1981 |

|

SU995361A2 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

Авторы

Даты

1980-12-07—Публикация

1977-05-24—Подача