1

Изобретение относится к технике электросвязи и может использоваться для определения скорости модуляции в синхронных и стартстопных системах связи.

По основному авт. св. № 577692 известно устройство для определения скорости телеграфирования, содержащее последовательно соединенные преобразователь входных сигналов, блок квантования, ко второму и третьему входам которого подключены выход генератора опорных частот и управляющий выход блока выделения эле янтарного периода входного сигнала, блок пересчета и блок индикации, а второй выход преобразователя входных сигналов через формирователь сигнала «Сброс подключен к установочному входу блока выделения элементарного периода входного сигнала, причем третий выход генератора опорных частот соединен с третьим входом блока пересчета 1.

Однако известное устройство имеет низкую точность определения скорости телеграфирования.

Цель изобретения - повышение точности определения скорости телеграфирования.

Для достижения этой цели в устройство для определения скорости телеграфирования, содержащее последовательно соединенные преобразователь входных сигналов, блок квантования, ко второму и третьему входам которого подключены выход генератора опорных частот и управляющий выход блока выделения элементарного периода входного сигнала, блок пересчета и блок индикации, а второй выход преобразователя входных сигналов через (})ормирователь сигнала

10 «Сброс подключен к установочному входу блока выделения элементарного периода входного сигнала, причем третий выход генератора опорных частот соединен с третьим входом блока пересчета, введены дополнительный блок квантования, дополнительный

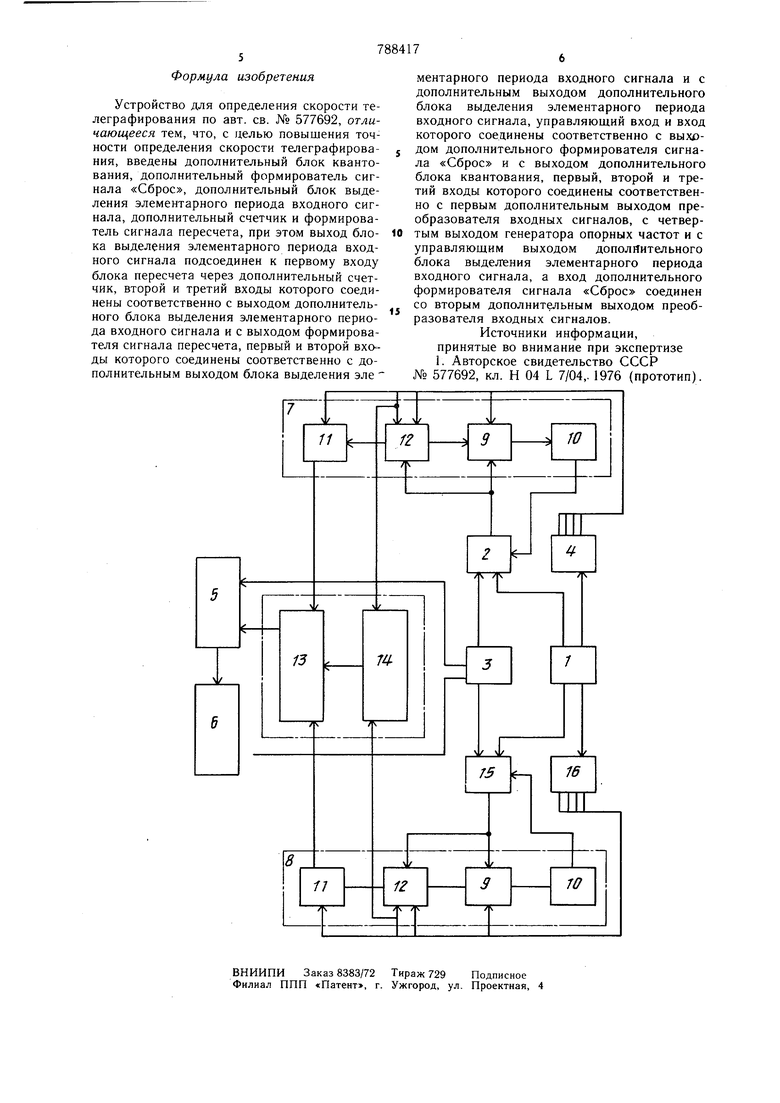

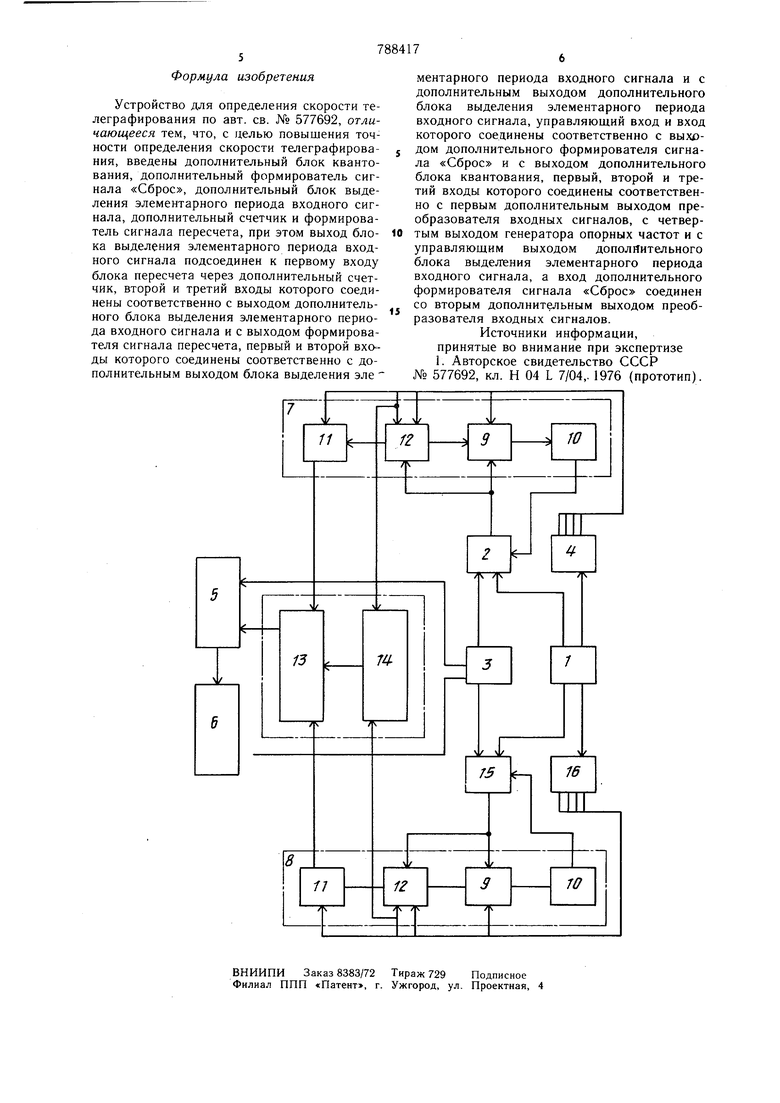

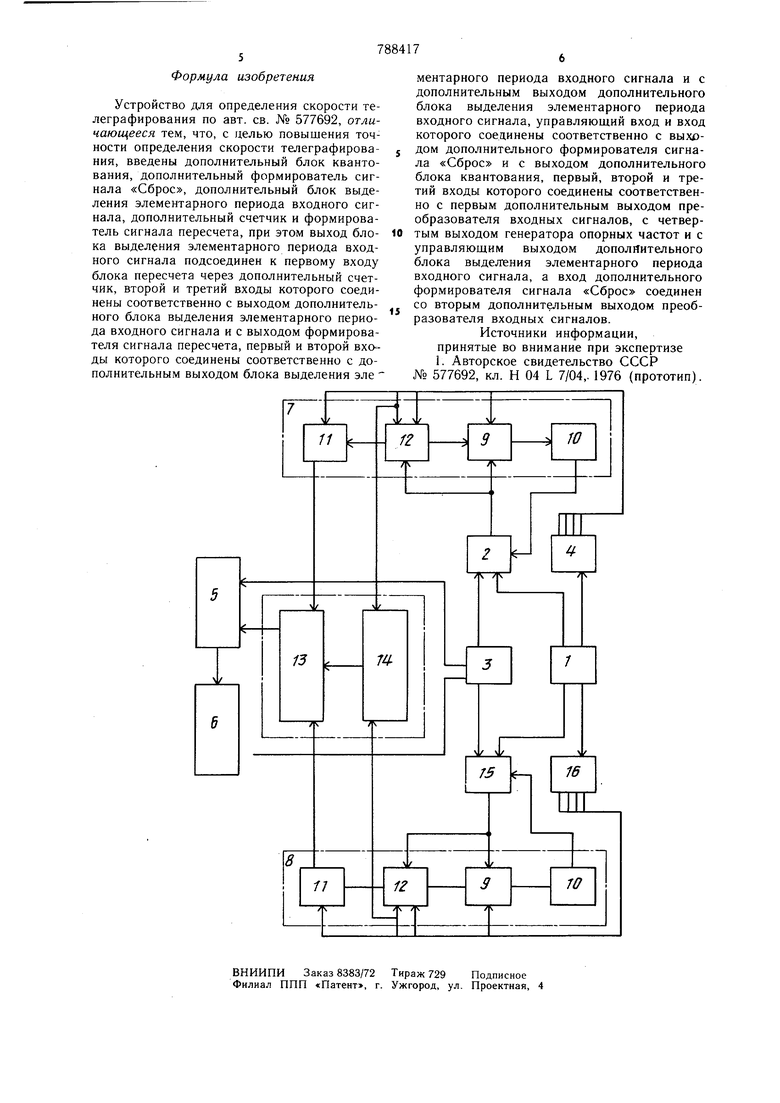

5 формирователь сигнала «Сброс, дополнительный блок выделения элементарного периода входного сигнала, дополнительный счетчик и формирователь сигнала пересчета, при этом выход блока выделения элементарного периода входного сигнала подсоединен к первому входу блока пересчета через дополнительный счетчик, второй и третий входы которого соединены соответственно с выходом дополнительного блока выделения элементарного периода входного сигнала и с выходом формирователя сигнала пересчета, первый и второй входы которого соединены соответственно с дополнительным выходом блока выделения элементарного периода входного сигнала и с допопнительным выходом дополнительного блока выделения элементарного периода входного сигнала, управляющий вход и вход которого соединены соответственно с выходом дополнительного формирователя сигнала «Сброс и с выходом дополнительного блока квантования, первый, второй,и третий входы которого соединены соответственно с первым дополнительным выходом преобразователя входных сигналов, с четвертым выходом генератора частот и с управляющим выходом дополнительного блока выделения элементарного периода входного сигнала, а вход дополнительного формирователя сигнала «Сброс соединен со вторым дополнительным выходом преобразователя входных сигналов. На чертеже представлена структурная электрическая схема предложенного устройства. Устройство для определения скорости телеграфирования содержит преобразователь 1 входных сигналов; блок 2 квантования; генератор 3 опорных частот; формирователь 4 сигнала «Сброс ; блок 5 пересчета; блок 6 индикации; блок 7 выделения элементарного периода входного сигнала; дополнительный блок 8 выделения элементарного периода входного сигнала, каждый из которых состоит из реверсивного счетчика 9, дешифратора 10 нулевого состояния реверсивного счетчика, элемента 11 памяти и суммирующего счетчика 12; дополнительный счетчик 13; формирователь 14 сигнала пересчета; дополнительный блок квантования 15; дополнительный формирователь 16 сигнала «Сброс. Устройство работает следующим образом. Из сигнала, поступающего на преобразователь 1, формируются прямоугольные посылки, которые подаются на один из входов блоков 2 и 15 квантования. На второй вход этих блоков подается кварцованная частота с выхода генератора 3 опорных частот. Пачки импульсов с выхода блоков 2 и 15 поступают одновременно на входы синхронизации суммирующего счетчика 12 и реверсивного счетчика 9. Первая посылка, заполненная кварцованной частотой, записывается в оба счетчика. Затем сигналом «Сброс, с.формированным путем задержки заднего фронта посылки формирователем 4 и дополнительным формирователем 16, реверсивный счетчик 9 переводится в нулевое состояние, а число, записанное в суммирующем счетчике 12 параллельным кодом, переписывается в реверсивный счетчик 9 и элемент 11 памяти с одновременной установкой суммирующего счетчика 12 в нулевое состояние. Вторая пачка импульсов записывается в суммирующий счетчик 12, а в реверсивном счетчике 9 производится считывание числа, обусловленного первой посылкой. Если вторая посылка короче первой, то реверсивный счетчик 9 не доводится до нулевого состояния. Сигнал «Сброс опять переводит реверсивный счетчик 9 а нулевое состояние и переписывает в него число второй посылки с суммирующего счетчика 12. Если третья посылка по длительности больще второй, то она, считывая число второй посылки, доводит реверсивный счетчик 9 до нулевого состояния. Дешифратор 10 запирает блоки 2 и 15 квантования, запрещая счет всей длительности третьей посылки суммирующим счетчиком 12. Таким образом, в суммирующий счетчик 12 может записаться число, равное записанному в реверсивном-счетчике 9, или меньшее, соответствующее более короткой посылке всей предыдущей последовательнос1;и. Процесс анализа входного сигнала повторяется с приходом каждой новой посылки. При поступлении посылки минимальной длительности она, записавшись соответствующим числом в суммирующий счетчик 12 и далее - в реверсивный счетчик 9, контролирует все последующие посылки. Информация о длительности позитивных посылок с элемента 11 памяти блока 7 параллельным кодом переписывается в дополнительный счетчик 13, а негативных посылок с элемента 11 памяти блока 8 - последовательным кодом. Формирователь 14 сигнала пересчета сформирует- команду на пересчет при поступлении по одному сигналу «Сброс с формирователей 4 и 16 при условии поступления сигнала первым с формирователя 4. Таким образом, в дополнительном счетчике 13 записывается число, соотвeтcтвy oщee суммарной длительности минимальных посылок из последовательностей «Позитив и «Негатив. Это число, несущее в себе инфо рмацию о длительности двух элементарных посылок принимаемых сигналов, поступает в блок 5 пересчета, который пересчитывает его в число, соответствующее скорости модуляции. Блок 6 индикации высвечивает результат измерения. Таким образом, предложенное устройство обеспечивает точное определение скорости модуляции независимо от наличия и величины преобладания в измеряемых сигналах, что очень важно при эксплуатации различных оконечных устройств. Определение же скорости модуляции при наличии преобладаний выделением предполагаемой элементарной посылки одной полярности дает ложный результат. Истинное значение скорости модуляции в этом случае можно получить лишь усреднением двух посылок минимальной длительности, выделенных из позитивной и негативной последовательностей измеряемых сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения скорости телеграфирования | 1976 |

|

SU577692A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ДЛИТЕЛЬНОСТИ ЭЛЕМЕНТАРНОЙ ПОСЫЛКИ ТЕЛЕГРАФНЫХ СООБЩЕНИЙ С РАЗЛИЧНЫМИ СКОРОСТЯМИ ТЕЛЕГРАФИРОВАНИЯ | 1973 |

|

SU383218A1 |

| Устройство для определения скорости телеграфирования | 1976 |

|

SU653760A1 |

| Устройство для измерения скорости телеграфирования | 1982 |

|

SU1059691A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Регенератор приемника стартстопных телеграфных сигналов | 1976 |

|

SU641671A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

Авторы

Даты

1980-12-15—Публикация

1979-02-14—Подача