(54) ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU976482A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1777178A1 |

| Устройство для контроля параметров двигателя внутреннего сгорания | 1988 |

|

SU1733946A1 |

| Управляемый умножитель частоты следования импульсов | 1982 |

|

SU1034145A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1277351A1 |

Изобретение относится к автоматике и контрольно-измерительной технике и может Способствовать, в частности увеличению девиации в системах контроля. Известен умножитель частоты, выполненный на основе аналоговой техники и состоящий иэ линейного интегратора, двух нуль.-6рганов и элемента ИЛИ. Входной синусоидальный сигнал поступает на входы первого нуль.-органа и линейного интегратора. На вход второго нуль-органа поступает сигнал с выхода линейного интегратора с фазой 9-1Ч1 относительно BjcoOHoro сигнала. Нуль-органы формируют узкие импульсы в момент прохождения сигналами соответственно через нулевые точки. Выходы нупь.-органов соединены с элементом ИЛИ. Выходной сигнал логического элемента или имеет частоту в четыре раза больше, чем частота входного сигнала l7 Недостатком данного устройства является нестабильность работы и низкая точность. Наиболее близким по технической сущности является цифровой умножитель частоты следования импульсов, выполненный на основе цифровой техники и состоящий из генератора первой опорной частоты, соединенного последовательно с первым счетчиком импульсов, первым входом блока сравнения кодов, буферным устройством и из генератора второй опорной частоты, соединенного последовательно с вторым счетчиком импульсов, устройством памяти и со вторым входом схемы сравнения кодов, входы синхронизации второго счетчика импульсов и устройства памяти соединены со входной шиной, а выход буферного устройства соединен с входом установки в ноль первого счетчика импульсов IX. Недостатком этого устройстьа является то, что частота выходного сигнала формируется с ошибкой, определяемой дискретностью измерения периода входного сигнала во втором счетчике импульсов. Величина этой ошибки, приведенная

ко времени следования импульсов, может составлять П периодов частоты генератора первой опорной частоты за период частоты сигнала, подлежащего умножению.

Целью изобретения является повышение точности умножения частоты.

Поставленная цель достигается тем, что в цифровой умножитель частоты следования импульсов, содержащий генератор опорной частоты, первый выход которого соединен со входом первого счетчика импульсов, блок памяти, вход которого соединен с выходом второго счетчика импульсов, а выход - через блок сравнения кодов, второй вход которого подключен к выходу первого счетчика импульсов, со входом буферного устройства, введены делитель частоты, вход которо-, го соединен со вторым выходом генера- тора опорной частоты, а выход - со входом второго счетчика импульсов, два элемента И, третий счетчик импульсов, вход которого соединен с выходом делителя частоты, счетный вход - с выходом первого элемента И и входом установки минус единицы первого счетчика импуль- сов, вход установки в нуль которого подключен к выходу второго элемента И, и дешифратор, вход которого соединен с выходом третьего счетчика импульсов, а прямой и инверсный выход - с первыми входами соответственно первого и второго элементов И, вторые входы которых подключены к выходу буферного устройст ва.

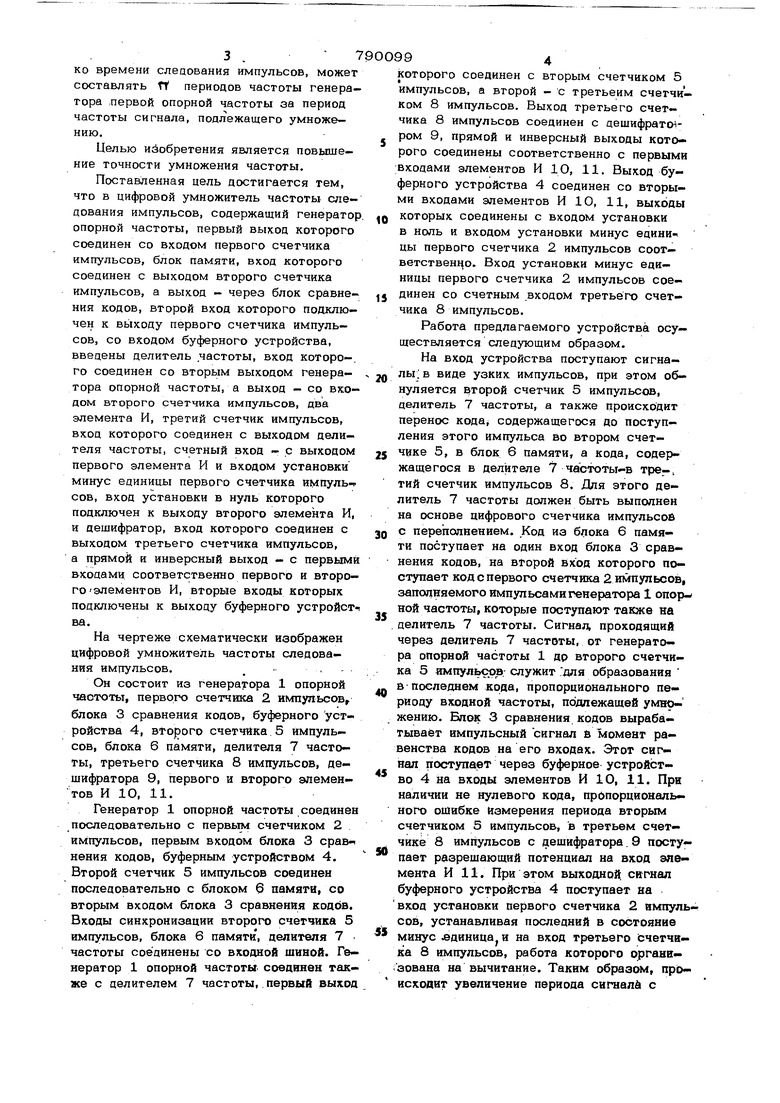

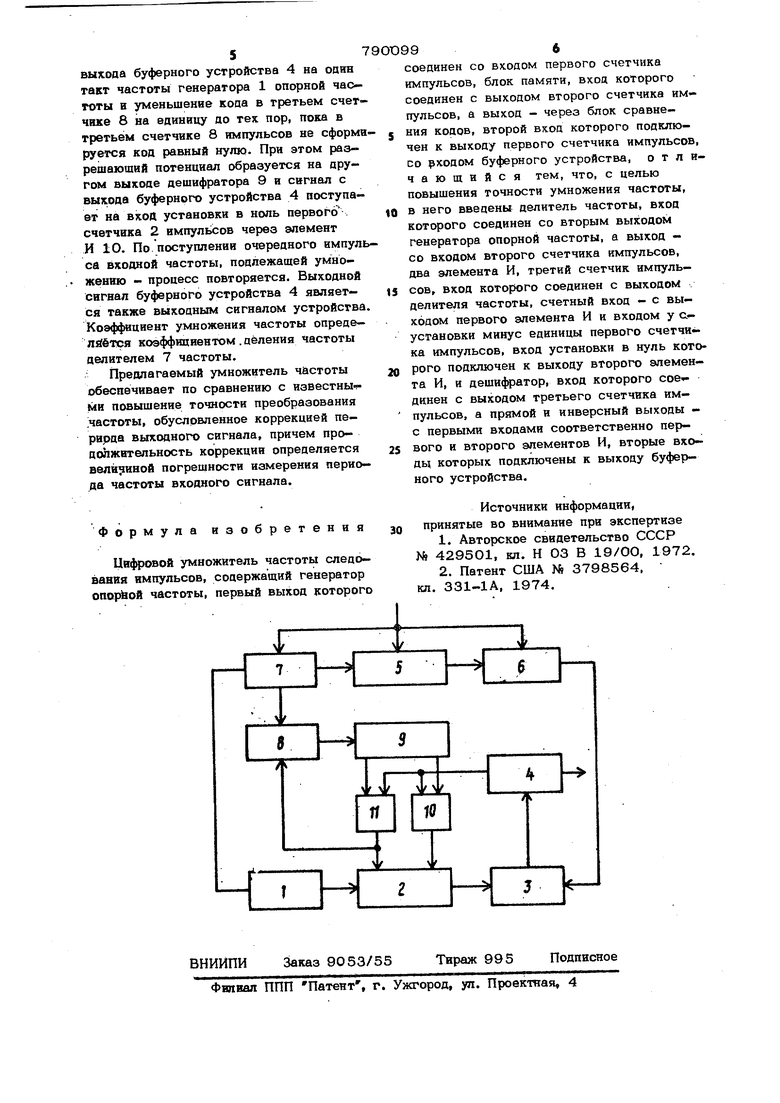

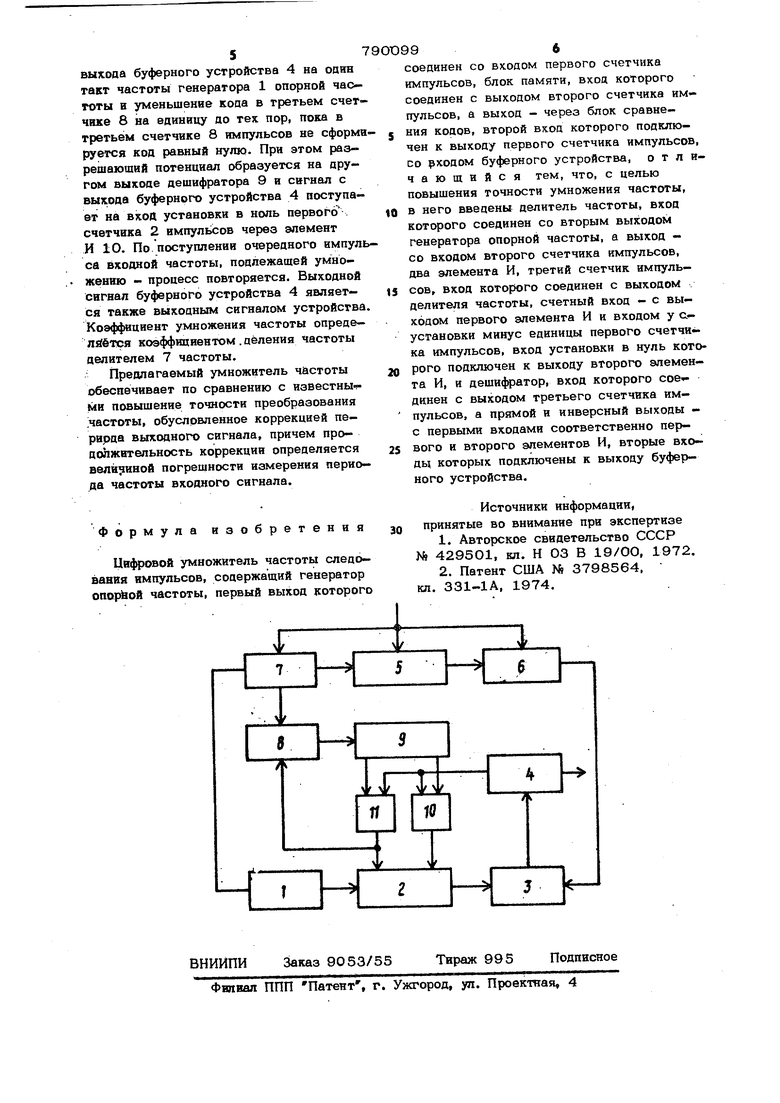

На чертеже схематически изображен цифровой умножитель частоты следования им)1ульсов., .

Он состоит из генератора 1 опорной частоты, перврго счетчика 2 HivraynbcOB

блока 3 сравнения кодов, буферного устройства 4, второго счетчика 5 импульсов, блока 6 памяти, делителя 7 частоты, третьего счетчика 8 импульсов, дешифратора 9, первого и второго элементов И 1О, 11.

Генератор 1 опорной частоты соединен последовательно с первым счетчиком 2 импульсов, первым входом блока 3 срав нения кодов, буферным устройством 4. Второй счетчик 5 импульсов соединен последовательно с блоком Q памяти со вторым входом блока 3 сравнения кодов. Входы синхронизации второго счетчика 5 импульсов, блока 6 памяти, делителя 7 частоты соединены со входной шиной. Генератор 1 опорной частоты соединен также с делителем 7 частоты, первый выход

которого соединен с вторым счетчиком 5 импульсов, а второй - с третьеим счетчиком 8 импульсов. Выход третьего счетчика 8 импульсов соединен с цешифратопром 9, прямой и инверсный выходы которого соединены соответственно с первыми входами элементов И Ю, 11. Выход буферного устройства 4 соединен со вторыми входами элементов И 10, 11, выходы которых соединены с входом установки в ноль и входом установки минус единих цы первого счетчика 2 импульсов соот- ветствен1 о. Вход установки минус единицы первого счетчика 2 импульсов соединен со счетным входом третьего счетчика 8 импульсов.

Работа предлагаемого устройства осуществляется следующим образом.

На вход устройства поступают сигналы; в виде узких импульсов, при этом обнуляется второй счетчик 5 импульсов, целитель 7 частоты, а также происходит перенос кода; содержащегося до поступления этого импульса во втором счетчике 5, в блок 6 памяти, а кода, содержащегося в делителе 7 частоты-в тре-, тий счетчик импульсов 8. Для этого делитель 7 частоты должен быть выполнен на основа цифрового счетчика импульсоб с переполнением. Код из блока 6 памяти поступает на один вход блока 3 сравнения кодов, на второй вход которого поступает код с первого счетчика 2 импульсов, заполняемого импупьсамигенератора 1 опор ной частоты, которые поступают также на делитель 7 частоты. Сигнад проходящий через делитель 7 частоты, от генератора опорной частоты 1 до второго счетчика 5 импульсов служит для образования в последнем кода, пропорционального периоду входной частоты, подлежащей умножению. Елок 3 сравнения кодов вырабатывает импульсный сигнал & момент равенства кодов на его входах. Этот сигнал поступает через буферное устройство 4 на входы элементов И 10, 11. При наличии не нулевого кода, пропорционального ошибке измерения периода вторым счетчиком 5 импульсов, в третьем счетчике 8 импульсов с дешифратора. 9 поступает разрешающий потенциал на вход элемента И 11. При этом выходной, сигнал буферного устройства 4 поступает на вход установки первого счетчика 2 импулсов, устанавливая последний в состояние минус единица и на вход третьего Счетчика 8 импульсов, работа которого органв зована на вычитание. Таким образом, происходит увеличение периода сигнале с

Авторы

Даты

1980-12-23—Публикация

1978-11-09—Подача