I

Изобретение относится к цифровой измерительной технике и может быть использовано для преобразования частоты следования импульсов.

Целью изобретения является повышение быстродействия.

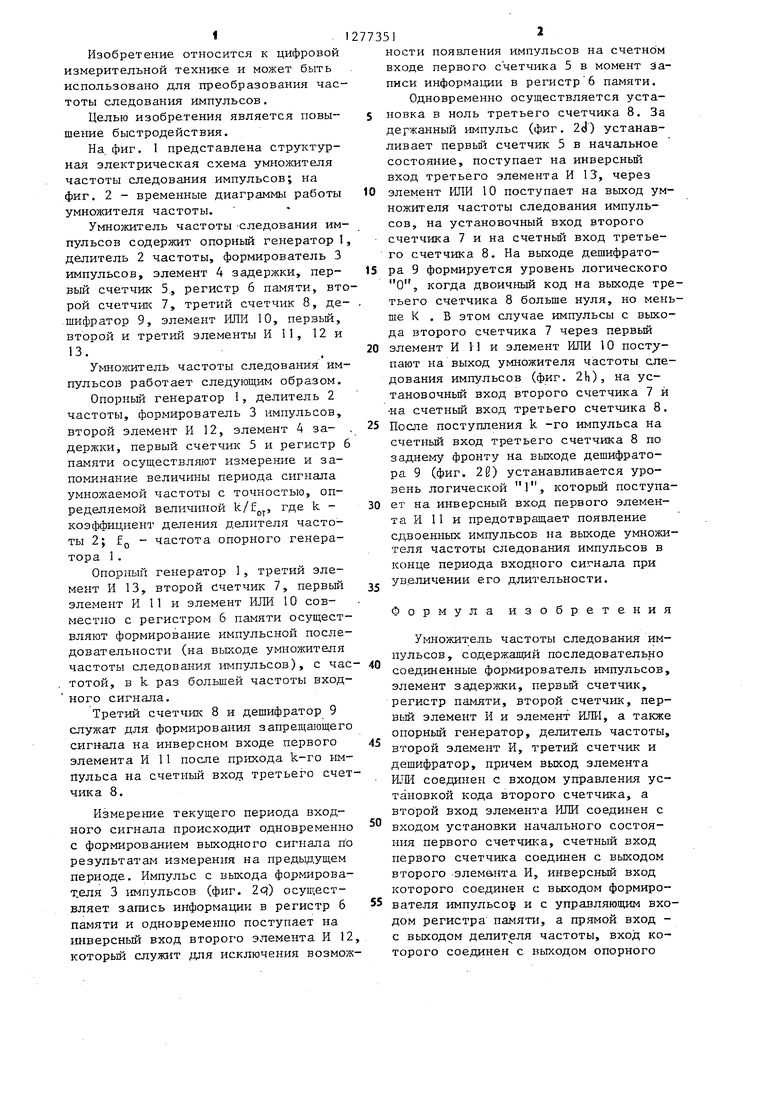

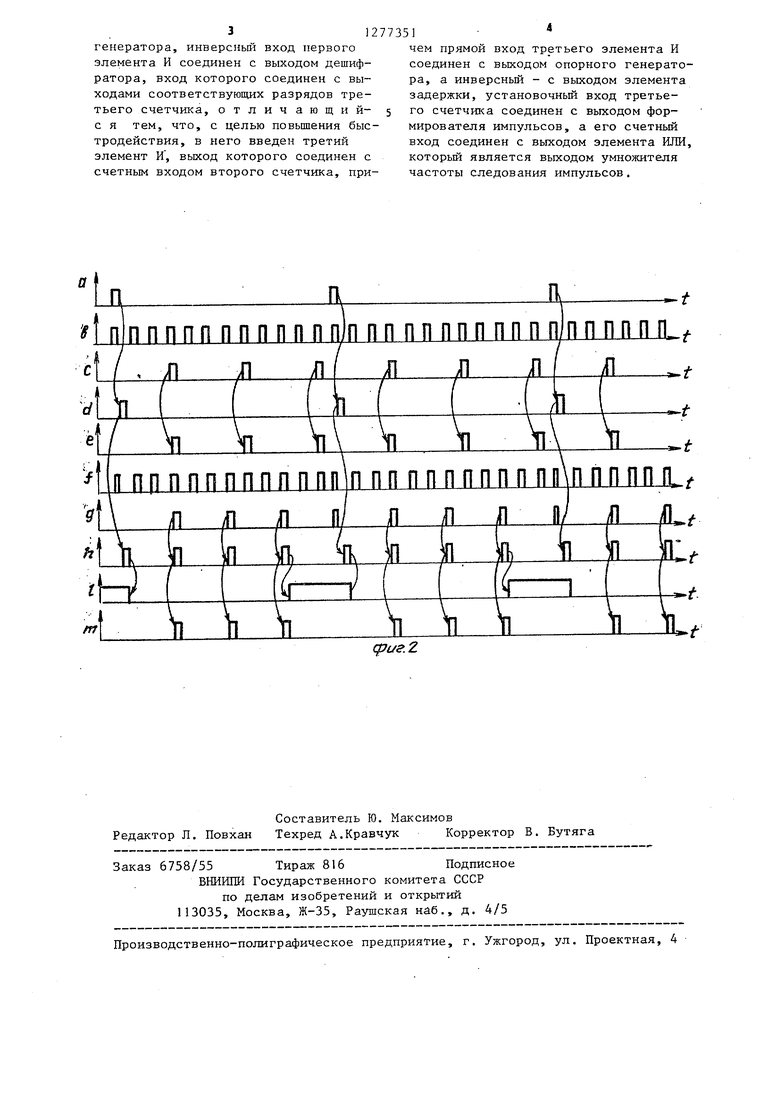

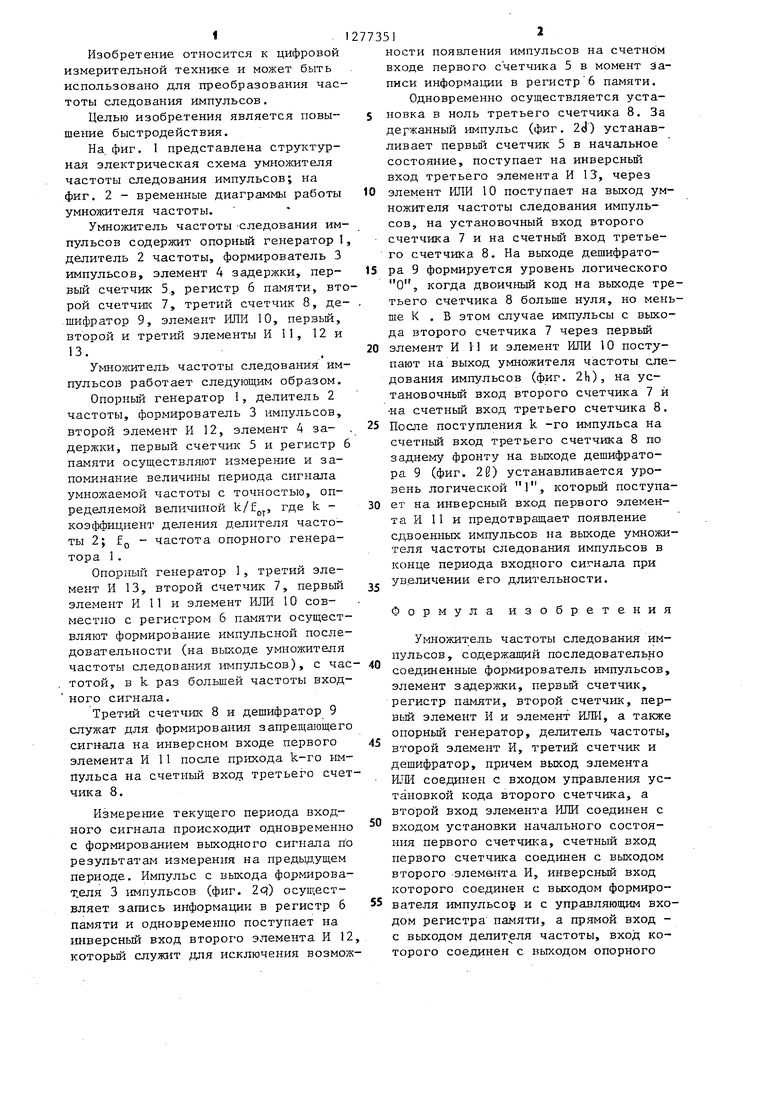

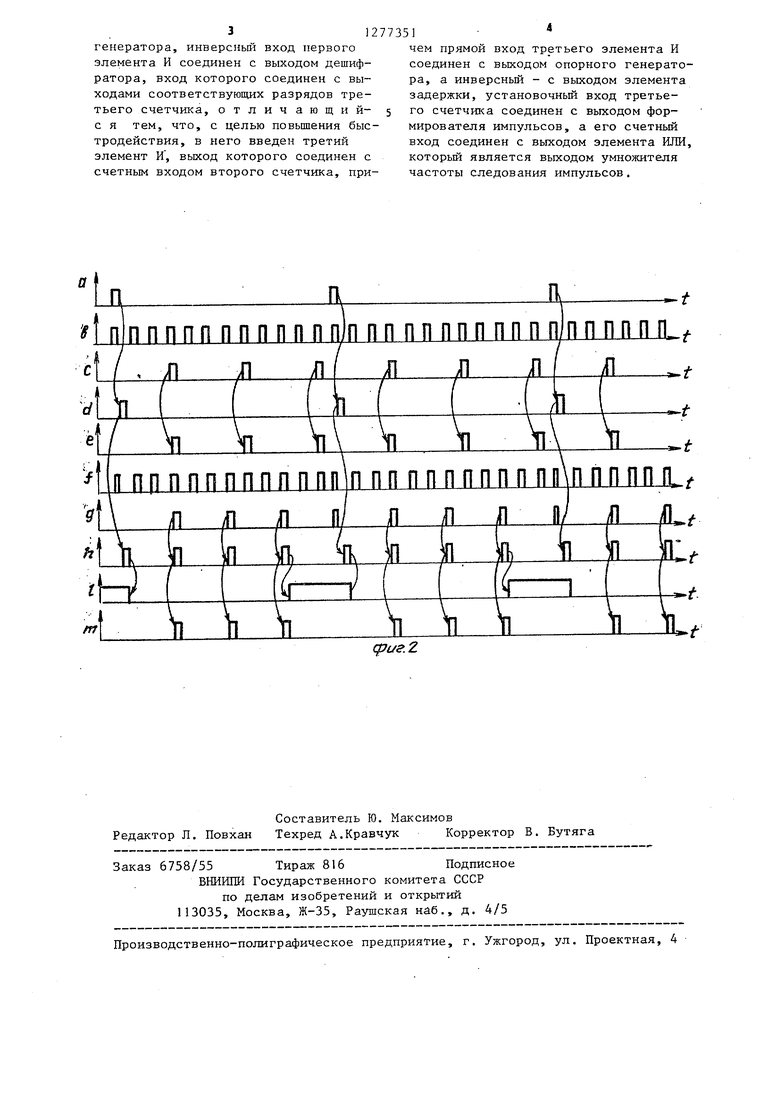

На, фиг. 1 представлена структурная электрическая схема умножит«шя частоты следования импульсов; на фиг. 2 - временные диаграммы работы умножителя частоты.

Умножитель частоты -следования импульсов содержит опорный генератор 1 делитель 2 частоты, формирователь 3 импульсов, элемент 4 задержки, первый счетчик 5., регистр 6 памяти, второй счб1тчик: 7, третий счетчик 8, де .шифратор 9, элемент ИЛИ 10, первьй, второй и третий элементы И 11, 12 и 13.

Умнолситель частоты следования импульсов работает следующим образом.

Опорный генератор 1, делитель 2 частоты, формирователь 3 импульсов, второй элемент И 12, элемент 4 за- дерлски, первый счетчик 5 и регистр 6 памяти осуществляют измерение и запоминание величины периода сигнала умножаемой частоты с точностью, определяемой величиной ,-j) где k - коэ(1)фициент деления делителя частоты 2; fg - частота опорного генератора 1 .

Опорный генератор 1, третий элемент И 13, второй счетчик 7, первьш элемент И 11 и элемент ИЛИ 10 совместно с регистром б памяти осуществляют формирование импульсной последовательности (на выходе умножителя частоты следования импульсов), с частотой, в k раз большей частоты входного сигнала.

Третий счетчик 8 и дешифратор 9 служат для формирования запрещающего сигнала на инверсном входе первого элемента И 11 после прихода k-ro импульса на счетный вход третьего счетчика 8.

Измерение текущего периода входного сигнала происходит одновременно с формированием выходного сигнала по результатам измерения на предыдущем периоде. Импульс с выхода формирова- т.еля 3 импульсов (фиг. 2я) осуществляет запись информации в регистр 6 памяти и одновременно поступает на шшерсньй вход второго элемента И 12 который служ11т для исключения возмож

77351

ности появления импульсов на счетном входе первого счетчика 5 в момент записи информаи 1и в регистр 6 памяти. Одновременно осуществляется уста5 новка в ноль третьего счетчика 8. За держанный импульс (фиг. 2d) устанавливает первьп4 счетчик 5 в начальное состояние, поступает на инверсный вход третьего элемента И 13, через

10 элемент ИЛИ 10 поступает на выход умножителя частоты следования импульсов, на установочный вход второго счетчика 7 и на счетньй вход третьего счетчика 8. На выходе дешифрато15 ра 9 формируется уровень логического О, когда двоичный код на выходе третьего счетчика 8 больше нуля, но меньше К . В этом случае импульсы с выхода второго счетчика 7 через первый

20 элемент И 1 и элемент ИЛИ 10 поступают на выход умножителя частоты следования импульсов (фиг. 2h), на ус- тановочньй вход второго счетчика 7 и на счетньш вход третьего счетчика 8.

25 Поате поступления k -го импульса на счетньй вход третьего счетчика 8 по заднему фронту на выходе дешифратора 9 (фиг. 2S) устанавливается уро

вень логической 1, которьй поступает на инверсный вход первого элемента И 11 и предотвращает появление сдвоенных импульсов на выходе умножителя частоты следования импульсов в конце периода входного сигнала при увеличении его длительности.

Формула изобретения

Умножитель частоты следования импульсов, содержащий последовательно соединенные формирователь импульсов, элемент задерж1си, первьй счетчик, регистр памяти, второй счетчик, первый элемент И и элемент ИЛИ, а также опорный генератор, делитель частоты, второй элемент И, третий счетчик и дешифратор, причем вькод элемента ИЛИ соединен с входом управления установкой кода второго счетчика, а второй вход элемента ИЛИ соединен с входом установки начального состояния первого счетчика, счетный вход первого счетчика соединен с выходом второго элемента И, инверсньй вход которого соединен с выходом формирователя импульсо5 и с управляющим входом регистра памяти, а прямой вход - с выходом делителя частоты, вход которого соединен с выходом опорного

генератора, инверсный вход первого элемента И соединен с выходом дешифратора, вход которого соединен с выходами соответствующих разрядов третьего счетчика, отличающий- с я тем, что, с целью повышения быс тродействия, в него введен третий элемент И, выход которого соединен с счетным входом второго счетчика, при77351

чем прямой вход третьего элемента И соединен с выходом опорного генератора, а инверсный - с выходом элемента задержки, установочный вход третьего счетчика соединен с выходом формирователя импульсов, а его счетный вход соединен с выходом элемента ИЛИ, который является выходом умножителя частоты следования импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой умножитель частоты следования импульсов | 1980 |

|

SU1013952A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Цифровой умножитель частоты следования импульсов | 1984 |

|

SU1226604A1 |

| Дискретный умножитель частоты | 1985 |

|

SU1337988A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1012431A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

Изобретение относится к цифровой измерительной технике и обеспечивает повышение быстродействия. Опорный генератор (ОГ) 1, делитель частоты 2, элемент И 12, элемент задержки 4, счетчик 5 и регистр памяти 6 осуществляют измерение и запоминание величины периода сигнала умножаемой частоты. ОГ 1, элемент И 13, регистр памяти 6, счетчик 7, элементы И 11, ИЛИ 10 осуществляют формирование импульсной последовательности с частотой, в К раз большей частоты входного сигнала. Счетчик 8 и дешифратор 9 формируют запрещающий сигнал на инверсном входе элемента И 11 после прихода k-ro импульса на счетный вход счетчика 8. Измерение текущего периода входного сигнала происходит одновременно с формированием выходного сигнала по результатам измерения на предьдущем периоде. Быстродействие повьщ1ается за счет введения элемента И 13 и подключения счетного входа счетчика 8 к выходу элемента ИЛИ 10. 2 ил. i (Л С

пппппппппппшпппппппппппп

п п п п п п

f

п пппппппппппп

ПППППППППППП ППППП 1

«

fff

л

i

сриг.2

Составитель Ю. Максимов Редактор Л. Повхан Техред А.Кравчук Корректор В. Бутяга

Заказ 6758/55 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Цифровой умножитель частоты | 1979 |

|

SU799146A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-04-10—Подача