1

Изобретение относится к вычислительной технике и автоматике и может найти применение при реализации технических средств в этих областях. Известно триггерное устройство (ТУ-триггер), содержащий установочны триггер, два элемента И-НЕ, два элемента задержки, тактовую и управляющую шины.f1.

Недостатком такого устройства является то, что оно не может использоваться для выполнения задачи управления прохождения потоков информации

Наиболее близким к предлагаемому является триггерное устройство, содержащее группу тактовых шин, шины установки в единицу и в ноль, две группы элементов И-НЕ (по количеству тактовых шин), два дополнительных элемента И-НЕ, два элемента И и два элемента задержки, причем выход первого элемента И соединен со входом первого элемента задержки и с первым входом первого дополнительного элемента И-НЕ, второй вход которого соединен с шиной установки в единицу, выход второго элемента И соединен со входом- второго элемента задержки и с первым входом второго дополнительного элемента И-НЕ, второй вход которого соединен с шиной установки в ноль, выходы первого и второго элементов задержки соединены с первыми входами элементов И-НЕ соответственно первой и второй группы, вторые входы элементов И-НЕ первой группы соединены со вторыми входами элементов И-НЕ второй группы и соединены соответственно с группой тактовых шин, выходы элементов И-НЕ первой группы, выход второго дополнительного элемента И-НЕ и выходы элементов И-НЕ второй группы, выход первого дополнительного элемента ИИ-НЕ соединены соответственно со входами первого и второго элементов И. Устройство служит для пересчета импульсов, поступающих от нескольких абонентов C lНедостаток известного устройства отсутствие возможности управлять прохождением потоков информации. Цель изобретения - расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что в триггерное устройство, содержащее группу тактовых шин, шины установки в единицу и в ноль, два

элемента И-НЕ и два элемента задержки, вход первого из которых соединен с инверсным выходом первого логического блока И;с первым входом первого элемента И-НЕ, второй вход которого соединен с шиной установки в единицу вход второго цемента задержки соединен с инверсным выходом второго логического блока и с первым входом |Второго элемента И-НЕ, второй вход которого соединен с шиной установки в ноль, введены группа управляющих шин, два сумматора по модулю два и лгические блоки, выполненные в виде мультиплексоров, первые входы первог и второго сумматоров по модулю два соединены соответственно с выходами первого и второго элементов задержки входы разрешения первого и. второго мультиплексоров соединены соответственно с выходами второго и .первого элементов И-НЕ, выходы первого и второго сумматоров по модулю два соединены с младшими селекторными входами соответственно первого и второго мултиплексороВд группа управляющих шин соединена соответственно с объединенными вторыми входами сумматоров по модулю два и объединенными одноименными старшими селекторными входами мультиплексоров, одноименные информационные входы которых объединены и соединены соответственно с группой тактовых шин.

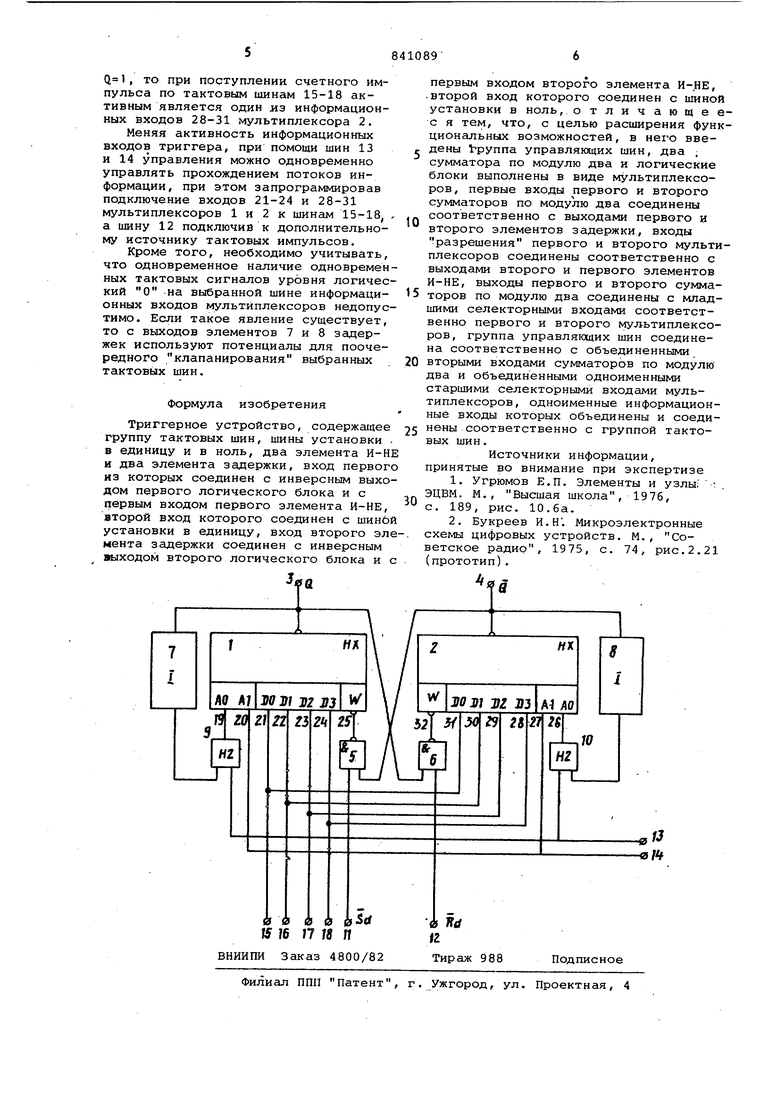

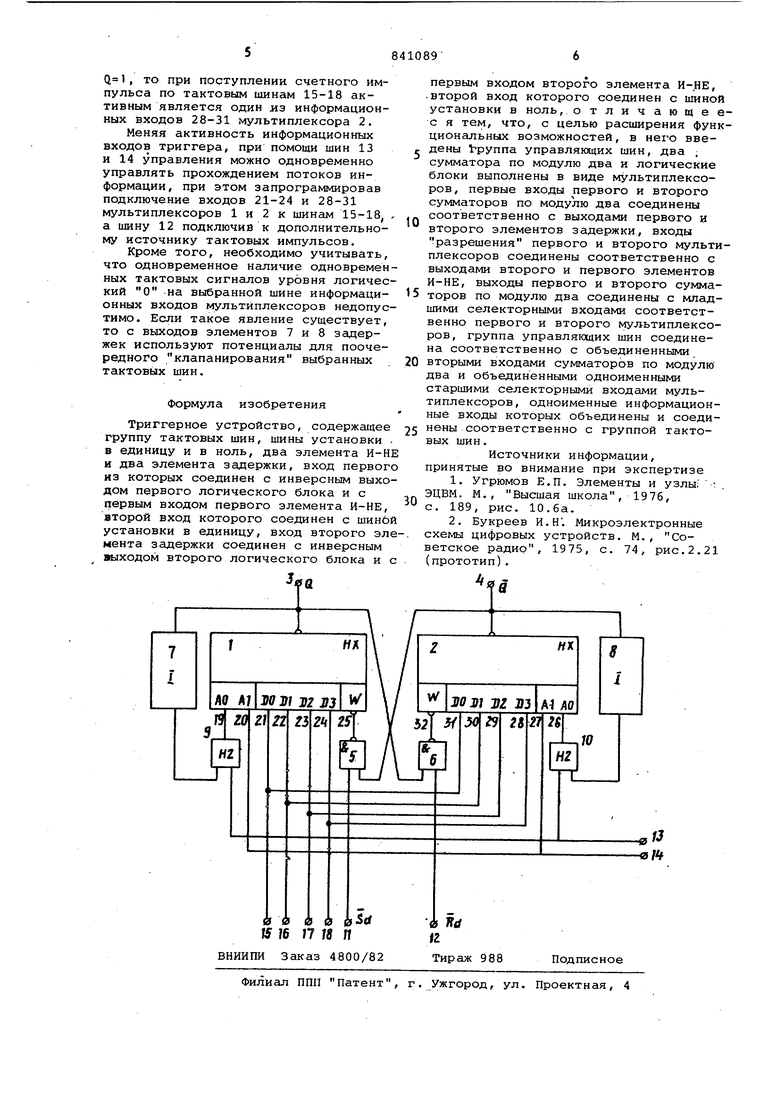

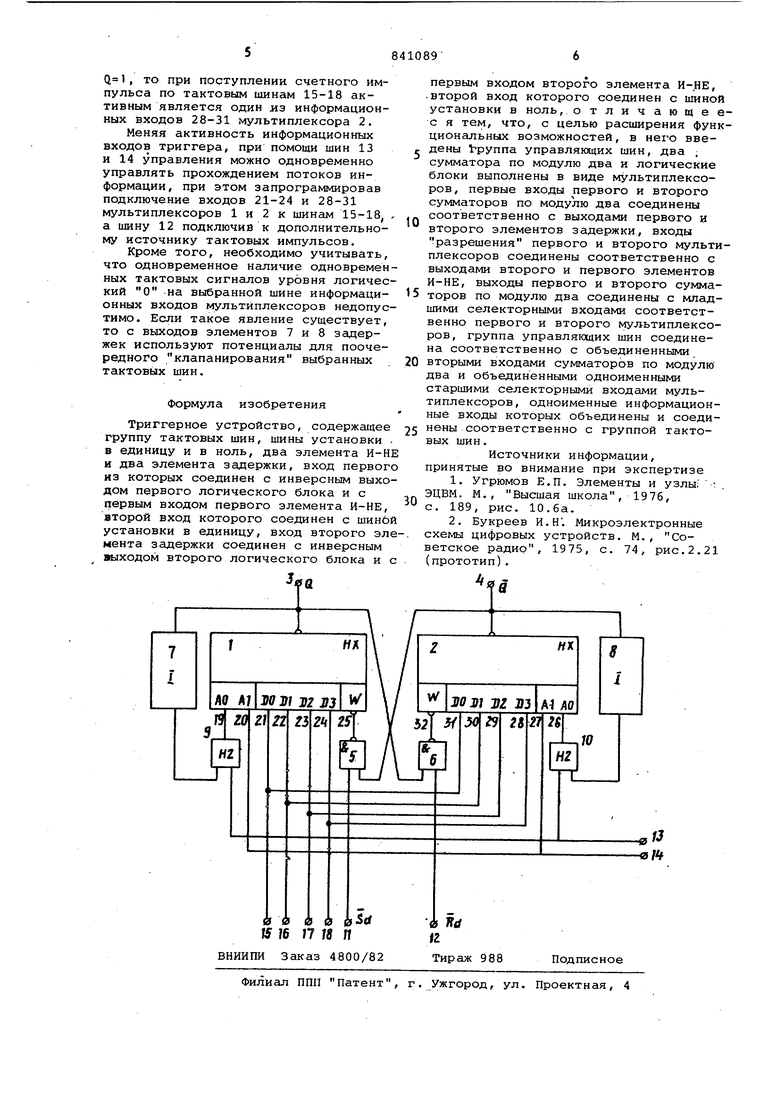

На чертеже приведена электрическа схема триггерного устройства.

Предлагаемое устройство содержит мультиплексоры 1 и 2, прямой 3 и инверсный 4 выходы триггерного устройства, элементы 5 и 6 И-НЕ, элементы 7 и 8 задержки, сумматоры 9 и 10 по модулю.два, шины 11 и 12 установки соответственно в .единицу и в ноль, управляющие шины 13 и 14, тактовые шины 15-18, младший 19 и старший 20 селекторные входы мультиплексора 1, информационные входы 21-24 мультиплексора 1, вход 25 разрешения мультиплексора 1, младший 26 и старший 27 селекторные входы мультиплексора 2, информационные входы 28-31 мультиплексора 2 и вход 32 разрешения мультиплексора 2. При этбм прямой выход 3 соединен с первым входом б элемента И-НЕ и через элемент 7 задержки с первым входом 9 сумматора по модулю два, инверсный выход 4 соединен с первым входом 5 элемента И-JtlE и через элемент 8 задержки с первым входом 10 сумматора по модулю два, вторые входы 5 и 6 элементов И-НЕ соединены соответственно с шиной 11 установки в единицу и шиной 12 установки в ноль, управляющие шины 13 и 14 соединены соответственно со вторыми входами 9 и 10 сумматоров по модулю два и старшими селекторными входами 20 и 27, тактовые шины 15-18 соединены соответственно с информационныгли входами 21-24 мультиплексора 1 и с информационными входами 31, 30, 29 и 28 мультиплексора 2, входы 25 и 32 разрешения мультиплексоров 1 и 2 соединены соответственно с выходами 5 и б элементов И-НЕ.

Устройство работает следующим образом.

В исходном состоянии на шинах 11 и 12, 15-18 присутствуют потенциалы логическая 1, а на шинах 13 и 14 некоторая комбинация двоичного кода, причем как на активных (выбранных), так и на пассивных (невыбранных) входах мультиплексоров 1 и 2, присутствуют потенциалы логическая 1. При подаче потенциала логический О по шине- 12 установки в ноль на выходе б элемента И-НЕ появляется потенциал логическая 1 (если на выходах мультиплексоров 1 и 2 были состояния соответственно логическая 1 и логический О), который блокирует мультиплексор 2, и на его выходе появляется потенциал логическая 1, поступавший на вход 5 элемента И-НЕ, вызывает на его выходе потенциал логический О, который разрешает функционирование мультипл.ексора 1, и на выходе последнего появляется инвертированное состояние одного из разрешенных информационных входов, т.е. логический О.

Таким образом, на прямом 3 и инверсном 4 выходах триггерного устройства присутствует нулевое состояние триггерного устройства, т.е. и

5 . Это состояние устойчивое, так как сигнал блокировки на входе 32 мультиплексора 2 сохраняется при снятии потенциала логический О с шины 12. При этом, если на шинах управления 13 И 14 - логическая 1, то активными (выбранными) для мультиплексора 1 является шина 18, а для мультиплексора 2 - шина 16, поскольку на селекторных входах 19 и 20 мультиплексора 1 присутствует код 11, а на селекторных входах 26 и 27 мультиплексора 2 - код 10.

Для устройства в целом при потенциалах, например, логическая 1 на всех шинах 13 и 14 управления активным является только вход 24 мультиплексора 1, так как с приходом каждого тактового импул са только по этому входу инвертируется ранее записанная в триггерном устройстве информация. Поскольку эта операция эквивалентна прибавлению логической 1 к коду ранее записанной в триггере информации, предлагаемое триггерное устройство осуществляет счет импульсов, подаваемых на его активный вход, причем если , то при поступлении счетного импульса по тактовым шинам 15-18 активным является один из информационных входов 21-24 мультиплексора 1, если , то при поступлении счетного импульса по тактовым шинам 15-18 активным является один из информационных входов 28-31 мультиплексора 2. Меняя активность информационных входов триггера, при помощи шин 13 и 14 управления можно одновременно управлять прохождением потоков информации, при этом запрограммировав подключение входов 21-24 и 28-31 мультиплексоров 1 и 2 к шинам 15-18, а шину 12 подключив к дополнительному источнику тактовых импульсов. Кроме того, необходимо учитывать, что одновременное наличие одновремен ных тактовых сигналов уровня логичес кий О -на выбранной шине информационных входов мультиплексоров недопус тимо. Если такое явление существует, то с выходов элементов 7 и 8 задержек используют потенциалы для поочередного клапанирования выбранных тактовых шин. Формула изобретения Триггерное устройство, содержащее группу тактовых шин, шины установки в единицу и в ноль, два элемента И-Н и два элемента задержки, вход перво из которых соединен с инверсным выхо дом первого логического блока и с первым входом первого элемента второй вход которого соединен с шинб установки в единицу, вход второго эл мента задержки соединен с инверсным шлходом второго логического блока и первым входом второго элемента И-НЕ, второй вход которого соединен с шиной установки в ноль, отличающеес я тем, что, с целью расширения функциональных возможностей, в него введены tpynna управляющих шин, два , сумматора по модулю два и логические блоки выполнены в виде мультиплексоров, первые входы первого и второго сумматоров по модулю два соединены соответственно с выходами первого и второго элементов задержки, входы разрешения первого и второго мультиплексоров соединены соответственно с выходами второго и первого элементов И-НЕ, выходы первого и второго сумматоров по модулю два соединены с младшими селекторными входами соответственно первого и второго мультиплексоров, группа управляющих шин соединена соответственно с объединенными вторыми входами сумматоров по модулю два и объединенными одноименными старшими селекторными входами мультиплексоров, одноименные информационные входы которых объединены и соединены соответственно с группой тактовых шин. Источники информации, принятые во внимание при экспертизе 1.Угрюмов Е.П. Элементы и узлы; : ЭЦВМ. М., Высшая школа, 1976, с. 189, рис. 10.6а. 2.Букреев И.Н. Микроэлектронные схемы цифровых устройств. М., Советское радио, 1975, с. 74, рис.2.21 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для умножения по модулю 2 @ -1 | 1985 |

|

SU1304019A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Генератор случайной последовательности | 1989 |

|

SU1640687A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

Авторы

Даты

1981-06-23—Публикация

1979-09-27—Подача