Изобретение относится к измерительной технике и может быть использо вано для измерения мгновенных, амплитудных , средних,средневыпрямленных, действующих значений напряжений или их отклонений от номинальных значений. Известен цифровой вольтметр действующего значения переменного напряжения, содержащий ключи, интеграторы, блоки сравнения, триггер, блок извле чения корня и измеритель интервала времени Ill Недостатками, устройства являются низкая точность, так как для получения действуквдего значения входное на пряжение три раза интегрируется, вклю ченными последовательно- интеграторАми, погрешность от несимметричности формы измеряемого напряжения, низкое быстродействие, так как необходимо время для многократного разряда первых двух интеграторов в течение периода . Цель изобретения - повышение точности и быстродействия преобразовани Поставленная цель достигается тем JTO ваналого-цифровой, преобразователь содержащий, первый И второй ключ 1ервый и второй интеграторы,, блок сравнения, первый вход которого соединен с общей шиной, а выход - с блоком управления, источник опорного напряжения, . введены третий ключ, инвертор, цифроаналоговый преобразователь, аналоговый запоминающий блок, коммутатор, узел управления, .включа рщий логичес-.-, кий блок,параллельный и последовательный регистры, причем шина входного сигнала соединена с первым входом и через инвертор со вторым входом коммутатора, к выходу,которого подключены последовательно соединенные блок сравнений, первый ключ, аналоговый запоминающий блок, второй ключ, цифроаналоговый преобразователь, первый |1нтегратор, третий ключ, второй интегратор, выход которого соединен с пятым входом коммутатора, четвертый вход которого соединен с первым входом второго ;ключа, второй вход которого соединен с источником опорного напряжения и с седьмым входом коммутатора, третий вход которого соединен С выходом первого интегратора, а шестой вход - со входом первого интегратора и вторым входом третьего, клю ча, при этом последовательный и параллельный регистры и логический блок последовательно соединены между собой.

причем выход логического блока соединен с -управляющим входом цифроаналогового преобразователя, а управляющие входы коммутатора, первого, второго И третьего ключей, первого и второго интегратора и логического блока соединены соответственно с выходами . блока управления.

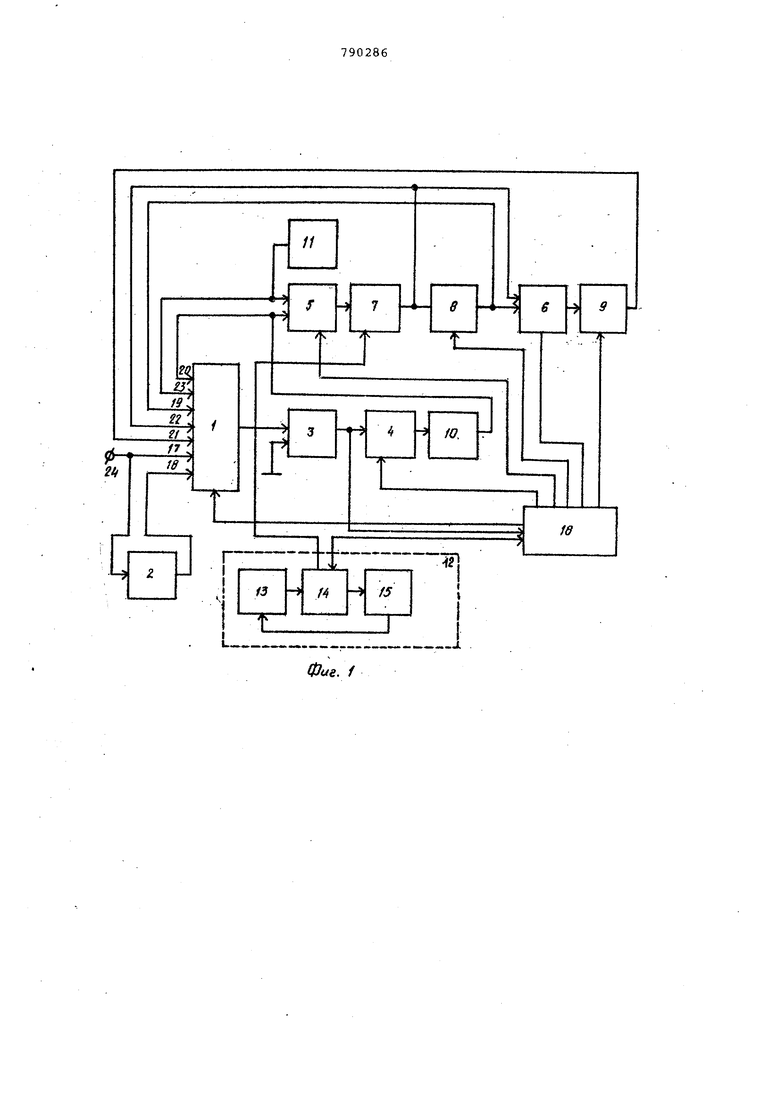

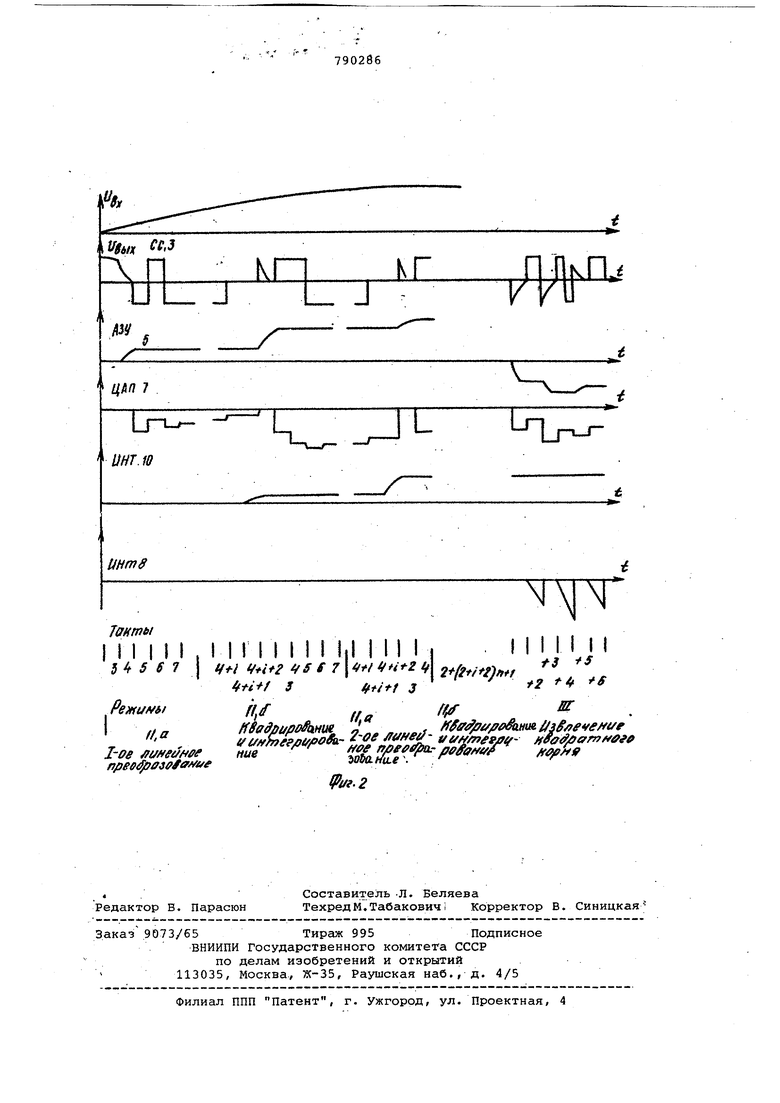

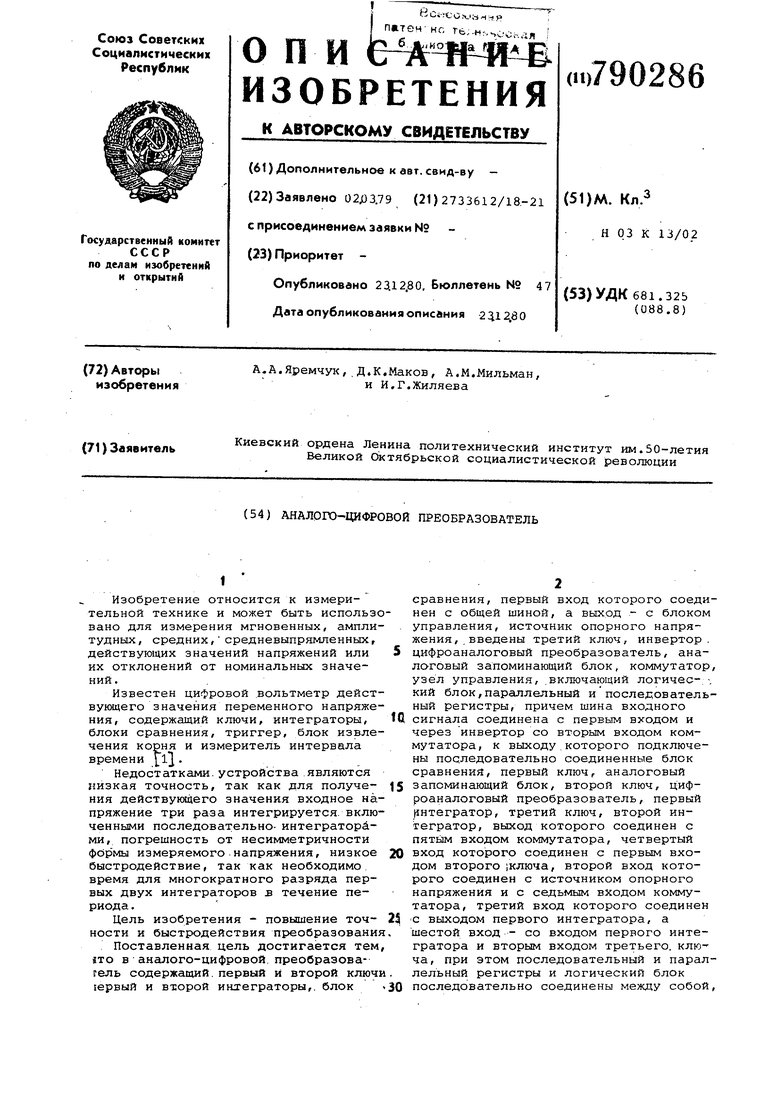

На фиг. 1 представлена структурная электрическая схема аналого-цифрового преобразователя, на фиг. 2 временные диаграммы работы.

Устройство содержит коммутатор 1, инвертор 2, блок 3 сравнения, первый, второй и третий ключи 4, 5 и 6, цифроаналогоэый преобразователь (ЦАП) 7, первый и второй интеграторы 8 и 9, аналоговый запоминающий блок 10, ис-. точник 11 опорного напряжения,, узел 12 управления, параллельный регистр 13, логический блок 14, последовательный регистр 15, блок 16 управления, входы 17...23 коммутатора, входную шину 24.

Работа аналого-цифрового преобразователя основана на обработке дискретизированных во врэмени мгновенных значений и осуществляется в трех режимах :

1) подготовительный, 2J формирование напряжения, пропорционального сумме квадратов, дискретизированных во времени мгновенных , значений, 3) извлечение корня.

Аналого-цифровой преобразователь работает следующим образом.

1 режим

1такт. По команде от блока управления все блоки преобразователя устанавливаются в исходное состояние, ключи 4,5,6 закрыты. Коммутатор открыт

по входу 17 и подает входное напряжение 1 на блок сравнения, выполненный на операционном усилителе.

2такт. Блок сравнения.выделяет период Тд-1/fx измеряемого напряжения передает информацию о периоде Г в блок управления, который осуществляет подстройку частоты измерения дискретных во времени мгновенных значений измеряемого напряжения Ух

в соответствии с выражением fij)j.. где f чийУю измеряемых дис кретных мгновенных значений (ti-conat)

И режим:а)линейное преобразованиев такт. Блок сравнения определяет полярность напряжения Uy и управляет через 6JIOK управления состоянием коммутатора по входу 18, к которому подключается входное напряжение через инвертор скоэффициентом гюредачи .

4 такт. Блок управления управляет входами 17 и 18 коммутатора таким образом, ЧТО напряжение на выходе ком. мутатора равно lUyl , т.е. осуществляется двухполупериодное выпрямление. При этом открыты ключ 4 и коммутатор по входу 20, образуя замкнутую аналоговую запоминающую ячейку,состоящую из блока сравнения и аналоговог запоминающего блока 10.В этом такте осуществляется слежение .замкнутой анлоговой запоминающей ячейкой за напржением )Ux) .С пятого по{4+1)такты осуществляется поразрядное аналого.цифровое преобразование первого мгновенного значения 1 Ux, Ц в i -раэрядЬый двоичный кед.

5такт. Производится сравнейие напряжения, соответствующего старшему (i) разряду цифроаналогового. преобразователя с измеряемым мгновенным значением f j . Первый ключ 4 закрыт, второй ключ 5 открыт по второму входу, соединенному с источником опорного напряжения. Коммутатор открыт по входам 20 и 22. В последовательный регистр 15 узла 12 управления порязрядным аналого-цифровой преобразвателем по команде от блока управления через логический блок 14 записывается логическая единица 1 в старший разряд, которая затем переписы- . вается в параллельный регистр 13. Параллельный регистр через логический блок управляет цифроаналоговым преобразователем. После окончания переходных процессов блок сравнения сравнивает напряжение с выхода аналогового запоминающего блока 10 и напряжение с выхода цифроаналогового преобразователя 7, соответствующее напряжению старшего разряда цифроаналогового преобразователя т.е. формируется код О.

6такт. Записывается информация (код ai) о старшем t разряде кода измеряемого мгновенного значения

1 Uj( I в параллельный регистр 13, выделяется информация о втором по величине разряде кода измеряемого мгновенного значения lUyj) При U 7,U в старшем разряде параллельного регистра 1.3 записывается логическая единица 1. При во всех разрядах параллельного регистра 13 сохраняются логические нули.,В последовательном регистре 15 в шестом такте осуществляется сдвиг логической единицы в следующий младший разряд. Затем производится запись сдвинутой единицы во второй разряд регистра 13 После окончания переходных процессов блок сравнения сравнивает напряжения с выхода запоминающего блока 10 U, и цифроаналогового преобразователя U

7такт. Записывает;ся информация о втором по величине разряде кода измеряемого мгновенного значения в параллельный регистр 13, выделяется информация о третьем по величине разряде кода измеряемого мгновенного значения (4+ tj такт. Записывается информация о предпоследнем ,по величине разр де кода измеряемого мгновенного значения в параллельный регистр 13, выделяется информация о самом младшем по величине разряде кода измеряемого мгновенного значения | Uy«|Таким образом, в (4+1+1) такте в параллельном регистре 13 будет код, пропорциональный измеряемому мгновен ному значению DX | , а напряжение на выходе цифроаналогового преобразо Ьателя можно представить в виде р-Чиоп и,,-ли-ли„ где Uon напряжение источника опорного напряжения, Q; : - коэффициенты i,-разрядов / принимающие значения О или ли - порог срабатывания блока сравнения, UU); - погрешность от квантования I режим:б квадрирование и интегрирование 4 + t+l) такт. Формируется напряжение, пропорциональное квадрату измеряемого мгновенного значения. Первый ключ 4 закрыт, второй ключ 5 открыт по первому входу, соединенному с выходом аналогового запоминающего блока 10. Коммутатор закрыт по всем входам. На выходе цифроаналогового преобразователя 7 после окончания пе реходных процессов напряжение будет пропорционально квадрату напряжения первого измеряемого мгновенного значения:и„--р-а,и,,и,и,,/ид (U,,-AU-iU,)U,,. (4 + 1+2 такт. Интегрируется в течение фиксированного промежутка времени напряжение U, , пропорциональное квадрату первого измеряемого мгновенного значения. Второй ключ 5 открыт по своему первому входу, третий ключ б открыт по второму входу, соединенному с выходом цифроаналогового преобразователя. Получаем напряжение постоянна времени интегратора 9.. По окончании интегрирования все ключи закрываются коммутатор открытпо первому входу, аналого-цифровой преобразователь переходит снова в третий такт. Аналого цифровой преобразователь отслеживает измеряет второе из п мгновенных значений lUxij l /формирует напряжение U | пропорциональное ква/;рату второго из меряемого мгновенного значения U,. . Напряжение интегрируется интегратором 9 в течение интервала времени t . Напряжение U22 после второго интегрирования можно записать как U2i- iu a.()t где К - коэффициент пропорциональности. После окончания второго интегрирования аналого-цифровой преобразователь снова переходит в третий такт. 2+(2+1 + 2)п такт. После преобразо.вания И- дискретных мгновенных значений напряжение Uy, на выходе интегратора 9 можно выразить: V . режим:извлечение корня в, неявном виде 2+(2+с +2)п+1 такт. По команде от блока 16 управления и узла 12 управ ления в старший разряд последователь ного регистра 15 записывается логическая единица 1, коммутатор открыт по входам 20 и- 22. Первый ключ 4 открыт. Второй ключ 5 открыт по второму входу. Замкнутая аналоговая запоминающая ячейка отслеживает напряжение р Uon старшего разряда цифроаналогового преобразователя 7. { 2+(2+t+2)ti+2| такт. Формируется напряжение ( Uon) пропорциональное квадрату напряжения старшего разряда цифроаналогового преобразователя путем переключения ключа -5 к выходу аналогового запоминаюгдего блока после отключения ключа 4 ( К U,)Напряжение (X2 UOP) интегрируется первым интегратором 8 в течение времени twHT- Напряжение на выходе первого интегратора 8 после интегрирования можно представить так: .r(,i/T;, где Т - постоянная времени первого интегратора 8. В конце такта осуществляется сравнение блоком сравнения напряжений U соответственно с выходов первого 8 и второго 9 интеграторов, поступающих через входы 19 и 21 коммутатора, и блоком сравнения формируется код Ъ о старшем (г разряде действующего значения. При этом первый ключ 4 закрыт, второй ключ 5 открыт по первому входу, коммутатор открыт по входам 19 и 21. : ) 2+(2+i:+2)n+3 такт. Записывается код о старшем разряде измеряемого . действующего значения в парал-. лельный регистр 13. При Ьщ Ung в старший (7, разряд параллельного регистра 13 записывается логический нуль О, при обратном неравенстве логическая единица 1 т.е. формируется код bj . В последовательном регистре 15 логическая единица сдвигается во второй разряд .и переписывается в регистр J.3.. Формируется напряжение Uon (.Ь 2С 2 ) Коммутатор открыт по входам 20 и 22, первый . ключ 4 открыт. Замкнутая аналоговая запоминающая ячейка отслеживает на пряжение Uon( ). j 2-4-(2+t+2)п+4(. Формируется напряжение K%cn(6ir г-) которое интегрируется первым интегра тором 8 в течение времени t . Напряжение на выходе первого интегратора 8 после интегрирований можно предста вить U,.2-.2-)t/7; В конце такта осуществляется срав нение 6Л9КОМ 3 напряжений UM с выходов соответственно первого 8 и второго 9 интеграторов. Первый ключ закрыт, второй ключ 5 открыт по перв му входу, коммутатор открыт по входам 19 к 21. Блоком сравнения формируется инфо мация Ъ.1 о втором по величине разряде кода действующего- значения. I 2+(2+1 +2)п +2+ I )/ ..такт.. Формируетk: М fS 2) ся напряжение 2 сп jT -t которое интегрируется первым интех-ра тором 8 в течение времени t. Напряжение на выходе первого интегратора 8 после интегрирования можно предста вить в виде .r-Cn(Xbi2- 2)4H/T;. в конце такта осуществляется срав нение блоком 3 напряжений И UMZ с выходов ссотвественно первого и вт рого интеграторов. Первый ключ 4 зак второй ключ 5 открыт по первому входу, коммутатор открыт по входам 19 И 21. Блоком сравнения формируется информация о младшем по величине раз-ряде кода действующего значения. Таким рбразог получаем uJ,(ti,.2-)4/i;si bsr fe,, d USn Т„ т.е.код,полученный.в параллельном ре гистре 13,пропорционален действующем значению напряжения. Аналого-цифровой-преобразователь позвфляет измерять мгновенные, ампли тудные, средние, средневыпрямленные и действующие значения переменного н , отклонение, перечисленных значений от номинального, значения. Устройство обладает более высокими метрологическими .характеристиками, так как при измерении.суммы квадрато мгновенных значений .используется оди интегратйр вместо трех, что уменьшает погрешность из-за дрейфа, устраняется .апертурная погрешност.ь, отсутствует погрешность от нессиметричности формы измеряемого напряжения. Кроме того, заявляемое устройство обладает большим быстродействием, т.к. в нем устраняется интервал времени, необходимый на разынтегрирование, что позволяет повысить частоту дискретизации. Требования к долговременной стабильности генератора невысоки. Формула изобретения Аналого-цифровой преобразователь, содержащий первый и второй ключи, первый и второй интеграторы, блок сравнения, первый вход которого соединен с общей шиной, а выход - с блоком управления, источник.опорного напряжения, отличающийся тем, что, с целью повышения точности и быстродействия введены третий ключ инвертор, цифроаналоговый преобразо- ватель, аналоговый запоминающий блок коммутатор,, узел управления, в ключ ающий логический блок, параллельный и последовательный регистры,.причем шина входного сигнала соединена спервым входом и через инвертор со вторым входом коммутатора,к выходу которого подключены последовательно соединенные блок сравнения, первый ключ, аналоговый запоминающий блок, второй ключ, цифроаналоговый преобразователь, первый интегратор, третий ключ, второй интегратор, выход которого соединен с пятым входом коммутатора , Четвертый вход которого соединен -с первым входом второго ключа, второй вход которого соединен с источником опорного напряжения и с седьмым входом коммутатора, третий вход которого.соединен с выходом первого интегратора, а шестой вход - со входом первого интегратора и вторым входом третьего ключа, при этом подледо вательный и параллельный регистры и ,,логический блок последовательно соедин ены между собой, причем выход логи4eckoro блока соединен с управляющим входом цифроаналогового преобразователя/ а управляющие входы коммутатора первого, второго и третьего ключей, первого,и второго интегратора и логического блока соединены соответственно с выходами блока управления. Источники информации, принятые во внимание при .экспертизе . 1. Авторское свидетельство СССР № 343226,кл.-и; 01 R 19/26, 10.06.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

| Цифровой вольтметр среднеквадратического значения переменного напряжения | 1988 |

|

SU1652933A1 |

| Дискретно-аналоговый фурье-преоб-РАзОВАТЕль | 1979 |

|

SU813307A1 |

| Электроразведочная станция | 1987 |

|

SU1469489A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197079A1 |

| Устройство для преобразования перемещения в код | 1981 |

|

SU978174A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Способ преобразования кода угла в напряжения,пропорциональные синусу и косинусу угла,и устройство для его осуществления | 1983 |

|

SU1136327A1 |

Авторы

Даты

1980-12-23—Публикация

1979-03-02—Подача