10

15

f 1256206

Изобретение относитсяГ к вычисли- тельной технике и может быть использовано в различных информационно-измерительных системах, к которым предъявляются повышенные требования к достоверности получаемых рёзуль- татой

Цель изобретения - повьшение помехоустойчивости и расширение функциональных возможностей путем обеспечения контроля процесса преобразования.

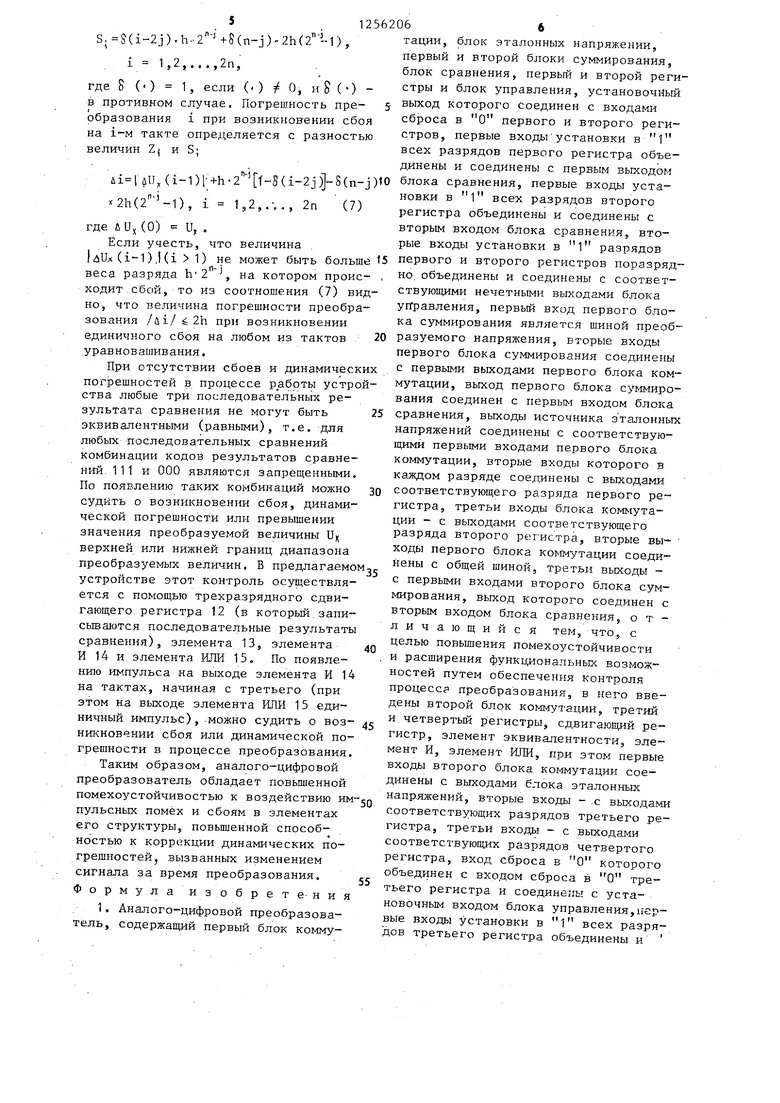

На фиг. 1 приведена функциональная схема; устройства; на фиг. 2 - функциональная схема блока управления.

Аналого-цифровой преобразователь содержит блок 1 эталонных напряжений, .блок 2 коммутации, блоки 3 и 4 суммирования, :блок 5 сравнения, регистры 6 и 7, состоящие из триггеров, блок 8 управления, регистры 9 и 10, втврой 20 блок 11 коммутации, сдвигшЬщий регистр 12, элемент 13 эквивалентности, элемент И 14, выход которого является шиной контроля, элемент ИЛИ 15. Ёлок 8 управления содержит шину 16 Запуск, генератор. 17 импульсов, элемент И 18 и сдвигающий регистр 19,

Сущность алгоритма уравновешива- ;ния преобразуемой величины, положенного в основу, предлагаемого устройст- 30 за, заключающийся в уравновешивании напряжений (токов) U и U

Uj + h и, ;

Ux + (1)

где и., t,(1)bl +cig(1) +о/„(2)Ь1 + oC(2)|2L + ....(n)U2+(n)U.

f.(i(i)(i)) ; .Ы , ..

25

ва по

на вы ни ге(

вы ни

.,

и

Т

вх 11

ци тр Ра мы ре

хо ко

35

40

и

oie(1)§2I ч-оСд(1)Ь1+ог„(2)21

+)|lT +. . .-.(n) (ЛГ)- -о1:ТГ)Ь1);

14 ° ,

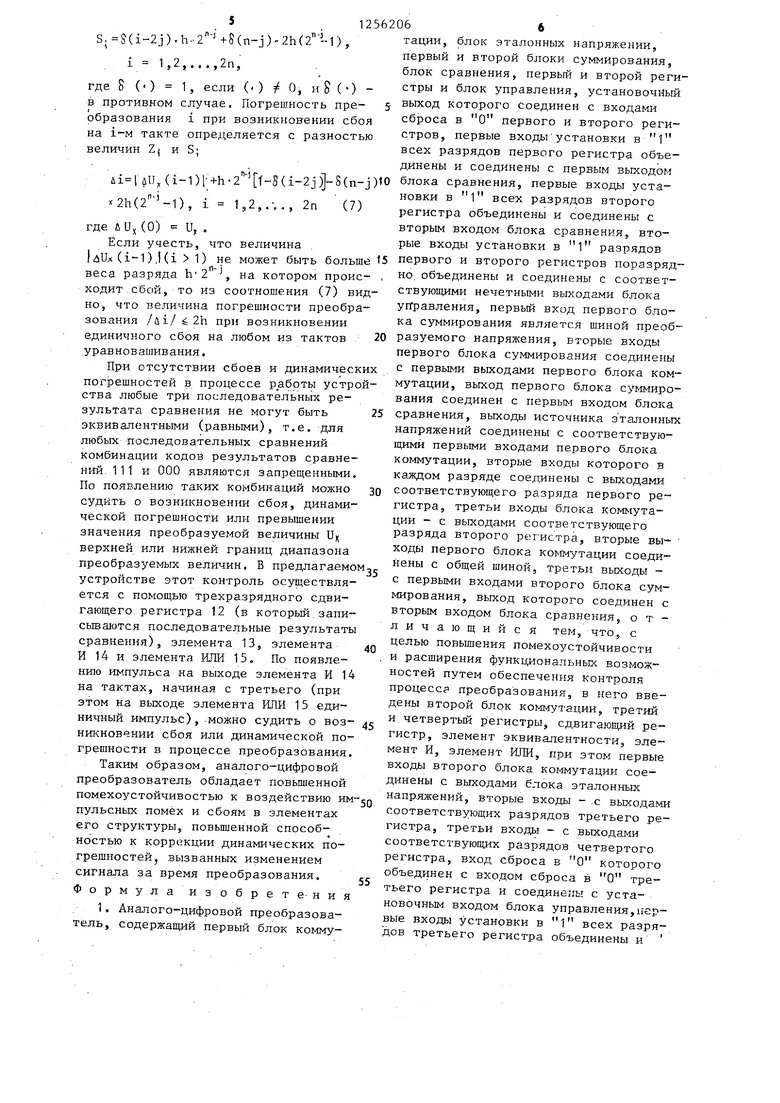

Причем разряды первого (третье)- го) 6(9) и второго (четвертого) 7(101 rtgd) о((, (i) oij (i) и Ota (i) - двоич- регистров одновременно не могут на ЧП

ходиться в единичном состоянии, так как последние определяются парафазны- мзл выходами блока 5 сравнения. Поэтому состояния выходов i-ro ключа блоков 2 и 11 коммутации для такой ком- 55 бинации входов не определены (таблица) ,

Блок 8 управления последовательно на каждом из своих выходов вырабаты-.

п разрядность регистров 6, 7, 9

ные коэффициенты, определяе- .мые состояниями i-x разрядов регистров 6 и 7 и 9 и 10 соответственно;

и,,.- величина уравновешивающего эталона, который может быть положительным или отрицательньм.

причем h 2 (h дискретность преобразования).

06

2

После окончания цикла уравновешивания сумма значений величин U, и Uj постоянна и определяется соотношением,

и, +и;

h()

(2)

На прямом выходе блока 5 сравнения на любом i-M такте уравновешивания вырабатьшается код результата сравнения У(i) 1 (на инверсном выходе ге(1) О), если Uj U, и код 96 (i) 0 (ie(i) 1) -в противном случае.

Источник 1 вырабатьшает на своих выходах следующие эталонные напряж е- ния (токи): и.

(i

.,/2, и,,/4,..,, ,

шд

1,2,3,.,.,п) подключается к

.,.,и,/2. Каждая эталонная величина

и

Т

входам i-x ключей первого 2 и второго 11 блоков коммутации.

Первьй блок 2 (второй 11) коммута- цик представляет собой набор из п трехпозиционных аналоговых ключей. Работой каждого ключа управляют прямые выходы соответствующих разрядов регистров 6, 7, 9 и 10.

В таблице показаны состояния выходов любого i-ro ключа блоков 2 и П коммутации в зависимости от состояния разрядов управлякяцих регистров.

Состояние i-x разрядов регистров

Состояние выходов i-ro ключа первого блока 2 (второго 11) коммутации

вает тактовые импульсы. Импульс по шине 16 Запуск (он же является установочным вькодом блока 8 управления) устанавливает на всех (2п+1) прямых выходах сдвигающего регистра 19 нулевые потенциалы. При этом нулевой потенциал с (2-i-1)-ro выхода сдвигающего регистра 19 разрешает прохождение импульсов с генератора 17 через элемент И 18 на вход реги- стра 19. При этом на выходах последнего с приходом каждого импульса от генератора 17 последовательно формируются тактовые импульсы.

Устройство работает следующим об- .разом.

Импульс с установочного выхода блока 8 управления () устанав лива- ет все разряды регистров 6, 7, 9 и 10 в нулевое состояние. При этом на всех вьгходах блоков 2 и 11 устанавливаются нулевые потенциалы. На выходах блоков 3 и 4 суммирования устанавливаются сигналы U Ux

и и, 0, которые сравниваются блоком 5. На прямом и инверсном выходах последнего вьфабать1 аются соответственно коды ж(0) и Эе(О) О результата сравнения, Если и, О, то эе(О) 1 («(), если и 0 9е(0) О (жТо) 1).

При поступлении первого тактового импульса с первого выхода блока 8 старшие разряды регистров 6 и 7 принимают состояния соответственноо( д( 1 )35

Соотношения (4) - (6) показывают, что для определения двоичного эквива лента и, можно использовать либо все коды N, N

коды и N

S.

о

о

N.

и Na, либо ТОЛЬКО

л I

И IL , либо только коды N

о

-9е(0) ио1;о(О Эе(0). в зависимости от состояний старших разрядов регистров 6 и 7 (таблица) эталонная величина подключается к первому 3 или второму 4 блокам. На этом такте бло- О ком 5 вырабатываются коды результата сравнения Эс(1) и Э€ (1) , значения которых определяются соотношением значений напряжений (токов) U( и U,. На втором такте с приходом тактового им-45 нескомпенсированной части преобразу- пульса с второго выхода блока 8 стар- напряжения (тока) (4U,(i-1)) шие разряды регистров 9 и 10 принимают СОСТОЯНИЯ соответственно оСд (1) . 96(1) и осТТТ) Э€(1). При этом эталонное напряжение которое пос- 5Q тупает на вход первого ключа блока 11 коммутации, в зависимости от состояний разрядов oiq (1) Иогд(1) регистров 9 и 10 подключается к первому 3

На любом i-M такте уравновешивания действие сбоя может привести к неправильному результату сравнения значений величины U ( и U и согласно алгоритму работы устройства к непра-ч вильному включению последующего веса разряда. Величина Z , равная сумме

на предыдущих тактах и веса неправильно включенного разряда, определяется выражением

, (1-1)1 ,2,...,2п,

где

1/2, если 1 кратно 2; J + 1 - в противном случае. Эта величина может быть скомпенси-

или второму 4 блокам. На этом же так-55рована только весами разрядов, еще

те формируются блоком 5 коды Эб(2)не участвовавших в уравновешивании,

иэе(2). На третьем и четвертом так-Сумма весов последних S; определяеттах в уравновешивании участвует эта-ся вьфажением

10 12562064

лонная величина U,,y4, на пятом и шестом тактах - и т.д.

По окончании цикла уравновешивания на входах блока 5 присутствуют 5 напряжения U, и U, отличающиеся друг от друга на величину, не превышающую h (если Ugr h 2)

и + п и,;

ид+ь1:()))

а

h.i ((1) +o(i)).2 (3)

или Uy +h(No ).(N 3 где Нд,Ыо, - коды, отраженные

соответственно в регистрах,6,7, 9 и 10.

Код в регистре 7(10) представляет собой обратный -код в регистре 6(9), Двоичный эквивалент U согласно.(1) может быть определен

и, и - и/ n()-().(4)

С учетом соотношения (2-) значение и может быть найдено также из вьфа- жений

и, 2h(N,+N) - () ; (5) и, 2h()-() . (6)

Соотношения (4) - (6) показывают, что для определения двоичного эквивалента и, можно использовать либо все коды N, N

коды и N

S.

о

о

N.

и Na, либо ТОЛЬКО

л I

И IL , либо только коды N

о

нескомпенсированной части преобразу- напряжения (тока) (4U,(i-1))

На любом i-M такте уравновешивания действие сбоя может привести к неправильному результату сравнения значений величины U ( и U и согласно алгоритму работы устройства к непра-ч вильному включению последующего веса разряда. Величина Z , равная сумме

нескомпенсированной части преобразу- напряжения (тока) (4U,(i-1))

на предыдущих тактах и веса неправильно включенного разряда, определяется выражением

, (1-1)1 ,2,...,2п,

нескомпенсированной части преобразу- напряжения (тока) (4U,(i-1))

где

1/2, если 1 кратно 2; J + 1 - в противном случае. Эта величина может быть скомпенси-

S.S(i-2j).h..(n-j)-2h(), i 1,22n,

где 8 () 1, если ( ) О, иП ) - в противном случае. Погрешность преобразования, i при возникнонении сбоя на i-M такте определяется с разностью величин Zj и S;

(iU,,(i-1)l4-h-2 f-S(i-2j)-S(n-j) 0 блока сравнения, первые входы уста.j новки в 1 всех разрядов второго

«2h(2 -1), 1 1,,2,.,., /п (/) регистра объединены и соединены с

вторым входом блока сравнения, втоI111t

где uUx(O) и, .

Если учесть, что величина . входы установки в 1 разрядов

ЬШ (i-1),l(i 1) не может быть больше «5первого и второго регистров поразрядвеса разряда , на котором проис- ,но. объединены и соединены с соответкодит.сбой, то из соотношения (7) вид-ствующими нечетными выходами блока

но, что величина погрешности преобра-управления, первый вход первого блозования при возникновениика суммирования является шиной преобединичного сбоя на любом из тактов 20разуемого напряжения, вторые входы

уравновашивания.первого блока суммирования соединены

При отсутствии сбоев и динамических ,с первыми выходами первого блока компогрешностей в процессе работы устрой ства любые три последовательных результата сравнения не могут быть эквивалентными (равными), т.е. для любых -последовательных сравнений комбинации кодов результатов сравне- Н1-1Й, 111 и 000 являются запрещенными. По появлению таких комбинаций можно зо судить о возникновении сбоя, динамической погрешности или превышении значения преобразуемой величины верхней или нижней границ диапазона

мутации, выход первого блока суммирования соединен с первым входом блока 25 сравнения, выходы источника з талонных напряжений соединены с соответствующими первыми входами первого блока коммутации, вторые входы которого в каждом разряде соединены с выходами соответствующего разряда первого регистра, третьи входы блока коммутации - с выходами соответствующего разряда второго регистра, вторые вы- ходы первого блока, коммутации соеди

преобразуемых величин. В предлагаемом ™ с общей шиной, третьи выходы - устройстве этот контроль осуществля- первыми входами второго блока суммирования, выход которого соединен с вторым входом блока сравнения, о т ется с помощью трехразрядного сдвигающего, регистра 12 (в который.запи сьтаются последовательные результаты сравнения), элемента 13, элемента И 14 и элемента ИЛИ 15, По появлению импульса на выходе элемента И 14 на тактах, начиная с третьего (при этом на выходе элемента ИЛИ 15 едиличающиися тем, что, с

40

целью повьшгения помехоустойчивости и расширения функциональньш возможностей путем обеспечения контроля процесс преобразования, в него введены второй блок коммутации, третий

ничный импульс),.можно судить о воз- 45 и четвертый регистры, сдвигающий ре никновении сбоя или динамической по- гистр, элемент эквивалентности, эле- грешности в процессе преобразования. элемент ИЛИ, при этом первые

Таким .образом, аналого-цифровой преобразователь обладает повьш енной

входы второго блока коммутации соединены с выходами блока эталонных

помехоустойчивостью к воздействию пряжений, вторые входы - .с выходами пульсных помех и сбоям в элементах соответствующих разрядов третьего регистра, третьи входь - с выходами соответствуюш;их разрядов четвертого

его структуры, повышенной способностью к коррекции динамических погрешностей, вызванных изменением сигнала за время преобразования.

Формула изобрете-ния

1. Аналого-цифровой преобразователь, содержащий первый блок комму55

регистра, вход сброса в О которого объединен с входом сброса в О третьего регистра и соединены с установочным входом блока управления,первые входы установки в 1 всех разрядов третьего регистра объединены и

62066

тации, блок эталонных напряжении, первый и второй блоки суммирования, блок сравнения, первый и второй регистры и блок управления, установочный 5 выход которого соединен с входами сброса в О первого и второго регистров, первые входы установки в 1 всех разрядов первого регистра объединены и соединены с первым выходом

вторым входом блока сравнения, втоI111t

входы установки в 1 разрядов

с первыми выходами первого блока ком

мутации, выход первого блока суммирования соединен с первым входом блока сравнения, выходы источника з талонных напряжений соединены с соответствующими первыми входами первого блока коммутации, вторые входы которого в каждом разряде соединены с выходами соответствующего разряда первого регистра, третьи входы блока коммутации - с выходами соответствующего разряда второго регистра, вторые вы- ходы первого блока, коммутации соеди

личающиися тем, что, с

регистра, вход сброса в О которого объединен с входом сброса в О третьего регистра и соединены с установочным входом блока управления,первые входы установки в 1 всех разрядов третьего регистра объединены и

соединены соответственно с первьм выходом блока сравнения, первые входы установки в 1 всех разрядов четвертого регистра объединены и соединены

с вторым выходом блока сравнения, а вторые входы установки в 1 третьего и четвертого регистров поразрядно объединены и соединены с соответствующими четными выходами блока управления, причем третьи входы первого блока суммирования соединены с первыми выходами вторбго блока коммутации, вторые выходы которого соединены с вторыми входами второго блока суммирования, а третьи выходы - с общей шиной, первый выход блока сравнения соединен с входом сдвигающего регистра, выходы которого соединены соответственно с входами элемента

эквивалентности, выход которого сое- 20 выхода разрядов сдвигающего регистра динен,с первым входом элемента И,вто- .являются соответственно нечетными и. рой вход которого соединен с выходом чётными выходами блока управления.f

ры

12562068

элемента ИЛИ, входы которого соединены с соответствующими выходами блока управления, выход элемента И является шиной контроля.

2, Преобразователь по п.1, отличающийся тем, что,блок управления выполнен на генераторе импульсов , элементе И, сдвигающем рег«стре, при этом прямой выход старшего разряда сдвигающего регистра соединен с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И подключен к входу синхронизации сдвигакицего регистра, причем шина Запуск является входом установки в О сдвигаищего регистра и установочным выходом блока управления, а

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1270895A1 |

| Преобразователь напряжения в код последовательного приближения | 1978 |

|

SU790290A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1462479A1 |

| Устройство для задания программы | 1979 |

|

SU862118A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Устройство для определения текущей оценки среднего значения | 1984 |

|

SU1363251A1 |

| Преобразователь напряжения в код | 1980 |

|

SU884126A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

Изобретение относится к вычислительной технике и позволяет повысить помехоустсйчивость и расширить функциональные возможности путем обеспечения контроля процесса преобразования. Это достигается тем, что в аналого-цифровой преобразователь, содержаний блок 1 эталонных напряжений, первый блок 2 коммутации, первый 3 и второй 4 блоки суммирования, блок 5 сравнения, два регистра 6 и 7 и блок 8 управления, введены регистры 9 и 10, второй блок 11 коммутации, сдвигающий регистр 12, элемент 13 эквивалентности, элемент И 14 и элемент ИЛИ 15. 1 з.п. ф-лы, 2 ил., 1 табл.

Залуск -fg

Устам

И. Шулла

фиг. 2

- I

Составитель А. Титов Техред А. Кравчук

Заказ 4836/57Тираж 816Подписное

.ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С.Черни

| Торцовое уплотнение | 1980 |

|

SU954572A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| : Проблемы создания преобразовате- лей формы информации | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| -К.: Нау- крва думка, 1980, с | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1986-09-07—Публикация

1983-06-13—Подача