Изобретение относится к автоматике и вычислительной технике и предназначено для нодачи тока в нагрузку при одном определенном сочетании логических сигналов на входах и обеспечения регулируемого потенциала на выходе для всех остальных комбинаций логических сигналов на входе. Оно может быть, в частности, использовано для выбора строки в матрице памяти ОЗУ и установления потенциала хранения для ячеек матрицы.

Известен формирователь импульсов, в котором вход соединен с эмиттером входного транзистора, база которого через резистор подключена к положительному полюсу источника питания, а коллектор соединен с базой переключающего транзистора. Коллектор переключающего тра№зистора через резистор связан с нагрузкой и эмиттером повторительного транзистора. Эмиттер переключающего транзистора соединен с базой управляющего транзистора и через резистор - с его эмиттером, с отрицательным полюсом ис-

точника питания и с нагрузкой. Коллектор управляющего транзистора связан с базой повторительного транзистора, с коллектором ускоряющего транзистора и через резистор - с положительным полюсом источника питания. Коллектор повторительного транзистора соединен с базой ускоряющего транзистора, эмиттер которого подключен к положительному полюсу источника питания ij.

Недостатком данного формирователя является относительная сложность построения и, как следствие, пониженная надежность и невысокая степень интеграции его в интегральном исполнении.

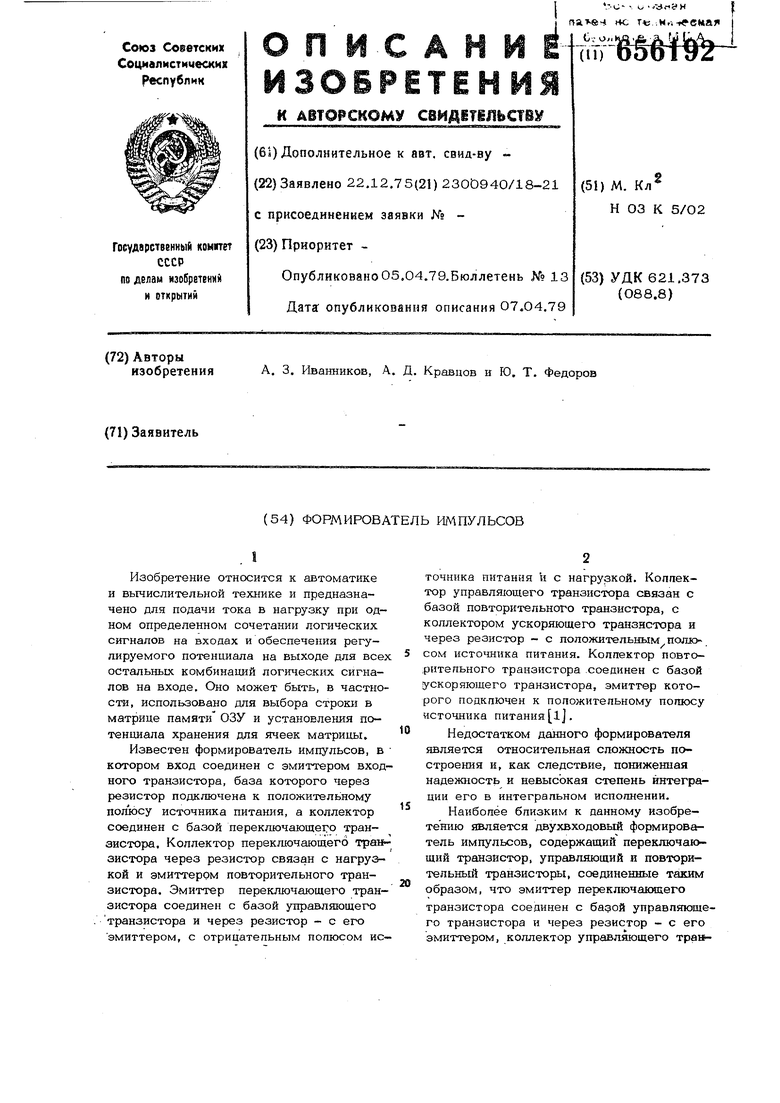

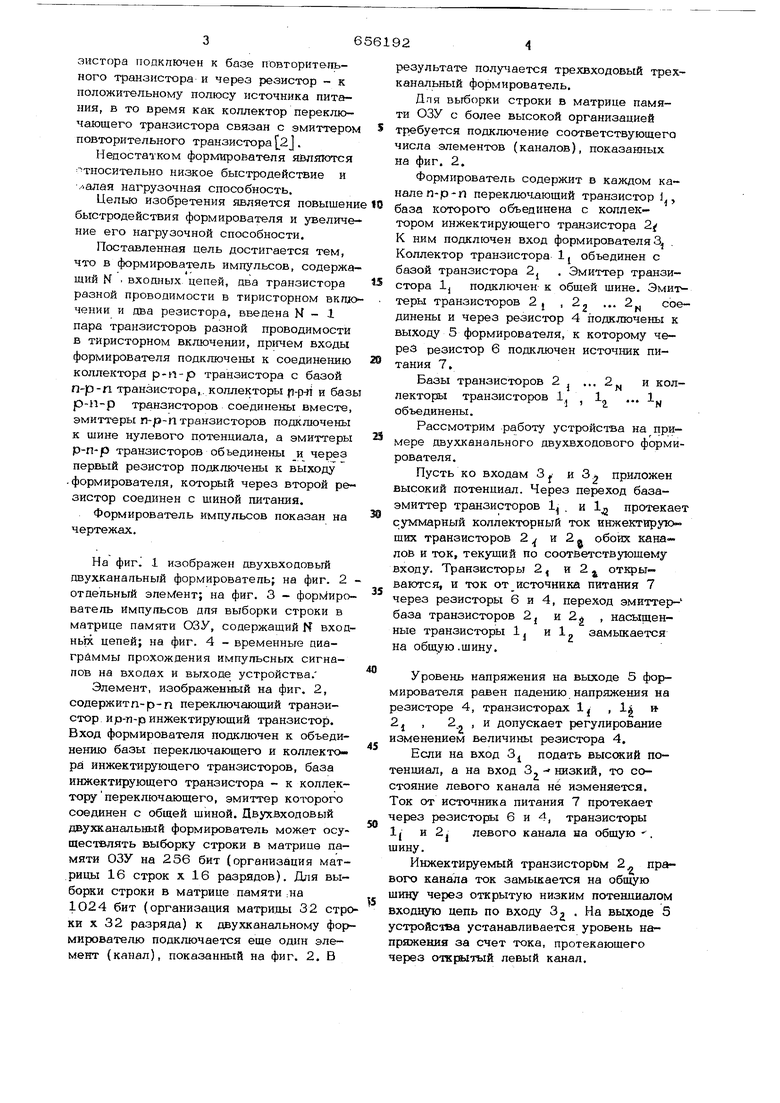

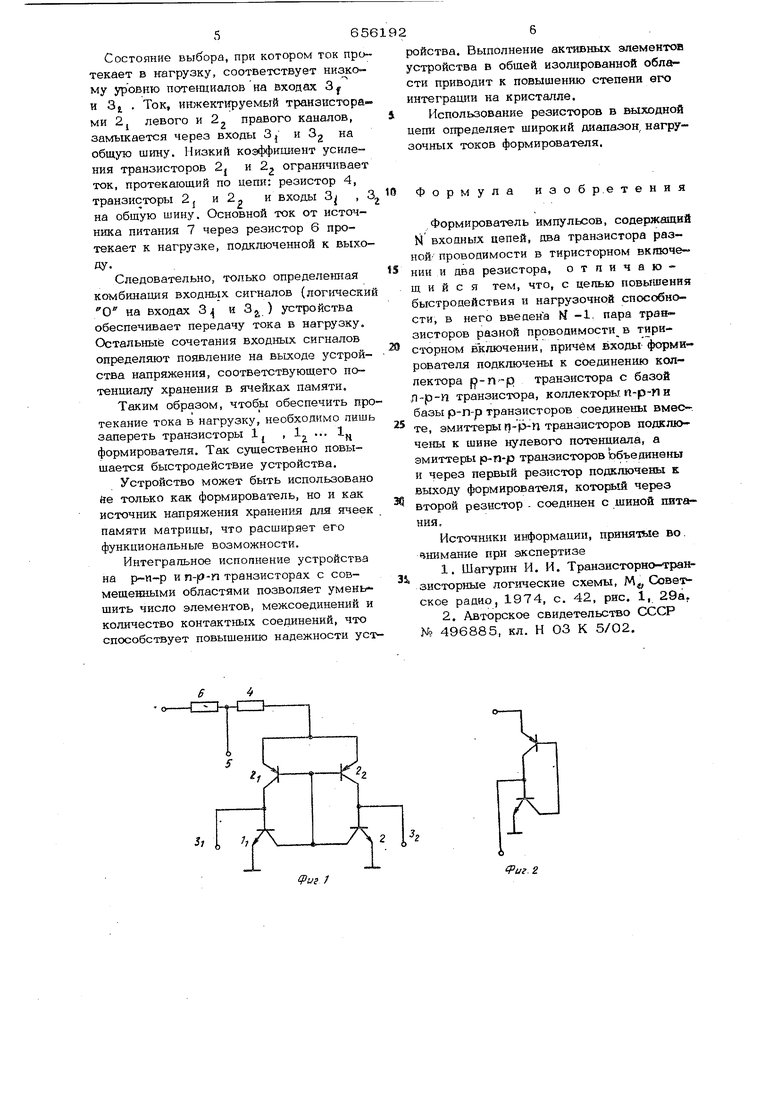

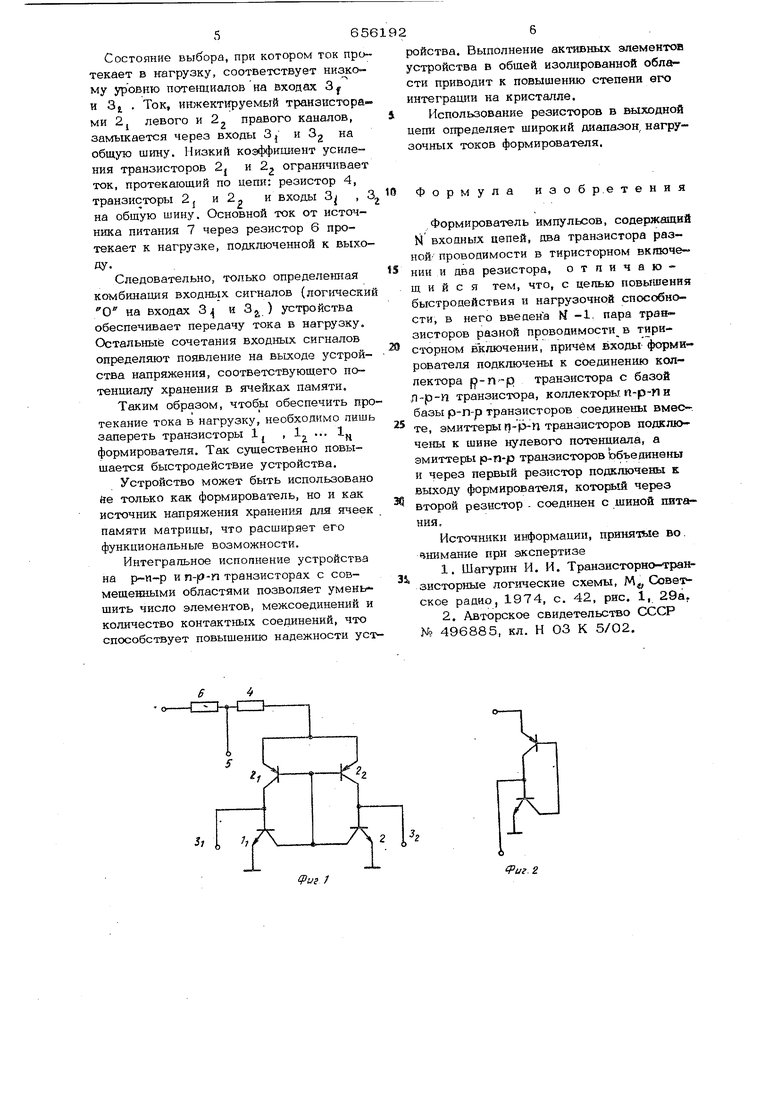

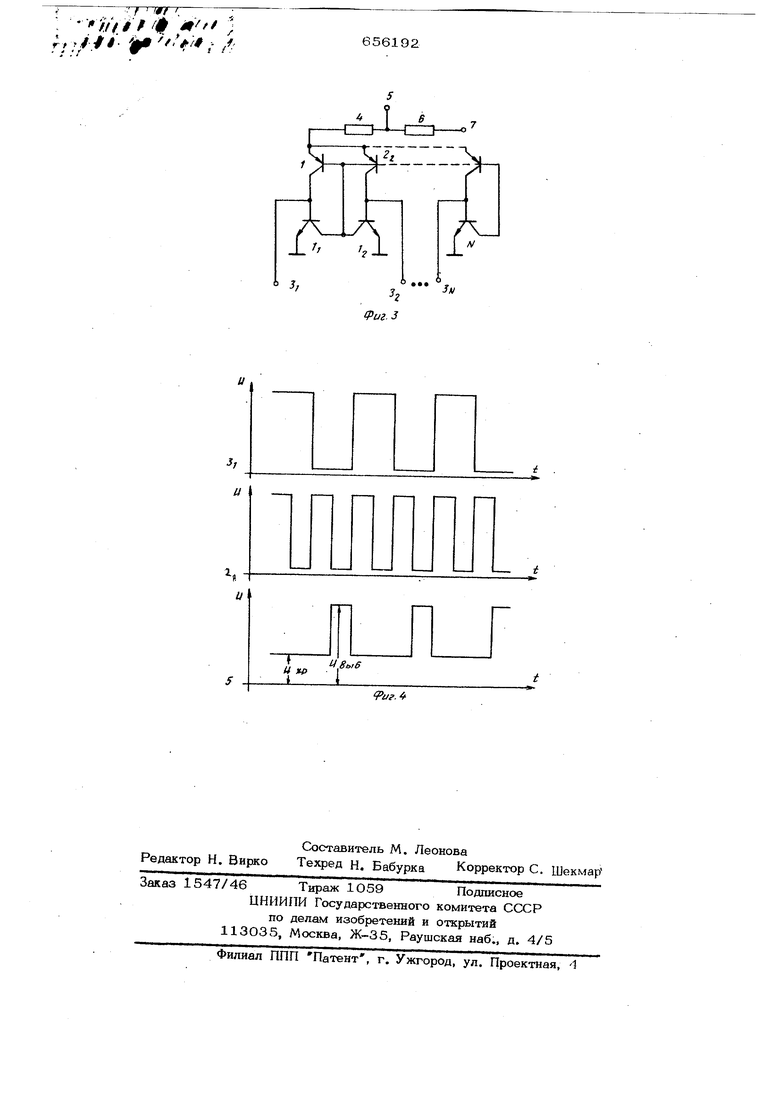

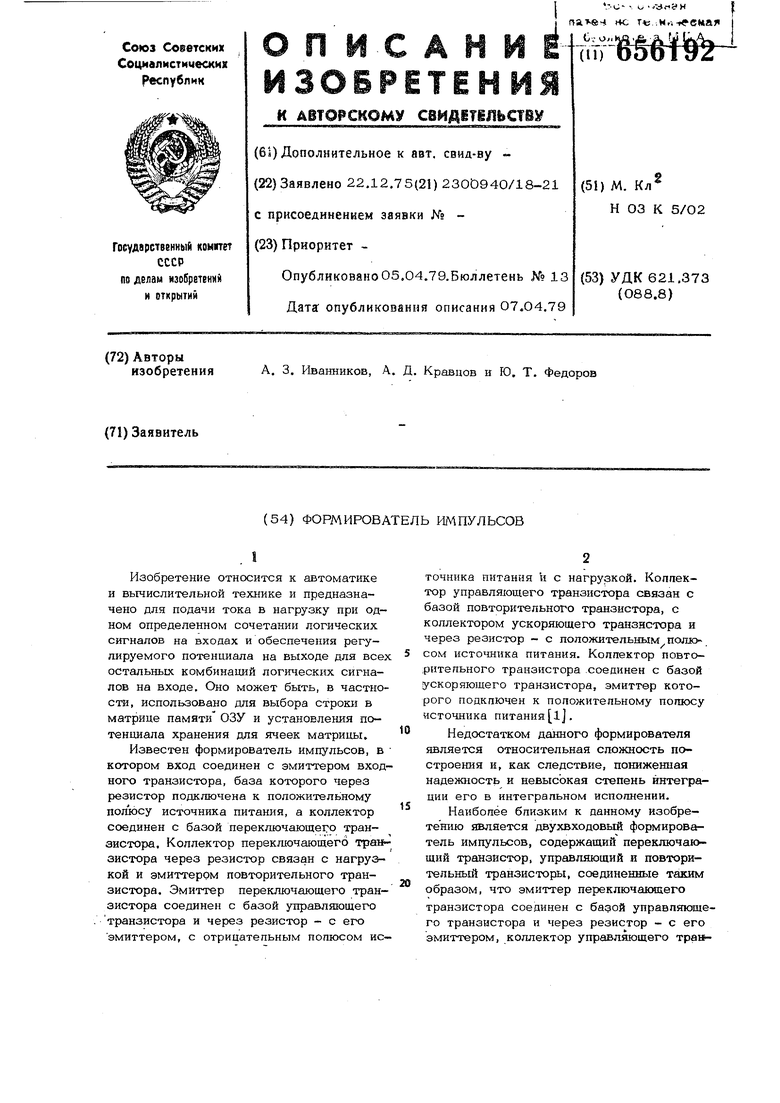

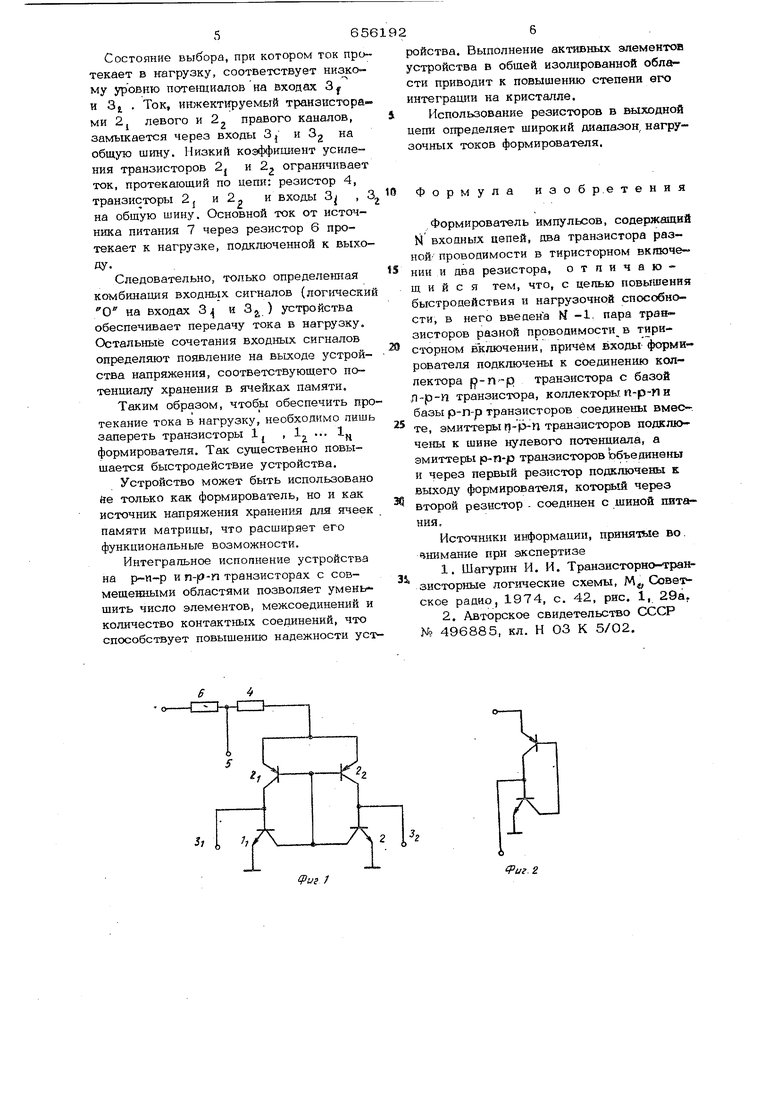

Наиболее близким к данному изобретению является двухвходовый формирователь импульсов, содержащий переключающий транзистор, управляющий и повторительный транзисторы, соединенные таким образом, что эмиттер переключающего транзистора соединен с бадой управляющего транзистора и через резистор - с его эмиттером, коллектор управляющего тра зистора подключен к базе повторитепьного транзистора и через резистор к положительному полюсу источника питания, в то время как коллектор переключающего транзистора связан с эмиттером повторительного транзистора . Недостатком формирователя являются относительно низкое быстродействие и /.алая нагрузочная способность. Целью изобретения является повышен быстродействия формирователя и увеличе ние его нагрузочной способности. Поставленная цель достигается тем, что в формирователь импульсов, содержа щий N . входных цепей, два транзистора разной проводимости в тиристорном вклю чении и два резистора, введена N - 1 пара транзисторов разной проводимости в тиристорном включении, пр1гчем входы формирователя подключены к соединению коллектора р-п-р транзистора с базой П-р-п транзистора,, коллекторы fi-p-fi и баз р-П-р транзисторов соединены вместе, эмита еры п-р-п транзисторов подключены к шине нулевого потенциала, а эмиттеры р-п-р транзисторов объединены и через первый резистор подключены к выходу -формирователя, который через второй резистор соединен с шиной питания. Формирователь импульсов показан на чертежах. На фиг 1 изображен двухвходовый двухканапьный формирователь; на фиг. 2 отдельный sneivfeHx; на фиг. 3 - формиро ватель Импульсов для выборки строки в матрице памяти ШУ, содержащий N вход ньгх цепей; на фиг. 4 - временные пиагрйммы прохождения импульсных сигналов на входах и выходе устройства. Элемент, изображенный на фиг. 2, содержитп-р-п переключающий транзистор ир-л-р инжектирующий транзистор. Вход формирователя подключен к объединению базы переключающего и коллектора инжектирующего транзисторов, база инжектирующего транзистора - к коллектору переключающего, эмиттер кочхэрого соединен с общей шиной. Пвухвходовый двухканальный формирователь может осуществлять выборку строки в матрице памяти ОЗУ на 256 бит (организация матрицы 16 строк X 16 разрядов). Для выборки строки в матрице памяти :На 1О24 бит (организация матрицы 32 стр ки х 32 разряда) к двухканальному фо1 мирователю подключается еще один элемент (канал), показаннъ1й на фиг. 2. В результате получается трехвходовый трехканальный формирователь. Дня выборки строки в матрице памяти ОЗУ с более высокой организацией т{ ебуется подключение соответствующего числа элементов (каналов), показанных на фиг. 2, Формирователь содержит в каждом канале п-р-п переключающий транзистор 1, база которого объединена с коллектором инжектирующего транзистора 2 К ним подключен вход формирователя 3 , Коллектор транзистора 1 объединен с базой транзистора 2j . Эмиттер транзистора Ij подключен к общей шине. Эмиттеры транзисторов 2 j ,22 2 соединенъ и через резистор 4 подключены к выходу 5 формирователя, к которому череЗ резистор 6 подключен источник питания 7, Базы транзисторов 2 и кол1.. лекторы транзисторов объединены. Рассмотрим работу устройства на примере двухканального двухвходового формирователя. Пусть ко входам 3 j, и 3 2 приложен высокий потенциал. Через переход базаэмиттер транзисторов 1 . и 1 протекает суммарный коллекторный ток инжектирующих транзисторов 2 и 2 обоих каналов и ток, текущий по соответствующему входу. Транзисторы 2, и 2 открываются, и ток от источника питания 7 через резисторы 6 и 4, переход эмиттербаза транзисторов 2j и 2 , насыщенные транзисторы Ij и 1„ замыкается на общую .шину. Уровень напряжения на въкоде 5 формирователя равен падению напряжения на резисторе 4, транзисторах 1j ,1 и2. , 2. , и допускает регулирование изменением величины резистора 4. Если на вход 3 подать выссжий потенциал, а на вход 3 - низкий, то состояние левого канала не изменяется. Ток от источника питания 7 протекает через резисторъ 6 и 4, транзисторы 1( и 2j левого канала на общую . щину. Инжектируемый транзистором 2 правого канала ток замыкается на общую шину через открытую низким потенциалом входную цепь по входу 3 . На выходе 5 устройства устанавливается уровень напр51жения за счет тока, протекающего через о-герытый левый канал.

Состояние выбора, при котором ток протекает в нагрузку, соответствует низкому уровню потенциалов на входах 31 и 3j, . Ток, инжектируемый транзисторами 2j левого и 2, правого каналов, замыкается через входы 3| и 32 на общую шину. Низкий коэффиш1ент усиления транзисторов 2j и 2 ограничивает ток, протекающий по цепи: резистор 4, транзисторы 2j и 2, и входы 3 , 3 на общую шину. Основной ток от источника питания 7 через резистор 6 протекает к нагрузке, подключенной к выходу.

Следовательно, только определенная комбинация входнь1х сигналов {логически О на входах 3 ;j и 3j ) устройства обеспечивает передачу тока в нагрузку. Остальные сочетания входных сигналов определяют появление на выходе устройства напряжения, соответствующего потенциалу хранения в ячейках памяти.

Таким образом, чтобы обеспечить протекание тока в нагрузку, необходимо лишь запереть транзисторы 1 ,1, ... 1 формирователя. Так существенно повыщается быстродействие устройства.

Устройство может быть использовано йе только как формирователь, но и как источник напряжения хранения для ячеек памяти матрицы, что расширяет его функциональные возможности.

Интегральное испопнение устройства на и п-р-п транзисторах с совмещенными областями позволяет умень щить число элементов, межсоединений и количество контактных соединений, что способствует повышению надежности устройства. Выполнение активных элементов устройства в общей изолированной области приводит к повышению степени его интеграции на кристалле.

Использование резисторов в выходной цепи определяет щирокий диапазон, нагрузочных токов формирователя.

Формула изоб р.е тения

Формирователь импульсов, содержащий N входных цепей, два транзистора разной- проводимости в тиристорном вкгаоче-

НИИ и два резистора, отличающийся тем, что, с цепью повышения быстродействия и нагрузочной способности, в него введена М -1, пара траа- зисторов разной проводимости в тиристорном включении, причём входы формирователя подключены к соединению коллектора р-п-р транзистора с базой Л-р-П транзистора, коллек-торы. п-р-п н базы р-п-р транзисторов соединены вмео-. те, эмиттеры п-р-п транзисторов подключены к шине нулевого потенциала, а эмиттеры fs-n-p транзисторов Ьбъединены и через первый резистор подключены к выходу формирователя, который через второй резистор - соединен с шиной питания.

Источники информации, принятые во. внимание при экспертизе

1.Шагурин И. И. Транзисторно-транзисторные логические схемы, М Совврское радио, 1974, с. 42, рис. 1, 29а.

2.Авторское свидетельство СССР № 496885, кл. Н 03 К 5/О2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Дешифратор | 1977 |

|

SU1050110A1 |

| Дешифратор | 1975 |

|

SU610298A1 |

| Накопитель для оперативного запоминающего устройства | 1990 |

|

SU1751815A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

Риг }

.2

тХГ Vf . . ,

: --Г//

;.;/.//

656192

л/

/ //

t

Авторы

Даты

1979-04-05—Публикация

1975-12-22—Подача