Изобретение относится к вычислительной технике и может быть использовано в интегральных схемах запоминающих устройств в качестве усилителя считывания.

Известен усилитель который содержит дополнительно к основным каскадам цепь разрешения считывания для уменьшения потребляемой мошности 1.

Недостатком этого усилителя является его сложность.

Наиболее близким техническим решением к изобретению является усилитель считывания, содержащий дифференциальный каскад, состоящий из первого и второго транзисторов, эмиттеры которых соединены между собой и через резистор подключены к шине нулевого потенциала, базы подключены к входам устройства, две аналогичные цепи, каждая из которых состоит из третьего транзистора, коллектор которого подключен к шине питания, а база упомянутого транзистора первой и второй цепи подключена к коллектору первого и второго транзистора дифференциального каскада соответственно, четвертого транизстора, коллектор которого соединен с базой третьего транзистора, эмиттер - с коллектором пятого транзистора, эмиттер которого подключен к общей шине, а база - к средней точке делителя напряжения, состоящего, например, из двух резисторов, который одним концом подключен к обшей шине, а другим - к точке соединения базы четвертого транзистора и разделительного элемента, например диода, второй конец которого подключен к эмиттеру третьего транзистора, кроме того, коллектор пятого транзистора второй цепи подключен к выходу устройства, а база - к коллектору пятого транзистора первой цепи 2.

Недостатком известного усилителя является то, что при работе всегда одна из двух аналогичных цепей оказывается включенной и по цепи питания потребляется мощность.

Целью изобретения является снижение потребляемой усилителем мощности без существенного усложнения его и при сохранении высокого быстродействия.

Поставленная цель достигается тем, что в усилитель считывания, содержащий переключающие транзисторы, резисторы, диоды, усилительный, управляющие и нагрузочные транзисторы, причем базы первого и второго переключающих транзисторов являются соответственно первым и вторым входа.ми устройства, выходом которого является коллектор усилительного транзистора, эмиттеры переключающих транзисторов соединены с первым выводом первого резистора, а коллекторы подключены соответственно к базе первого управляющего и коллектору первого нагрузочного транзисторов и к базе второго управляющего и коллектору второго нагрузочного транзисторов, коллекторы первого и второго управляющих транзисторов соединены с шиной питания, а эмиттеры подключены соответственно к аноду первого и к аноду второго диодов, катоды которых сое5 динены соответственно с базой первого нагрузочного транзистора и первым выводом второго резистора и с базой второго нагрузочного транзистора и первым выводом третьего резистора, второй вывод которого подключен к первому выводу четвертого резистора, базе усилительного транзистора, эмиттеру первого нагрузочного транзистора и коллектору третьего управляющего транзистора, база которого соединена с вторым выводо.м второго резистора и первым выво5 дом пятого резистора, второй вывод которого подключен к шине нулевого нотегГциала; эмиттеру третьего управляющего транзистора, второму выводу четвертого резистора и эмиттеру усилительного транзистора, коллектор которого соединен с

0 эмиттером второго нагрузочного транзистора, введены диоды с третьего по щестой, причем аноды третьего и пятого диодов соединены с вторым выводом первого резистора и щиной питания, а катоды - соответ5 ственно с анодами четвертого и шестого диодов, катоды которых подключены соответственно к базе первого и к базе второго переключающих транзисторов, при этом тип проводимости переключающих транзисторов противоположен типу проводимости уси0 лительного, управляющих и нагрузочных транзисторов.

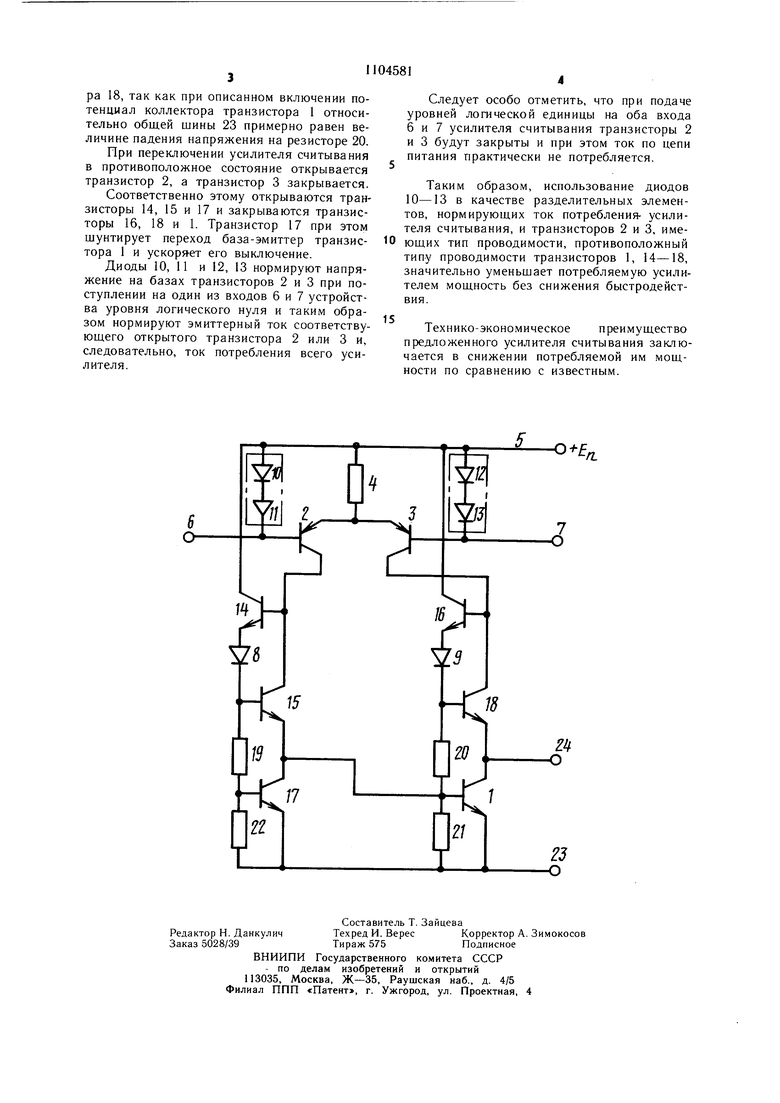

На чертеже представлена принципиальная схема предложенного усилителя считывания.

Усилитель считывания содержит усилительный транзистор 1, первый 2 и второй 3 переключающие транзисторы, первый резистор 4. На чертеже обозначены шина 5 питания, первый 6 и второй 7 входы усилителя. Усилитель содержит также диоды с первого по шестой 8-13, первый управляющий транзистор 14, первый нагрузочный транзистор 15, второй 16 и третий 17 управляюП-1ие транзисторы, второй нагрузочный транзистор 18, резисторы со второго по пятый 19-22, обплую шину 23 и выход 24.

5 Усилитель считывания работает следующим образом.

При поступлении на вход 6, например уровня логической единицы, а на вход 7 - уровня логического нуля, транзистор 2 буQ дет закрыт, а транзистор 3 - открыт. Соответственно с этим ток, протекающий в коллекторной цепи транзистора 3, вызовет открывание транзистора 16, эмиттерный ток которого, протекая по цепи, состоящей из диода 9 и резисторов 20 и 21, создает на

5 резисторе. 21 напряжение, открывающее транзистор 1, коллектор которого подключен к выходу 24. Степень насыщения транзистора I ограничивается с помощью транзисто

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Усилитель считывания | 1983 |

|

SU1132364A1 |

| Усилитель считывания | 1989 |

|

SU1658209A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Устройство для стабилизации импульсного тока нагрузки | 1986 |

|

SU1352472A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104587A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий переключающие транзисторы, резисторы, диоды, усилительный, управляющие и нагрузочные транзисторы, причем базы первого и второго переключающи.х транзисторов являются соответственно первым и вторым входами устройства, выходом которого является коллектор усилительного транзистора, эмиттеры переключающих транзисторов соединены с первым выводом первого резистора, а коллекторы подключены соответственно к базе первого управляющего и коллектору первого нагрузочного трназисторов и к базе второго управляющего и коллектору второго нагрузочного транзисторов, коллекторы первого и второго управляющих транзисторов соединены с шиной питания, а эмиттеры подключены соответственно к аноду первого и к аноду второго диодов, катоды которых соединены соответственно с базой первого нагрузочного транзистора и первым выводом второго резистора и с базой второго нагрузочного транзистора и первым выводом третьего резистора, второй вывод которого подключен к первому выводу четвертого резистора, базе усилительного транзистора, эмиттеру первого нагрузочного транзистора и коллектору третьего управляющего транзистора, база которого соединена с вторым выводом второго резистора и первым выводом пятого резистора, второй вывод которого подключен к щине нулевого потенциала, эмиттеру третьего управляющего транзистора, второму выводу четвертого резистора и эмиттеру усилительного транзистора, коллектор которого соединен с эмиттером второго нагрузочного транзистора, от® личающийся тем, что, с целью снижения потребляемой усилителем мощности, в него введены диоды с третьего по шестой, причем аноды третьего и пятого диодов соединены с вторы.м выводом первого резистора и щиной питания, а катоды - соответственно с анодами четвертого и щестого диодов, катоды которых подключены соответственно к базе первого и к базе второго переключающих транзисторов, при этом тип проводимости переключающих транзисторов противоположен типу проводимости усилительного, уп равляющих и нагрузочных транзисторов. сд 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Усилитель считывания | 1976 |

|

SU640365A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-07-23—Публикация

1983-04-29—Подача