(54) ЭЛЕМЕНТ С ТРЕМЯ СОСТОЯНИЯМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Элемент с тремя состояниями | 1982 |

|

SU1051721A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Логический элемент на мдп-транзисторах | 1977 |

|

SU664297A1 |

| Согласующее устройство на мдптранзисторах | 1976 |

|

SU708512A1 |

| Многофункциональный логический элемент | 1982 |

|

SU1016841A1 |

| Логический элемент с тремя состояниями на комплементарных МДП-транзисторах | 1988 |

|

SU1562967A1 |

| Выходное устройство с тремя состояниями на КМДП-транзисторах | 1988 |

|

SU1539994A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

Изобретение относится к вычислительной технике и электронике и может быть; использовано при создании интегральных схем на МДП-транзистора в качестве выходного ключа-усилителя для непосредственного объединения по ИЛИ с выходными каскадами других dkeM. Элемент может быть использован в устройствах вывода информации статических ЗУ и БИС-микропроцессоров. Известны элементы с тремя состояниями на дополняющих МДП-транзисторах, содержащие двухтактный выходной каскад и симметричную схему управления Ц. Недостаток этих элементов заключается в значительной потребляемой мощности. Известен элемент с тремя состояниями на дополняющих МДП-транзисторах, содержащий выkoднoй двухтактный инвертор, включенный между шиной питания и общей шиной, ключевые транзисторы п и р-типа, включенные соответственно между первым входом выходного двухтактного инвертора и общей шиной и между шиной питания И вторым входом выходного двухтактного инвертора, затворы ключевьгх транзисроров подключены к информационной шине, инвертор, включенный между шиной питания и первым, входом выходного двухтактного инвертора, вход инвертора подключен к шине управляющего сигнала, а выход - к второму входу выходного двухтактного инвертора, и двунаправленный ключ, включенный между шиной управляющего сигнала и первым входом выходного двухтактного инвертора, затворы транзисторов двунаправленного ключа р и п-типа подключены соответственно к информационной шине и к второму входу выходного двухтактного инвертора 2. Недостатком известногоэлем -нта является значительное потребление мощности и низкое быстродействие. Цель изобретения - уменьшение потребляемой мощности и увеличение быстродействия. Для достижения поставленной цели в элемент с тремя состояниями на дополняющих МДП-транзисторах, содержащий выходной двухтактный инвертор, включенный между шиной питания и общей шиной, ключевые транзисторы п и р-типа, включенные соответственно |между первым входом выходного двух725235

ТаГктного инвертора и общей шиной и ежду шиной питания и вторым входом выходного двухтактного инвертора, затворы ключевых транзисторов подключены к информационной шине, и первый инвертор, включенный между шиной питания и первым входом выходного двухтактного инвертора, вход первого инвертора подключен к шине прямого управляющего сигнала а выход - к второму входу выходного двухтактного инвертора, введен второй инвертор, включенный между выходом первого инвертора и общей шиной, вход которого подключен к шине инверсного управляющего Сигнала, а выход - к первому входу выходного двухтактного инвертора.. ,.,. , ,

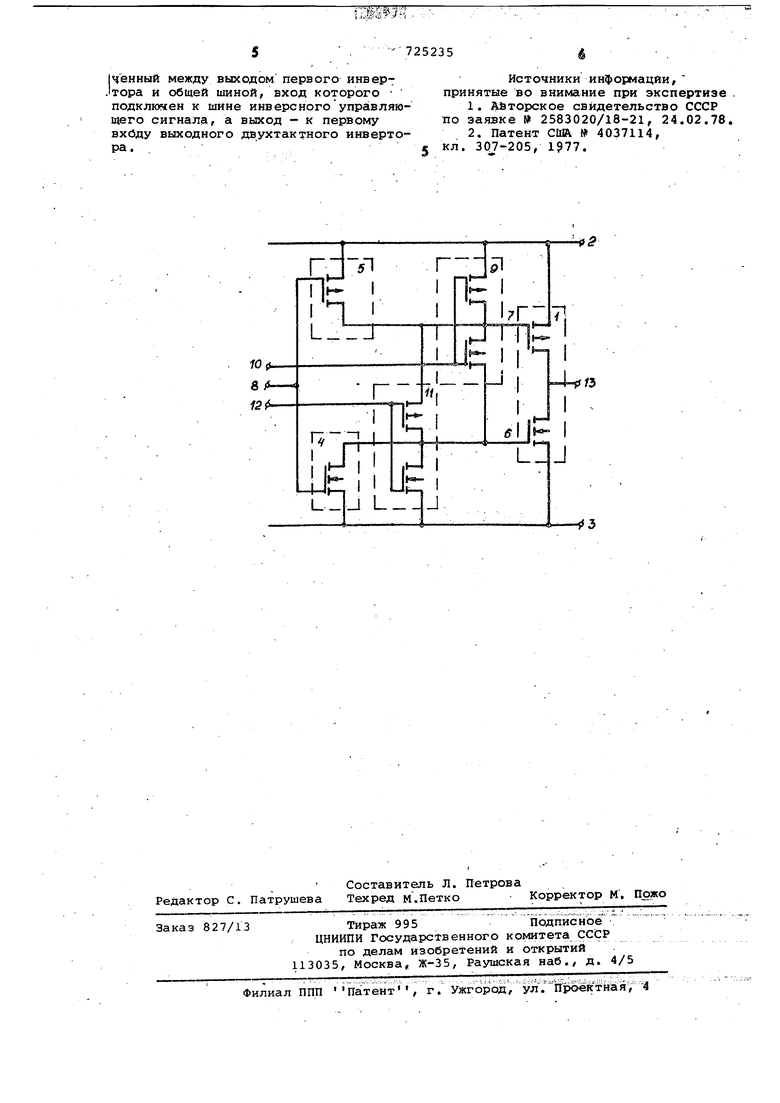

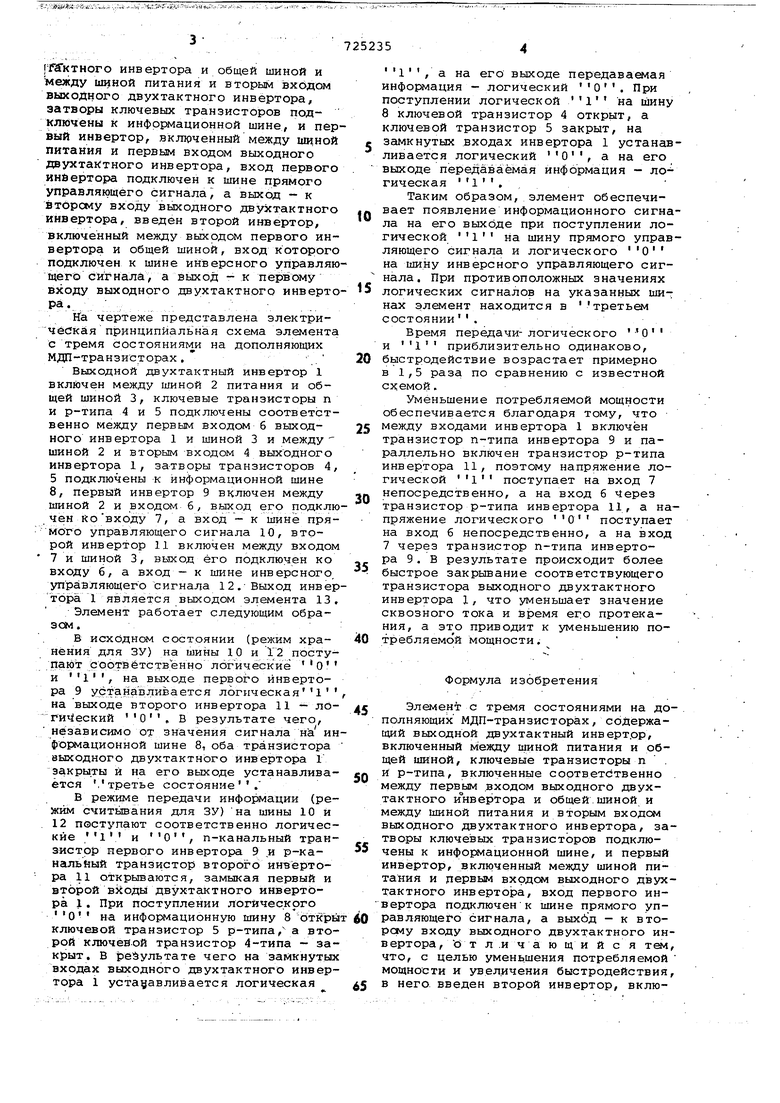

ria чертеже представлена электричёСкая принципиальная схема элемента с тремя состояниями на дополняющих МДП-транзисторах, .

Выходной двухтактный инвертор 1 включен между шиной 2 питания и общей шиной 3, ключевые транзисторы п и р-типа 4 и 5 подключены соответственно между первым входом б выходного инвертора 1 и шиной 3 и между шиной 2 и вторым входом 4 выходного инвертора 1, затворы транзисторов 4, 5 подключены к информационной шине 8, первый инвертор 9 включен между шиной 2 и входом б, выход его подключен ковходу 7, а вход - к шине прямого управляющего сигнала 10, второй инвертор 11 включен между входом 7 и шиной 3, выход его подключен ко входу 6, а вход - к шине инверсного, управляющего сигнала 12. Выход инвертора 1 является выходом элемента 13,

Элемент работает следующим образом ,

В исходном состоянии (режим хранения для ЗУ) на шины 10 и Г2 поступают соответственно логические О и , на выходе первого инвертора 9 устанавливается логическая Ч , на выходе второго инвертора 11 - лбги еский О, В результате чего, независимо от значения сигнала на информационной шине 8, оба транзистора выходного двухтактного инвертора 1 закрыты и на его выходе устанавливается .третье состояние .

В режиме передачи информации (режим считБшания для ЗУ)на шины 10 и 12 поступают соответственно логические и О, п-канальный транзистор первого инвертора 9 ,и р-канальйый транзистор второго инвертора 11 открываются, замыкая первый и второй входы двухтактного инвертора 1. При поступлении логического О на информационную шину 8 открыт ключевой транзистор 5 р-типа, а второй ключевой транзистор 4-типа - закрыт. В результате чего на замкнутых входах выходного двухтактного инвертора 1 устадавливается логическая

1 , а на его выходе передаваемая информация - логический О. При поступлении логической Ч на шину 8 ключевой транзистор 4 открыт, а ключевой транзистор 5 закрыт, на замкнутых входах инвертора 1 устанавливается логический О, а на его выходе передаваемая информация - логическая .

Таким образом, элемент обеспечивает появление информационного сигнала на его выходе при поступлении логической Ч на шину прямого управляющего сигнала и логического О на шину инверсного управляющего сигнала. При противоположных значениях логических сигналов на указанных шинах элемент находится в третьем состоянии .

Время передачи-логического -О и Ч приблизительно одинаково, быстродействие возрастает примерно в 1,5 раза по сравнению с известной

схемой.

Уменьшение потребляемой мощности обеспечивается благодаря тому, что между входами инвертора 1 включён транзистор п-типа инвертора 9 и параллельно включен транзистор р-типа инвертора 11, поэтому напряжение логической поступает на вход 7 непосредственно, а на вход 6 через транзистор р-типа инвертора 11, а напряжение логического О поступает на вход 6 непосредственно, а на вход 7 через транзистор п-типа инвертора 9 . В результате происходит более быстрое закрывание соответствующего транзистора выходного двухтактного инвертора 1, что уменьшает значение сквозного тока и время его протекания, а это приводит к уменьшению потребляемой мощности.

Формула изобретения

Элемент с тремя состояниями на дополняющих МДП-транзисторах, содержащий выходной двухтактный инверт.ор, включенный между шиной питания и общей шиной, ключевые транзисторы п и р-типа, включенные соответственно . между первым .входом выходного двухтактного инвертора и общей.шиной и между шиной питания и вторым входом выходного двухтактного инвертора, затворы ключе:вых транзисторов подключены к информационной шине, и первый инвертор, включенный между шиной питания и первым входом выходного двухтактного инвертора, вход первого инвертора подключенк шине прямого управляющего сигнала, а выхбд - к вторсму входу выходного двухтактного инвертора, От л .и ч а ю щи и с я тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия, в него введен второй инвертор, вклю1ченный между выходом первого инверг .тора и общей шиной, вход которого подключен к шине инверсного управляющего сигналаf а выход - к первому вхйду выходного двухтактного инвертора.

725235

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-03-30—Публикация

1978-10-17—Подача