1

Изобретение относится к области электроники, в частности, к импульсной технике и предназначено для применения в интегральных цифровых схемах.

Известно устройство преобразования уровней напряжения, представляющее собой обычный ключевой каскад на дополняющих МДП-транзисторах с большим отношением удельных крутизн переключающего и нагрузочного транзисторов.

Такой ключевой каскад в одном из логических состояний потребляет значительную мощность.

Известно устройство преобразования уровней напряжения, содержащее два сложных инвертора на дополняющих МДПтранзисторах, в котором истоки переключающих транзисторов первого и второго сложного инвертора подключены к шине нулевого потенциала, затворы - к прямому и инверсному входам, а стоки - к инверсному и прямому выходам схе.мы соответственно, истоки нагрузочных транзисторов первого и второго сложных инверторов подключены к шине питания, затворы - к прямому и инверсному выходам, а стоки - к инверсному и прямому выходам схемы соответственно.

Недостатком этого устройства преобразования уровней напряжения является узкая

область применения и низкое быстродействие.

Целью изобретения является расширение функциональных возможностей и повышение Оыстродействия схемы преобразования уровней напряжения.

Для этого в устройство преобразования напряжения, содерл ащее два инвертора на

МДП-транзисторах, причем исток переключающего транзистора первого инвертора подключен к шине нулевого потенциала, затвор - к входной шине, а сток - к затвору нагрузочного транзистора второго инвертора,

сток переключающего транзистора второго инвертора - с затвором нагрузочного транзистора первого инвертора и стоком нагрузочного транзистора второго инвертора, истоки нагрузочных транзисторов подключены к

шине питания, введен дополнительный нагрузочный транзистор, сток которого подключен к стоку переключающего транзистора первого инвертора, исток - к стоку нагрузочного транзистора первого инвертора, а затвор-к

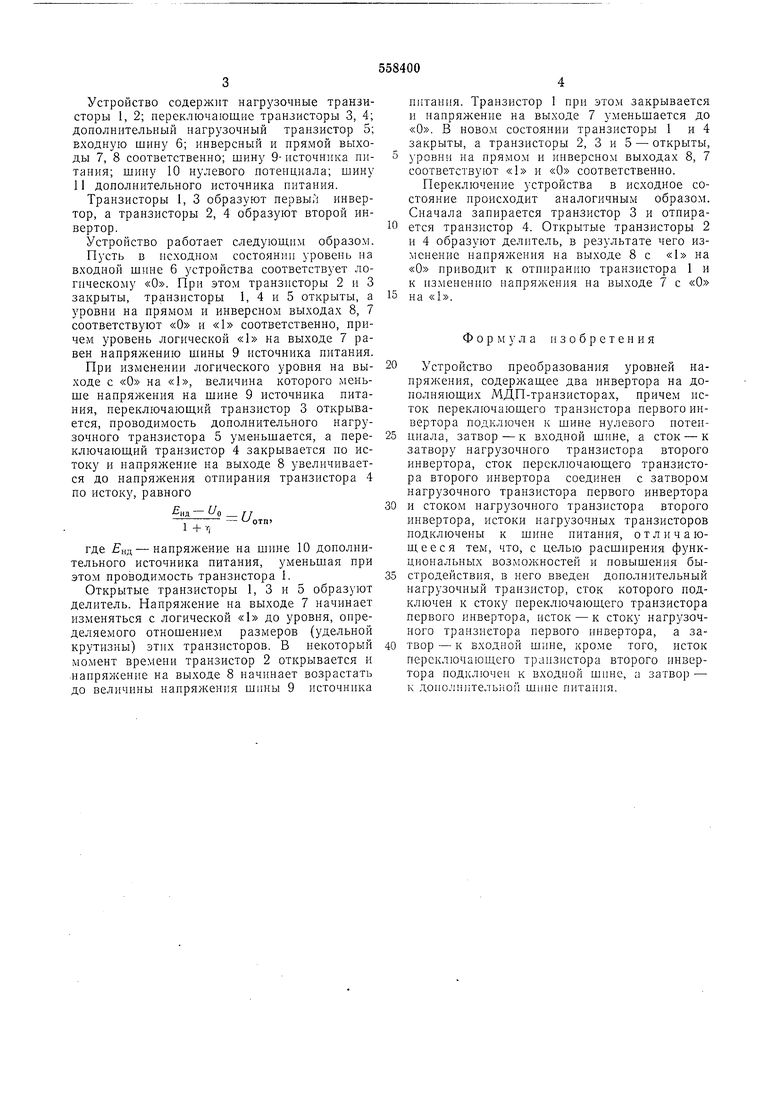

входной шине, кроме того, исток переключающего транзистора второго инвертора подключен к входной шине, а затвор - к дополнительной шине иитания. На чертел е показана принципиальная схема предлагаемого устройства.

Устройство содержит нагрузочные транзисторы 1, 2; переключающие транзисторы 3, 4; дополнительный нагрузочный транзистор 5; входную шину 6; инверсный и прялюй выходы 7, 8 соответственно; шину 9- источника питания; шину 10 нулевого потенциала; идииу 11 дополиительного источника питания.

Транзисторы 1, 3 образуют первый инвертор, а транзисторы 2, 4 образуют второй инвертор.

Устройство работает следуюш,им образом.

Пусть в исходном состоянии уровень на входной шине 6 устройства соответствует логическому «О. При этом транзисторы 2 и 3 закрыты, транзисторы 1, 4 и 5 открыты, а уровни иа прямом и инверсном выходах 8, 7 соответствуют «О и «1 соответственно, причем уровень логической «1 на выходе 7 равен напряжению шины 9 источника питания.

При изменении логического уровня на выходе с «О на «1, величина которого меньше напряжения иа шине 9 источника питания, переключаюш,ий транзистор 3 открывается, проводимость дополнительного нагрузочного транзистора 5 уменьшается, а переключаюш,ий транзистор 4 закрывается по истоку и напряжение иа выходе 8 увеличивается до напряжения отпирания транзистора 4 по истоку, равного

р и

нд О

и

1 +

где нд-напряжение на шине 10 дополнительного источника питания, уменьшая при этом проводимость транзистора 1.

Открытые транзисторы 1, 3 и 5 образуют делитель. Напряжение на выходе 7 начинает изменяться с логической «1 до уровня, определяемого отношением размеров (удельной крутизны) этих транзисторов. В некоторый момент времени транзистор 2 открывается и напряжение иа выходе 8 начииает возрастать до величины напряжения шины 9 источника

И11тания. Транзистор 1 при этом закрывается и иапрял ;еиие иа выходе 7 уменьшается до «О. В новом состоянии транзисторы 1 и 4 закрыты, а транзисторы 2, 3 и 5 - открыты,

уровни иа прямом и инверсном выходах 8, 7 соответствуют «1 и «О соответственно.

Переключение устройства в исходное состояние происходит аналогичным образом. Сначала запирается транзистор 3 и отпирается транзистор 4. Открытые транзисторы 2 и 4 образуют делитель, в результате чего измеиение напряжения на выходе 8с «1 на «О приводит к отииранию транзистора 1 и к из.менению напряжения на выходе 7 с «О

на «1.

Ф о р м л а изобретения

Устройство преобразования уровней напряжения, содержашее два инвертора на дополияюших МДП-траизисторах, причем исток переключаюи;его транзистора первого инвертора подключен к шине нулевого иотенциала, затвор - к входной шине, а сток - к затвору нагрузочного транзистора второго инвертора, сток переключаюп1его транзистора второго инвертора соедииеи с затвором нагрузочного транзистора первого инвертора

и стоком иагрузочного транзистора второго инвертора, истоки нагрузочных транзисторов подключеиы к шине питания, отличаюшееся тем, что, с целью расширения функциональных возможностей и повышения быстродействия, в него введен дополнительный нагрузочный транзистор, сток которого иодключей к стоку переключающего транзистора первого инвертора, исток - к стоку нагрузочного транзистора первого инвертора, а затвор - к входной шине, кроме того, исток переключающего транзистора второго инвертора иодключеи к входной шпие, а затвор - к доиолиительной шиие питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий преобразователь уровней напряжения на дополняющих мдп транзисторах | 1979 |

|

SU790330A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Преобразователь уровней напряжения | 1986 |

|

SU1358088A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Устройство согласования ТТЛ-элементов с МДП-элементами | 1980 |

|

SU919089A1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Источник питания | 1980 |

|

SU900376A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

Авторы

Даты

1977-05-15—Публикация

1976-02-27—Подача